| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

LUCRARE

PREZENTAREA PLATFORMEI DE LABORATOR

1. Scopul lucrarii

Lucrarea isi propune prezentarea si testarea platformei destinate laboratorului de Circuite integrate digitale, material didactic de baza utilizat nu numai in desfasurarea lucrarilor de laborator cuprinse in acest indrumar, dar si in activitatea de cercetare stiintifica in domeniu.

2. Aspecte teoretice

2.1. Descriere

Platforma de laborator este alcatuita din platforma multifunctionala si platforma de montaj echipata cu barete pentru circuite integrate.

2.1.1. Platforma multifunctionala, plansa I, este formata dintr-un ansamblu de doua placi suprapuse, interconectate electric si rigidizate din punct de vedere mecanic prin intermediul unor conectori.

Placa superioara, plansa II, reprezinta fata estetica a platformei pe care sunt grupate si inscriptionate blocurile componente ale ansamblului si pe care sunt plantati pinii de conexiune, microintrerupatoarele pentru alimentare, tastele de comanda si cei patru digiti cu 7 segmente ai blocului de afisaj.

Placa inferioara, plansa III, este cea pe care sunt plantate majoritatea componentelor electronice: circuite integrate, tranzistoare, LED-uri, rezistente, condensatoare, etc.

Platforma multifunctionala contine mai multe blocuri vizibile in plansa II si in desenul fetei estetice prezentat in fig. 1.1.

2.1.1.1. Blocul de alimentare, fig. 1.2 a si b, este format din sectiunile BA-1 si BA-2, caracterizate prin zonele aferente celor doua tensiuni de alimentare VCC1 (5V / 1A) si VCC2 (15V / 1A), precum si masei comune a intregului ansamblu.

BA-1 contine doua circuite de semnalizare echipate cu LED-uri, care indica prezenta celor doua tensiuni la intrarea in platforma, doua microintrerupatoare pentru cuplarea acestor tensiuni si o serie de pini pentru realizarea de conexiuni in caz de necesitate. BA-2 contine numai pini de conexiune.

Cele doua tensiuni de alimentare si masa comuna sunt aduse de la dulapul de alimentare dintre mesele laboratorului printr-un cablu cu 3 fire si un conector.

(a) (b)

Fig. 1.2. Blocul de alimentare

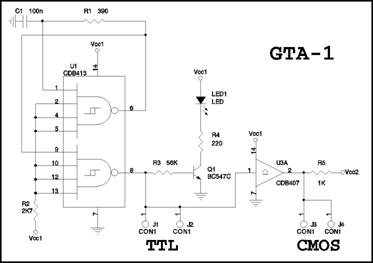

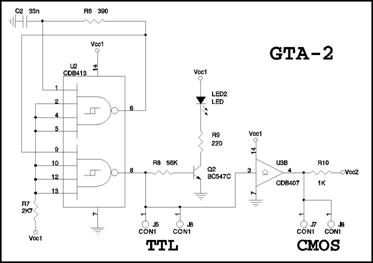

2.1.1.2. Blocul generatoarelor de tact automat, fig. 1.3, este format din sectiunile GTA-1 si GTA-2 care genereaza impulsuri de tact avand frecventele de 20kHz, respectiv 60kHz si formele de unda prezentate in fig. 1.4. Singura diferenta dintre cele doua GTA-uri consta in valoarea capacitatii (C1=100nF, in timp ce C2=33nF) care intra in formula de calcul a perioadei:

![]() , cu i=1,2.

, cu i=1,2.

(a)

(b)

Fig. 1.3. Blocul generatoarelor de tact automat

(a)

(b)

Fig. 1.4. Semnalele de iesire ale GTA1,2

Schema unui GTA este formata dintr-un generator de tensiune dreptunghiulara realizat in jurul circuitului integrat CDB413 (Anexa, fig. A6), un trigger Schmidt a carui utilizare confera fronturi foarte bune impulsurilor generate, un circuit de semnalizare echipat cu LED si un circuit de interfata TTL-CMOS, de fapt un buffer cu colectorul in gol, realizat cu 1/6 din circuitul integrat CDB407 (vezi anexa, fig. A3), cu rol de adaptor al nivelurilor de tensiune.

Pentru iesirile TTL si CMOS este prevazuta cate o pereche de pini.

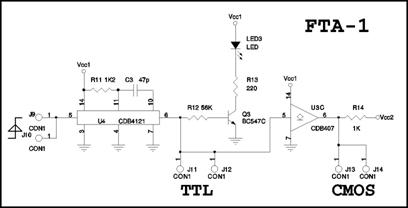

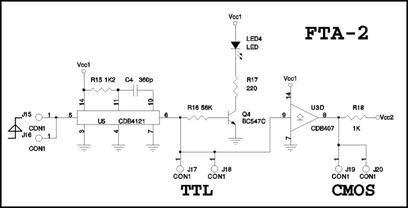

2.1.1.3. Blocul formatoarelor de tact automat, este compus din FTA-1 si FTA-2, fig. 1.5 a si b, ambele comandate pe frontul crescator al impulsurilor aplicate la intrari si generand la iesiri impulsuri cu durate standard de 40 ns, respectiv 300ns, datorita valorilor diferite ale capacitatilor C3=47pF si C4=360pF care intra in relatia de calcul a perioadei:

![]() , cu i=3,4.

, cu i=3,4.

Fiecare dintre cele doua formatoare contine cate un circuit basculant monostabil CDB4121 (Anexa, fig. A14), un circuit de semnalizare si unul de interfata TTL-CMOS.

Pentru iesirile TTL si CMOS este prevazuta cate o pereche de pini.

(a)

(b)

Fig. 1.5. Formatorul de tact automat

Fig. 1.6. Explicativa pentru functionarea FTA

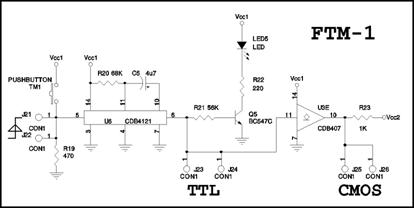

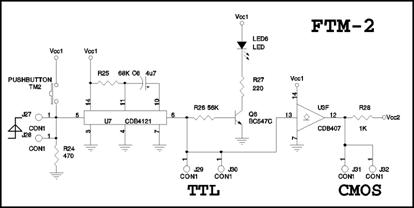

2.1.1.4. Blocul formatoarelor de tact manual, FTM-1 si FTM-2, fig. 1.7 a si b.

(a)

(b)

Fig. 1.7. Formatoarele de tact manual

Cele doua formatoare sunt identice si primesc la intrari fronturile crescatoare ale impulsurilor rezultate prin actionarea tastelor TM-1 si TM-2, generand la iesiri impulsuri cu durate standard de cca. 0,25s (v. fig. 1.8).

Fiecare dintre cele doua formatoare sunt prevazute cu cate un circuit basculant monostabil CDB4121 (Anexa, fig. A14), un circuit de semnalizare cu LED, un circuit de interfata si cate o pereche de pini pentru fiecare tip de iesire: TTL si CMOS.

(a)

(b)

Fig. 1.8. Diagramele de semnal ale formatorului de tact manual

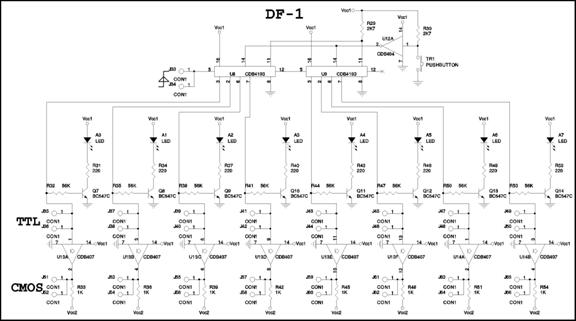

2.1.1.5. Blocul divizoarelor de frecventa, DF-1 si DF-2, fig. 1.9, comandate pe frontul crescator al impulsurilor aplicate la intrari. Divizoarele de frecventa permit numararea in binar, pe 8 biti, a impulsurilor aplicate la intrari si sunt realizate din cate doua numaratoare pe 4 biti CDB4193 (Anexa, fig. A15), conectate in cascada. Ele mai sunt prevazute cu 8 circuite de semnalizare cu LED-uri, 8 circuite de interfata si cate 8 perechi de pini pentru fiecare tip de iesire: TTL si CMOS.

Fig. 1.9. Divizorul de frecventa

0 0 1 1 1 0 1 0

TR 0 0 0 0 0 0 0 0

1 1 0 0 0 0 0 0 0

2 0 1 0 0 0 0 0 0

3 1 1 0 0 0 0 0 0

4 0 0 1 0 0 0 0 0

5 1 0 1 0 0 0 0 0

Fig. 1.10. Explicativa pentru functionarea divizorului de frecventa

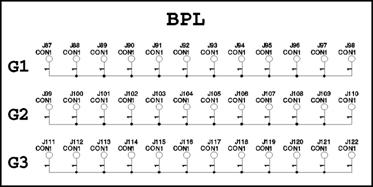

2.1.1.6. Blocul pinilor liberi (BPL), fig. 1.11, este format din 3 grupuri a cate 12 pini scurtcircuitati intre ei si avand rolul de a permite, atunci cand este cazul, multiplicarea unor contacte.

Fig. 1.11. Blocul pinilor liberi

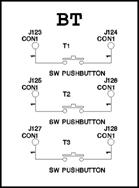

Blocul tastelor (BT), fig. 1.12, contine tastele T1, T2 si T3, disponibile prin pinii aferenti pentru utilizarea in diverse circuite.

Fig. 1.12. Blocul tastelor

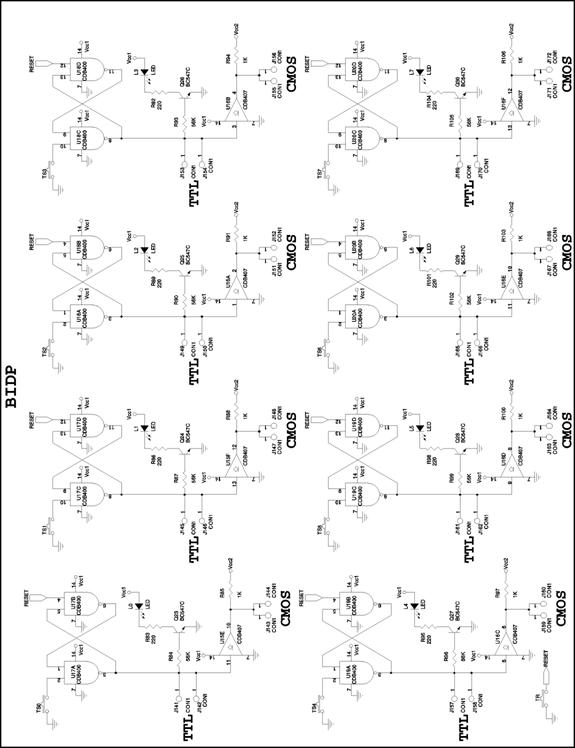

2.1.1.8. Blocul de introducere a datelor paralel (BIDP), fig. 1.13, contine 8 taste de inscriere (TS0, TS1, , TS7) si o tasta generala de stergere (TR).

Acestea actioneaza asupra unor bistabili SR realizati cu porti NAND din structura circuitului integrat CDB 400 (Anexa, fig. A1).

BIDP permite furnizarea unor cuvinte de 8 biti, vizualizabile cu ajutorul circuitelor de semnalizare echipate cu LED-uri si disponibile cu niveluri TTL si CMOS la perechile de pini special alocate.

Fig. 1.13. Blocul de introducere date paralel

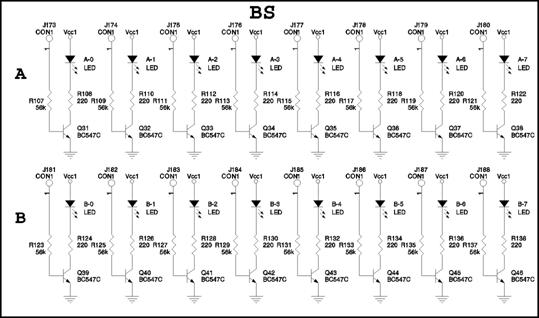

2.1.1.9. Blocul de semnalizare (BS), fig. 1.14, este format din doua sectiuni a cate 8 circuite de semnalizare echipate cu LED-uri. Pinii existenti sub fiecare dintre cele 16 LED-uri reprezinta intrarile in circuitele de semnalizare respective.

Fig. 1.14. Blocul de semnalizare

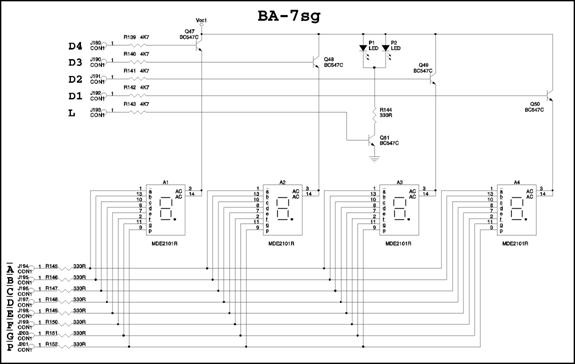

2.1.1.10. Blocul de afisaj cu 7

segmente (BA-7sg), fig. 1.15, contine 4 display-uri cu 7 segmente de tip MDE 2101R, v.

detaliul din fig. 1.16, grupate cate doua si doua LED-uri care

separa grupurile. Segmentele omoloage ale display-urilor sunt

interconectate si accesibile la pinii exteriori ![]() ,

, ![]() , iar

digitii si grupul de doua LED-uri sunt activabili prin pinii D1,

D2, L, D3 si D4.

, iar

digitii si grupul de doua LED-uri sunt activabili prin pinii D1,

D2, L, D3 si D4.

Fig. 1.15. Blocul de afisaj cu 7 segmente

Fig. 1.15. Schema blocului de afisaj cu 7 segmente

Fig. 1.16. Schema de conexiuni a unui display cu 7 segmente

2.1.2. Platforma de montaj, plansa IV, este echipata cu barete pentru circuite integrate si un mare numar de pini, conectati la aceste barete si care permit interconectarea circuitelor integrate si a altor eventuale componente. Pentru o mai usoara utilizare, a fost conceputa si o grila cu decupaje adecvate care permite numerotarea pinilor in concordanta cu aplicatia respectiva.

2.2. Functionare

2.2.1. Platforma multifunctionala

Examinarea functionarii platformei presupune examinarea functionarii tuturor blocurilor componente.

2.2.1.1. Blocul de alimentare, fig. 1.2 a si b, este format din sectiunile BA-1 si BA-2 a caror functionare o descriem in continuare.

Prezenta tensiunilor VCC1 si VCC2 in platforma multifunctionala este semnalata prin aprinderea LED-urilor 7 si 8. Tensiunea VCC1 are valoarea de 5V si este destinata alimentarii tuturor circuitelor platformei cu exceptia tranzistoarelor finale din bufferele cu colectorul in gol aflate in structura circuitelor de interfata TTL-CMOS. Acestea sunt alimentate cu tensiunea VCC2, a carei valoare poate fi reglata, in functie de aplicatie, in plaja (12 20)V. Ajustarea acestei tensiuni se poate face cu ajutorul unui semireglabil aflat in circuitul sursei de alimentare, sursa plasata in tabloul electric situat intre mese. In cazul in care se doreste o tensiune VCC2= VCC1=5V pentru alimentarea tranzistoarelor finale din buffere, aceasta se poate obtine conectand, in BA-1, iesirea intrerupatorului K1 (cuplat) cu iesirea intrerupatorului K2 (decuplat).

Observatie: Desi sursele de alimentare VCC1 si VCC2 sunt autoprotejate la scurtcircuit, nu este indicata scurtcircuitarea lor deoarece se poate distruge cablajul imprimat de pe platforma multifunctionala.

2.2.1.2. Blocul generatoarelor de tact automat (GTA1,2) furnizeaza la iesirile TTL si CMOS impulsuri dreptunghiulare de forma celor prezentate in fig. 1.4.

Datorita frecventelor mari de lucru (20 kHz, respectiv 60kHz), LED-urile de pe iesirile celor doua GTA-uri vor parea permanent aprinse, desi in realitate ele pulseaza la frecventele respective.

Circuitele de semnalizare conectate pe iesirile celor doua generatoare sunt formate din cate un tranzistor avand in baza o rezistenta de 56kΩ pentru limitarea curentului si in colector un LED inseriat cu o rezistenta de 220Ω. Cand la iesirea GTA (pinul 8 al circuitului integrat CDB413) avem 0 logic, tranzistorul este blocat si LED-ul este stins. Cand la iesirea GTA avem 1 logic (palierul superior al impulsului de tact), tranzistorul se va satura, VCEsat=0,1V≈0V si practic intreaga tensiune VCC1 se va aplica grupului LED-rezistenta. Putem scrie ca VCC1=VLED+RILED si cunoscand VCC1=5V si tensiunea de prag a LED-ului VLED≈2V, rezulta RILED≈3V. Stiind ca LED-ul lumineaza satisfacator in plaja ILED=(10 15)mA, se alege o rezistenta R=220Ω care va asigura un curent de cca.13mA.

Buffer-ul cu colectorul in gol, prezinta schema electrica din fig. 1.17 si asigura un nivel de tensiune adecvat pentru comanda circuitelor CMOS, cunoscut fiind faptul ca la 1 logic, o poarta TTL prezinta la iesire un nivel de tensiune de (2,4 5)V, in timp ce o poarta CMOS recunoaste drept 1 logic aplicat la intrare o tensiune de (3,5 5)V. Compatibilitatea TTL-CMOS este realizata de catre bufferul cu colector in gol care va asigura un nivel de tensiune foarte apropiat de 5V pentru 1 logic.

Fig. 1.17. Schema electrica a bufferului cu colectorul in gol

Intr-adevar, presupunand VCC1=VCC2=5V, daca T4 este saturat, V0=VCE4sat=0,1V≈0V si valoarea logica la iesirea bufferului va fi 0 logic.

Daca T4 este blocat, atunci prin Rext nu circula curent, caderea de tensiune de pe Rext, RextIc4≈0 si deoarece V0=VCC1- RextIc4, rezulta V0=VCC1=5V, deci 1 logic.

2.2.1.3. Blocul formatoarelor de tact automat furnizeaza la iesirile FTA-1 si FTA-2 impulsuri cu durate de 40ns, respectiv 300ns, atunci cand la intrari se aplica fronturi crescatoare ale unor impulsuri.

Daca, spre exemplu, atacam intrarea FTA-1 cu impulsurile furnizate de catre GTA-1, a caror perioada este de cca. 50µs, impulsul generat la iesirea lui FTA-1 va reprezenta cca. 1/1000 din perioada impulsului de la intrare si va aparea numai la salturile pozitive ale acestuia, vezi fig. 1.6. Ca urmare, LED-ul din circuitul de semnalizare se va aprinde numai cca. 1/1000 dintr-o perioada, fapt absolut neobservabil.

2.2.1.4. Blocul formatoarelor de tact manual

Circuitele basculante monostabile din structura FTM-1,2 sunt circuite basculante cu o singura stare stabila, in cazul nostru - 0 logic, stare din care pot fi scoase sub actiunea unui stimul (salt pozitiv) aplicat la intrare.

Daca tasta TM-1(2) este neactionata, intrarea 5 a circuitului integrat CDB4121 este conectata la masa prin rezistenta R19 (R24), deci V5=0V, fig. 1.8a.Ca urmare, iesirea 6 a circuitului integrat CDB4121 se va afla in starea stabila, deci V6=0V (0 logic), fig. 1.8b.

In momentul in care se actioneaza tasta TM-1(2), la intrarea 5 a circuitului integrat se produce saltul de la 0V la +5V, deci un salt 0→1, v. fig. 1.8a. Acest salt scoate din stabilitate monostabilul si-l trimite in starea instabila (1 logic) unde va ramane un interval de timp T=0,7RC, v. fig. 1.8b, dupa care revine in 0 logic.

Prin urmare, cele doua formatoare de tact manual, FTM-1 si FTM-2, genereaza la iesiri impulsuri cu o durata standard de 0,25s (v. fig. 1.8), atunci cand la intrari li se aplica impulsuri de durate diferite (operatorul uman nu poate genera prin apasarea unei taste impulsuri de aceeasi durata), dar de regula mai mici de 0,25s.

Mai mult decat atat, din cauza imperfectiunilor tastelor, saltul pozitiv care apare in momentul apasarii tastei este de fapt o suita de oscilatii 0→1 si 1→0 care in final se stabilizeaza la valoarea 1 logic. Daca am conecta tasta TM-1(2) direct la intrarea unui numarator, am constata ca, de exemplu, la o singura apasare pe tasta numaratorul va numara mai multe impulsuri, deci nu va numara corect.

Prin urmare, rolul circuitului basculant monostabil CDB4121 este nu numai acela de a transforma un impuls de durata variabila intr-unul de durata standard, ci si acela de a elimina influenta oscilatiilor generate de imperfectiunea tastelor.

2.2.1.5. Blocul divizoarelor de frecventa

Fiecare divizor de frecventa DF-1(2) contine cate doua divizoare de frecventa de cate 4 biti, fiecare dintre acestea fiind format din cate 4 circuite basculante bistabile conectate in cascada, v. fig. 1.10.

Circuitele basculante bistabile sunt simetrice ca schema, dar asimetrice ca viteza de raspuns, din cauza unor considerente legate de tehnologia de fabricatie. Ca urmare, in momentul cuplarii tensiunii de alimentare, cele 8 circuite basculante bistabile se fixeaza in stari logice imprevizibile, fapt accentuat si de modul de legare in cascada a acestora.

Presupunand ca dupa cuplarea tensiunii de alimentare starile celor 8 bistabile ar compune o combinatie binara care ar avea echivalentul zecimal 92 (v. fig. 1.10), numararea impulsurilor care se vor aplica la intrare ar incepe de la aceasta cifra iar rezultatul numararii va fi eronat.

Apare, prin urmare, necesitatea resetarii celor 8 bistabile, adica a aducerii starilor/iesirilor lor in 0 logic. Acest lucru se realizeaza cu ajutorul tastei TR-1(2), fig. 1.9.

Astfel, in momentul cuplarii tensiunii de alimentare, la intrarea inversorului U12A vom avea 1 logic (adus de la VCC1, prin rezistenta R30(R56)), iar la iesirea acestuia, deci la pinii 14 (clear) ai circuitului integrat CDB4193 vom avea 0 logic si aducerea la zero a bistabilelor nu se produce.

Actionarea tastei TR-1 va aduce un 0 logic la intrarea inversorului U12A, deci 1 logic la iesirea acestuia si pe pinii 14 (clear) ai circuitului integrat CDB4193. Pe acesti pini se inregistreaza, prin urmare, un salt pozitiv 0→1 care produce resetarea celor 8 bistabile (v. fig. 1.10, linia "TR").

Primul impuls aplicat la intrarea lantului de 8 bistabile va actiona asupra lui CBB-1 a carui stare/iesire va trece in 1 logic. Saltul 0→1 produs la iesirea lui CBB-1 si, prin urmare, la intrarea lui CBB-2, nu va influenta starea acestuia deoarece intrarea sa este sensibila numai la salturi negative (1→0). Prin urmare, iesirea lui CBB-2 va ramane in 0 logic si nu-l va influenta pe CBB-3, s.a.m.d. Numarul binar obtinut (v. fig. 1.10, linia "1") va fi 00000001, deci numararea primului impuls s-a desfasurat in mod corect.

Aplicarea celui de-al doilea impuls va schimba din nou starea/iesirea lui CBB-1 (tranzitie 1→0) si va afecta si starea/iesirea lui CBB-2 care va bascula in 1 logic (0→1). CBB-3 ramane in continuare insensibil deoarece isi schimba starea numai la salturi negative (1→0) aplicate la intrare, s.a.m.d. Numarul binar obtinut (v. fig. 1.10, linia "2") va fi 00000010, adica 2 in zecimal, deci numararea a fost corecta. S.a.m.d.

Este evident ca circuitul se comporta corect ca numarator.

Comparand formele de unda de la intrarea si iesirea lui CBB-2, constatam ca perioada T a impulsurilor de la iesire este dublul celei de la intrare, deci frecventa semnalului de la iesire este ½ din cea a semnalului aplicat la intrare.

Concluzionam ca un circuit basculant bistabil (CBB) divide prin 2 frecventa semnalului aplicat la intrare.

Prin urmare, daca la intrarea lui CBB-1, fig. 1.10, aplicam un semnal cu frecventa de 20kHz, la iesirea lui CBB-1 vom obtine 10kHz, la cea a lui CBB-2 - 5kHz, s.a.m.d.

Este clar ca circuitul se comporta ca un divizor (prin 2) de frecventa, deci DF-1,2 pot fi numite, la fel de corect, numaratoare de impulsuri sau divizoare (prin 2) de frecventa.

2.2.1.6. Blocul pinilor liberi permite, asa cum am mai spus, multiplicarea unor contacte. De exemplu, daca dorim sa trimitem in 11 directii diferite semnalul de la iesirea lui FTM-1, conectam iesirea acestuia la una din "insulele" G1, G2 sau G3 si de acolo putem pleca cu cate un conductor in cele 11 directii.

2.2.1.7. Blocul tastelor contine 3 taste disponibile pentru utilizarea in diverse circuite. Practic, apasarea uneia dintre taste creeaza scurt-circuit intre pinii aferenti si realizeaza comenzile dorite.

Blocul de introducere a datelor paralel este format, in principal, din 8 CBB-uri SR asincrone realizate cu NAND-uri. NAND-urile din stanga pot primi potentialul masei la una dintre intrari prin cate o tasta de SET, TSi, cu i=1, 2, , 7, iar cele din dreapta pot primi potentialul masei de la o aceeasi tasta de RESET, TR, comuna.

Actionarea uneia dintre tastele TSi inscrie un 1 logic in CBB-ul corespunzator, in timp ce actionarea tastei generale TR aduce in 0 logic toate cele 8 bistabile.

Poate fi astfel formata orice combinatie logica pe 8 biti (octet) cu scopul de a testa diverse circuite integrate cum ar fi registrele paralel (tampon), memoriile RAM, etc.

2.2.1.9. Blocul de semnalizare contine 16 circuite de semnalizare independente a caror functionare a fost prezentata in § 2.2.1.2.

2.2.1.10.

Blocul de afisaj cu 7 segmente este format din 4 display-uri cu 7

segmente si punct (virgula), in conexiune anod comun. Anozii celor 4

display-uri si ai celor doua LED-uri care formeaza punctele

dintre cele 2 perechi de display-uri, sunt activabili cu 1 logic aplicat

intrarilor Di, cu i=1, 2, 3, 4, respectiv L. Tranzistoarele

corespunzatoare, in montaj repetor, repeta la iesire (in emiter)

nivelurile de tensiune aplicate in baze si asigura in acest fel

tensiunea anodica a fiecarui display. Barele ![]()

![]()

![]() sunt active in 0 logic, deci segmentele corespunzatoare vor fi

activate numai la aplicarea unui 0 logic pe aceste bare.

sunt active in 0 logic, deci segmentele corespunzatoare vor fi

activate numai la aplicarea unui 0 logic pe aceste bare.

Pentru

exemplificare, daca dorim activarea segmentului ![]() din display-ul A1, trebuie sa

conectam

din display-ul A1, trebuie sa

conectam ![]() la masa (pregatind in acest fel

aprinderea tuturor segmentelor

la masa (pregatind in acest fel

aprinderea tuturor segmentelor ![]() din cele 4 display-uri) si sa

trimitem 1 logic numai pe intrarea D1, corespunzatoare

digitului A1.

din cele 4 display-uri) si sa

trimitem 1 logic numai pe intrarea D1, corespunzatoare

digitului A1.

2.2.2. Platforma de montaj

Dupa confectionarea grilei adecvate pentru circuitele integrate utilizate in montajul experimental, se realizeaza conexiunile dintre bornele de alimentare si de masa din platforma multifunctionala si platforma de montaj. Pot fi utilizati in acest scop pinii si traseele corespunzatoare care trec printre baretele in care se introduc circuitele integrate.

3. Desfasurarea lucrarii

3.1. Testarea platformei multifunctionale

3.1.1. Blocul de alimentare

a) Se verifica starea "deschis" a intrerupatoarelor K1 si K2 din BA-1;

b) Se introduce conectorul platformei multifunctionale in perechea sa de pe partea laterala a tabloului electric dintre mese;

c) Se cupleaza, in tabloul electric, cheia comutatoare aferenta mesei de lucru;

d) LED-urile 7 si 8 se vor aprinde, indicand prezenta tensiunilor VCC1, VCC2 siu a masei in platforma, dar numai inainte de K1 si K2, v. fig. 1.2;

e) Se masoara cu un voltmetru tensiunile VCC1 si VCC2 fata de masa;

f) Se cupleaza intrerupatorul K1, trimitandu-se tensiunea VCC1 in toata platforma multifunctionala, mai putin in colectorii tranzistoarelor din bufferele cu colector in gol;

g) Se remarca aprinderea unora dintre LED-urile din circuitele de semnalizare ale blocurilor DF-1, DF-2 si BIDP, precum si a celor GTA-1 si GTA-2;

h) Se reseteaza DF-1, DF-2 si BIDP, singurele LED-uri de pe platforma care mai raman aprinse fiind cele din BA-1 si cele din GTA-1 si GTA-2. Motivul pentru care acestea din urma raman aprinse a fost discutat anterior;

i) Cu K1 cuplat (inchis) si K2 decuplat (deschis), se face o punte intre iesirile lui K1 si K2, trimitand astfel VCC1 si la colectorii tranzistoarelor din bufferele cu colector in gol.

3.1.2. Blocul generatoarelor de tact automat

a) Conectand un osciloscop cu doua canale intre iesirile TTL, respectiv CMOS ale GTA-1 si masa, se vizualizeaza formele de unda din fig. 1.4;

b) Se determina perioada T a oscilatiilor GTA-1, facand produsul dintre numarul de diviziuni pe care se intinde T si timpul/diviziune afisat de osciloscop;

c) Se determina frecventa f a oscilatiilor cu relatia ![]() si se verifica faptul ca aceasta se

apropie ca valoare de 20 kHz;

si se verifica faptul ca aceasta se

apropie ca valoare de 20 kHz;

d) Se determina amplitudinea ATTL a oscilatiilor, facand produsul dintre numarul de diviziuni pe verticala si scala de tensiune afisata de osciloscop;

e) Se determina amplitudinea ACMOS a oscilatiilor in aceeasi maniera ca la punctul (d);

f) Se repeta experimentele de la punctele (a) (e) pentru GTA-2.

3.1.3. Blocul formatoarelor de tact automat

a) Se cupleaza iesirea TTL a GTA-1 la intrarea FTA-1 cu ajutorul unei singure conexiuni.

Amintim faptul ca un astfel de cuplaj ar necesita in mod normal doua conexiuni (firul cald si masa), dar deoarece platforma multifunctionala are masa comuna pentru toate circuitele, este suficienta o singura conexiune (firul cald).

b) Se conecteaza sonda corespunzatoare canalului 1 al osciloscopului la intrarea FTA-1 si cea de-a doua sonda - la iesirea TTL a aceluiasi circuit. Se vizualizeaza formele de unda din fig. 1.6;

c) Mutand cea de-a doua sonda la iesirea CMOS a lui FTA-1 se vizualizeaza formele de unda si se compara cu cele obtinute la punctul (b);

3.1.4. Blocul formatoarelor de tact manual

a) Fara a face nici o conexiune suplimentara, se apasa TM-1 si se constata ca LED-ul din circuitul de semnalizare de la iesirea FTM-1 ramane aprins un interval de timp mai mare decat cel in care tasta a fost apasata. Se justifica in acest mod diagramele din fig. 1.8;

b) Se repeta experimentul de la punctul (a) pentru FTM-2.

3.1.5. Blocul divizoarelor de frecventa

a) Se conecteaza iesirea TTL a FTM-1 la intrarea DF-1;

b) Se reseteaza DF-1 actionand TR-1;

c) Apasand repetat tasta TM-1 se verifica, cu ajutorul circuitelor de semnalizare echipate cu LED-uri, faptul ca DF-1 numara corect;

d) Se conecteaza intrarea lui DF-1 la intrarea lui FTM-1, adica se conecteaza tasta TM-1 direct la intrarea lui DF-1;

e) Se apasa in mod repetat tasta TM-1 si se verifica faptul ca DF-1 numara incorect din cauza impulsurilor parazite introduse de tasta;

f) Se conecteaza iesirea TTL a lui GTA-1 la intrarea lui DF-1;

g) Se reseteaza DF-1;

h) Se constata ca toate cele 8 LED-uri din circuitele de semnalizare ale lui DF-1 sunt permanent aprinse. In realitate, ele pulseaza cu o frecventa foarte mare si ochiul le percepe ca fiind permanent aprinse;

i) Se pune sonda corespunzatoare canalului 1 al osciloscopului pe pinul de intrare in primul bistabil din structura DF-1, iar sonda cealalta pe pinul A1 de la intrarea in cel de-al doilea bistabil. Se observa perioada dubla a impulsurilor de la iesirea bistabilului, deci frecventa pe jumatate fata de cea a impulsurilor aplicate la intrare.

j) Se repeta experimentul de la punctul (i) pentru iesirile CMOS si se evidentiaza diferentele care apar;

k) Cu GTA-1 cuplat la intrarea lui DF-1, se cupleaza in cascada cu DF-1 divizorul de frecventa DF-2 (iesirea TTL A7 a lui DF-1 cu intrarea lui DF-2). Se realizeaza un numarator pe 16 biti , la care ultimii 7 biti pulseaza cu o frecventa din ce in ce mai mica pe masura ce ne deplasam de la B1 catre B7.

Operatiunile de numarare si divizare de frecventa sunt acum evidente.

3.1.6. Blocul pinilor liberi

a) Se aduce succesiv VCC1 in cate una din zonele G1, G2 si G3 si se verifica cu unul dintre circuitele de semnalizare ale lui BS existenta lui 1 logic pe fiecare dintre cei 12 pini ai fiecarei zone;

3.1.7. Blocul tastelor

a) Se conecteaza succesiv una din bornele tastelor Ti, cu i=1, 2, 3, la VCC1, iar cealalta borna se conecteaza la unul din cele 16 circuite de semnalizare din BS;3

b) Se apasa tasta Ti si se verifica aprinderea LED-ului din circuitul de semnalizare respectiv.

3.1.8. Blocul de introducere a datelor paralel

a) Se apasa tasta de RESET, TR, astfel incat toti cei 8 bistabili ai blocului sa fie pusi pe zero;

b) Se apasa tastele TSi si se obtine configuratia binara dorita pe octetul din BIDP, vizualizata pe cele 8 LED-uri;

c) Se reseteaza bistabilii prin actionarea tastei TR.

3.1.9. Blocul de semnaliuzare

a) Se conecteaza un fir de conexiune la VCC1 (1 logic) si se ating cu extremitatea cealalta a firului pinii de intrare ai celor 16 circuite de semnalizare. Se constata aprinderea succesiva a celor 16 LED-uri;

b) Cu firul de conexiune conectat la masa (0 logic) se repeta experimentul de la punctul (a). Se constata ca toate LED-urile raman stinse.

3.1.10. Blocul de afisaj cu 7 segmente

(a) Se conecteaza in ordine pinii ![]() ,

, ![]() , ,

, , ![]() , la iesirile TTL ale BIDP, de la rangul 20

la rangul 27;

, la iesirile TTL ale BIDP, de la rangul 20

la rangul 27;

(b) Se conecteaza pinii D1, , D4, la iesirile B0, , B3 ale DF-2, cu intrarea lui DF-2 cuplata la iesirea TTL a lui FTM-2;

(c) Se actioneaza succesiv TM-2 si se constata vizualizarea pe display-urile cu 7 segmente a tuturor segmentelor si punctelor;

(d) Se actioneaza succesiv TS0,

, TS7 si se constata dezactivarea succesiva a

segmentelor ![]() ,

, ![]() , ,

, , ![]() si in final a

punctelor

si in final a

punctelor ![]() ;

;

(e) Se reseteaza BIDP prin actionarea tastei TR si se constata reaprinderea pe cele 4 display-uri a tuturor segmentelor si a punctelor.

3.2. Testarea platformei de montaj

Se verifica cu ajutorul unui ohmmetrutoate legaturile dintre pinii si baretele instalate pe platforma

4. Continutul referatului

4.1. Schemele GTA, fig. 1.3;

4.2. Diagramele semnalelor de la iesirile TTL si CMOS ale lui GTA-1 si GTA-2, fig. 1.4;

4.3. Valorile masurate ale frecventelor f1 si f2. Descrierea si explicarea operatiunilor de masurare;

4.4. Schemele FTA, fig. 1.5;

4.5. Diagramele semnalelor de la intrarile si iesirile FTA, fig. 1.16;

4.6. Schemele FTM, fig. 1.7;

4.7. Diagramele semnalelor de la intrarile si iesirile FTM, fig. 1.8;

4.8. Schema DF-1, fig. 1.9;

4.10. Diagramele de semnal ale intrarii si primilor 4 biti de iesire ai DF (A0, A1, A2 si A3), in corespondenta temporala.

In constructia diagramelor se va tine seama de urmatoarele:

- inainte de aplicarea primului impuls de tact, divizoarele sunt resetate;

- impulsurile de tact sunt active pe front crescator;

4.11. Schema BIDP, fig. 1.13;

4.12. Schema blocului de semnalizare BS, fig. 1.14;

4.13. Schema blocului de afisaj cu 7 segmente, fig. 1.15;

4.14. Observatii personale ale studentului.

Copyright © 2025 - Toate drepturile rezervate