| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

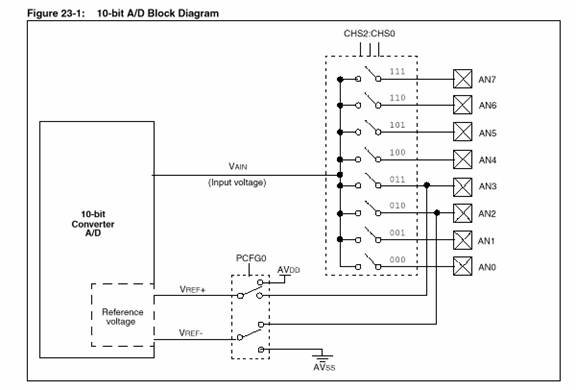

Convertor Analogic/Digital pe 10 biti

Modulul convertorului analog-digital poate avea pana la opt intrari analogice pentru un dispozitiv.

Intrarea analogica incarca un condensator de esantionare si retinere. Iesirea acestui condensator este intrarea convertorului. Convertorul genereaza apoi un raspuns digital corespunzator acestui nivel analogic, prin aproximari succesive. Conversia din analog in digital a semnalului de intrare analogic furnizeaza ca rezultat un numar digital pe 10 biti.

Tensiunile analogice de referinta (pozitiva sau negativa) sunt selectabile prin software fie prin tensiunea de alimentare a dispozitivului (AVdd sau AVss ), fie prin nivelele de tensiune de pe pinii AN3/Vref+ si AN2/Vref-.

Convertorul A/D are o proprietate unica , aceea de a fi capabil sa opereze in modul SLEEP.

Modulul A/D are 4 registri. Acesti registri sunt:

Registrul A/D Result High(ADRESH)

Registrul A/D Result Low(ADRESL)

Registrul de Control A/D 0(ADCON0)

Registrul de Control A/D 1(ADCON1)

Registrul ADCON0, controleaza operatiile modulului A/D. Registrul ADCON1, configureaza functiile pinilor de port. Pinii de port pot fi configurati ca intrari analogice( AN3 si AN2 pot fi de asemenea nivele de tensiune de referinta) sau ca intrari/iesiri digitale.

Figura 1 - Diagrama bloc a modului A/D pe 10 biti

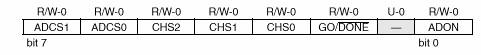

Registrul ADCON0

bitii ADCS1:ADCS0 - Bitii de selectie ai clock-ului de conversie A/D

00 = FOSC/2

01 = FOSC/8

02 = FOSC/32

11 = FRC ( clock-ul derivat din oscilatorul intern RC A/D)

bitii 5:3 CHS2:CHS0 - Bitii de selectie ai canalului analogic

000 = Canalul 0 (AN0)

001 = Canalul 1 (AN1)

010 = Canalul 2 (AN2)

011 = Canalul 3 (AN3)

100 = Canalul 4 (AN4)

101 = Canalul 5 (AN5)

110 = Canalul 6 (AN6)

111 = Canalul 7 (AN7)

Nota: Pentru dispozitivele care nu implementeaza toate cele 8 canale A/D, selectiile neimplementate sunt rezervate. Nu selectati nici un canal neimplementat.

bitul 2 GO/DONE : bitul ce indica starea conversiei A/D

1 = conversia analog-digitatala este in curs de desfasurare (setarea acestui bit porneste conversia, bit care este automat resetat hardware cand conversia A/D este completa)

0 = conversia analog-digitala nu este in progres

bitul 1 Neimplementat: Citit ca '0'

bitul 0 ADON: Bitul A/D pornit

1 = modulul convertor A/D este pornit

0 = modulul convertor A/D este oprit si nu consuma curent

Legenda:

R: Bitul poate fi citit

W: Bitul poate fi scris

U: Bitul este neimplementat , citit ca '0'

-n = Valoarea la resetul POR

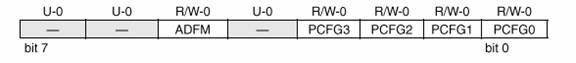

bitii 7:6 Neimplementati : Cititi ca '0'

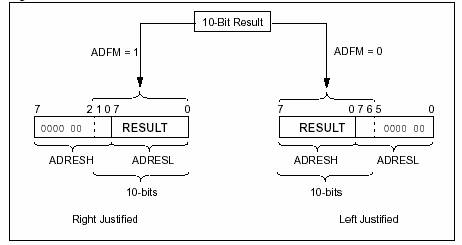

bitul ADFM: selectarea formatului in care se prezinta rezultatul (vazut in Figura 6).

1 = Aliniere la dreapta. Cei 6 biti mai semnificativi ai ADRESH sunt cititi ca '0'

0 = Aliniere la stanga. Cei 6 biti mai putin semnificativi ai ADRESL cititi ca '0'.

Bitul 4 Neimplementat : Citit ca '0'

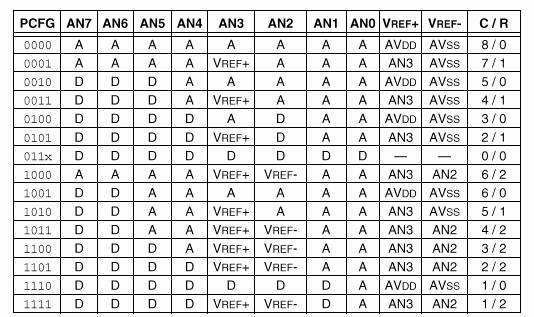

Bitii 3:0 PCFG3:PCFG0 - Bitii de control ai configurarii portului A/D

C/R=numarul de canale de intrare analogice / numarul de nivele de tensiune de referinta A/D

Legenda:

R: Bitul poate fi citit

W: Bitul poate fi scris

U: Bitul este neimplementat , citit ca '0'

-n = Valoarea la resetul POR

Nota1:

La fiecare resetare a dispozitivului, pinii de port care sunt multiplexate cu functii analogice(ANx) sunt fortati sa fie intrari analogice.

![]() Registrii ADRESH:ADRESL contin

rezultatul pe 10 biti a conversiei A/D. Cand conversia A/D este completa, rezultatul

este incarcat in aceasta pereche de registre, bitul GO/DONE (ADCON<2>) este resetat ,

si bitul flag de intrerupere ADIF este setat. Diagramele bloc ale modulului A/D

sunt aratate in Figura 1.

Registrii ADRESH:ADRESL contin

rezultatul pe 10 biti a conversiei A/D. Cand conversia A/D este completa, rezultatul

este incarcat in aceasta pereche de registre, bitul GO/DONE (ADCON<2>) este resetat ,

si bitul flag de intrerupere ADIF este setat. Diagramele bloc ale modulului A/D

sunt aratate in Figura 1.

Dupa ce modulul A/D a fost configurat dupa dorinta, canalul selectat trebuie achizitionat inainte sa fie pornita conversia. Canalele analogice de intrare trebuie sa aiba bitii TRIS corespondenti selectati ca intrari. Pentru a determina timpul de esantionare vezi subsectiunea "Cerintele de achizitie A/D". Dupa ce timpul de achizitie s-a scurs conversia A/D poate fi startata.

Pasii urmatori ar trebui urmati pentru a realiza o conversie A/D:

Configurarea pinilor analogici / a tensiunii de referinta / si a intrarii/iesirii digitale (ADCON1)

Selectarea canalului de intrare (ADCON0)

Selectarea clock-ului de conversie (ADCON0)

Pornirea modulului A/D (ADCON0)

Configurarea intreruperii A/D (daca se doreste aceasta):

Resetarea bitului ADIF

Setarea bitului ADIE

Setarea bitului GIE

3. Asteptarea scurgerii timpului de achizitie necesar.

Pornirea conversiei:

![]() Setarea bitului GO/DONE (ADCON0)

Setarea bitului GO/DONE (ADCON0)

![]() 5. Asteptarea ca conversia A/D sa se termine :

5. Asteptarea ca conversia A/D sa se termine :

fie testand ca bitul GO/DONE sa fi fost resetat ori ca bitul ADIF sa fi fost setat

fie asteptand intreruperea A/D

6. Citirea perechii de registre ce contin rezultatul conversiei A/D (ADRESH:ADRESL), resetarea bitului ADIF , daca este necesar.

7. Pentru urmatoarea conversie , mergeti la pasii 1 sau 2 , dupa cum este necesar.

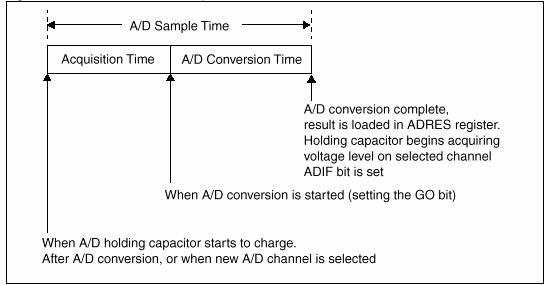

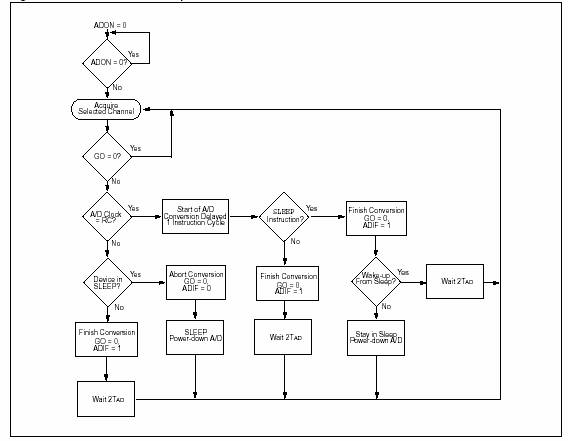

Figura 2 - Secventa de conversie A/D

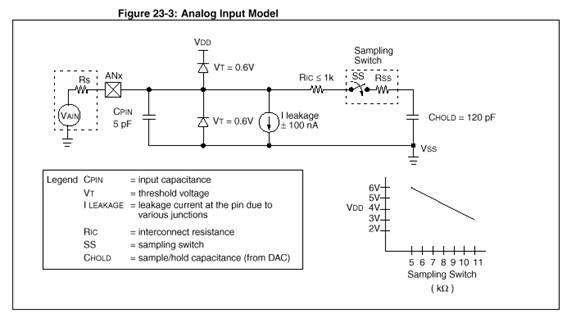

Pentru ca convertorul A/D sa-si atinga acuretatea specifica, condensatorul de retinere (Chold) trebuie sa fie lasat sa se incarce complet pana la nivelul de tensiune al canalului de intrare. Modelul de intrare analogic este aratat in figura 3. Impedanta sursei (Rs) si impedanta switch-ului de esantionare intern (Rss) afecteaza direct timpul necesar incarcarii condensatorului Chold. Impedanta Rss variaza cu nivelul de tensiune Vdd (Figura 3). Impedanta maxima recomandata pentru sursele analogice este de 10k. Pe masura ce impedanta este micsorata, si timpul de achizitie va fi redus. Dupa ce canalul de intrare analogic este selectat, achizitia trebuie facuta inainte ca conversia sa inceapa .

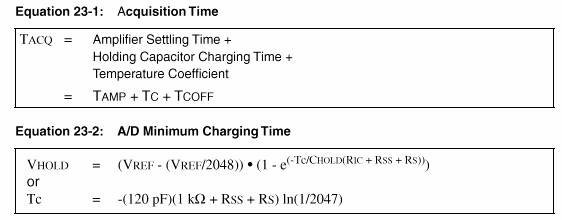

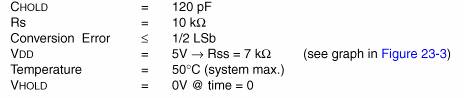

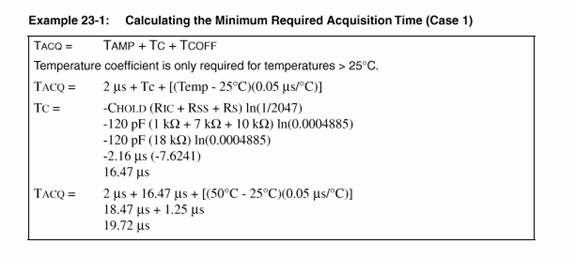

Pentru a calcula timpul minim de achizitie , poate fi folosita Ecuatia 1. Aceasta ecuatie presupune ca este folosita o eroare de ½ LSb (1024 pasi pentru A/D). Eroarea ½ Lsb este eroarea maxima permisa pentru ca A/D sa-si atinga rezolutia specifica.

Ecuatia 1 - Calculul timpului de achizitie

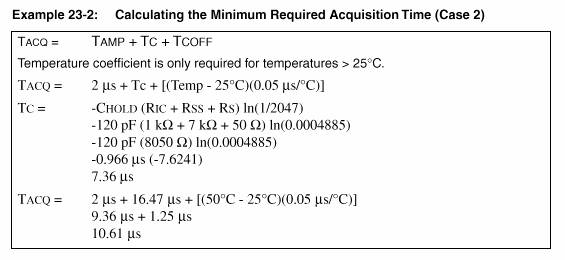

Exemplul 1 arata calcularea timpului minim necesar de achizitie Tacq . Acest calcul este bazat pe sistemul de presupuneri cu privire la aplicatie :

Exemplul 1 - Calculul lui TACQ (timpul de achizitie)

Acum pentru a ne face o idee asupra a ceea ce se intampla cu timpul de achizitie cand impedanta sursei are valoare minima (Rs=50). Exemplul 2 arata aceleasi conditii ca in exemplul 1 numai ca impedanta sursei este la valoare minima (Rs=50).

Exemplul 2 - Calculul lui TACQ minim

Nota1: Nivelul de referinta Vref nu are nici un efect asupra ecuatiei, de vreme ce se anuleaza singura.

Nota2: Condensatorul de retinere (Chold) nu este descarcat dupa fiecare conversie.

Nota3: Impedanta maxima recomandata pentru sursele analogice este de 10k. Aceasta este necesara pentru a indeplini specificatiile pinilor (curentii de scurgere).

Nota4: Dupa ce conversia a fost realizata , o intarziere de 2*TAD trebuie sa se deruleze inainte de o noua achizitie. In acest timp condensatorul de retinere nu este conectat la canalul de intrare A/D selectat.

Figura 3 - Modelul de intrare analogic

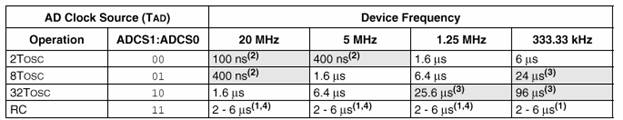

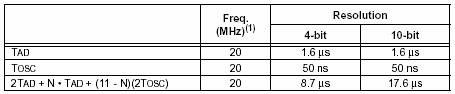

Selectarea clock-ului de conversie A/D

Timpul de conversie per bit este definit ca TAD . Conversia A/D necesita 11.5*TAD pentru o conversie de 10 biti. Sursa clock-ului de conversie A/D este selectabila software. Cele patru optiuni posibile pentru TAD sunt :

2*TOSC

8*TOSC

32*TOSC

oscilatorul RC intern

Pentru conversii A/D corecte, clock-ul de conversie (TAD) trebuie selectat pentru a asigura un timp TAD minim de 1.6us asa cum este aratat in parametrul 130 din sectiunea "Specificatii electrice".

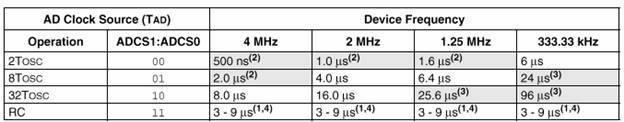

Tabelul 1 arata timpii TAD rezultati derivati din frecventa de operare a dispozitivului si din sursa selectata pentru clock-ul A/D. Acesti timpi sunt pentru dispozitivele care lucreaza in gama standard de tensiuni.

Tabelul 1

Legenda : Casutele hasurate sunt in afara gamei recomandate

Note :

1. Sursa RC are un timp TAD tipic de 4us.

Aceste valori incalca timpul minim necesar TAD .

Pentru timpi de conversie mai mici, este recomandata selectarea unei alte surse pentru clock.

Pentru frecvente ale dispozitivelor mai mari de 1MHz, dispozitivul trebuie sa fie in modul SLEEP pe timpul intregii conversii, altfel acuratetea A/D poate fi in afara specificatiilor.

Tabelul 2

Legenda : Casutele hasurate sunt in afara gamei recomandate

Note :

1. Sursa RC are un timp TAD tipic de 6us.

Aceste valori incalca timpul minim necesar TAD .

Pentru timpi de conversie mai mici, este recomandata selectarea unei alte surse pentru clock.

Pentru frecvente ale dispozitivelor mai mari de 1MHz, dispozitivul trebuie sa fie in modul SLEEP pe timpul intregii conversii, altfel acuratetea A/D poate fi in afara specificatiilor.

6. Configurarea pinilor de port analogici

Registrele ADCON1 si TRIS controleaza functionarea pinilor de port analogici. Pinii de port care se doreste sa functioneze ca intrari analogice trebuie sa aiba bitii TRIS corespunzatori setati (intrari). Daca bitul TRIS este resetat (iesire), nivelul digital de iesire (VOH sauVOL) va fi convertit.

Operatia A/D este independenta de starea bitilor CHS2:CHS0 si a bitilor TRIS.

Nota 1 : La citirea registrului port, orice pin configurat ca un canal de intrare analogica va fi citit ca resetat (nivel low - '0'). Pinii configurati ca intrari digitale vor fi convertiti ca intrari analogice. Nivelele analogice pe o intrare configurata ca digitala nu va afecta acuratetea conversiei.

Nota 2 : Nivelele analogice pe orice pin definit ca intrare digitala (inclusiv pinii AN7:AN0), pot face ca bufferul de intrare sa consume curent in afara specificatiilor dispozitivelor.

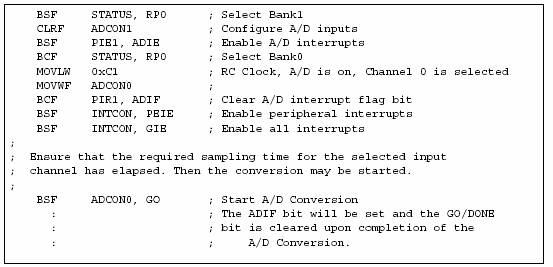

Conversii Analogic-Digitale (A/D)

![]() Exemplul 3

arata cum trebuie realizata o conversie A/D. Pinii portului PORTF si cei patru

pini inferiori ai portului PORTG sunt configurati ca intrari analogice.

Tensiunile de referinta analogice (VREF+ si VREF-) sunt

tensiunile AVDD si AVSS ale dispozitivului.

Intreruperea A/D este acitivata si

clock-ul de conversie este FRC. Conversia este realizata la pinul AN0

(canalul 0).

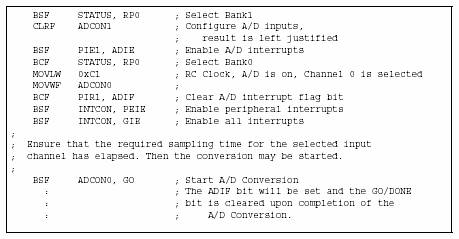

Exemplul 3

arata cum trebuie realizata o conversie A/D. Pinii portului PORTF si cei patru

pini inferiori ai portului PORTG sunt configurati ca intrari analogice.

Tensiunile de referinta analogice (VREF+ si VREF-) sunt

tensiunile AVDD si AVSS ale dispozitivului.

Intreruperea A/D este acitivata si

clock-ul de conversie este FRC. Conversia este realizata la pinul AN0

(canalul 0).

![]() Nota : Bitul

GO/DONE nu ar trebui setat in aceeasi

instructiune care porneste modulul A/D, din cauza cerintelor de timp de

achizitie.

Nota : Bitul

GO/DONE nu ar trebui setat in aceeasi

instructiune care porneste modulul A/D, din cauza cerintelor de timp de

achizitie.

Resetarea bitului GO/DONE in timpul unei conversii va anula conversia curenta. Perechea de registre ce contin rezultatul conversiei nu va fi actualizata cu rezultatul partial la conversiei. Astfel registrele ADRESH:ADRESL vor continua sa contina rezultatul ultimei conversii complete (sau ultima valoare inscrisa in ele). Dupa ce conversia A/D este abandonata, un timp de asteptare de 2*TAD este necesar inainte de a porni o noua conversie. Dupa acest timp, achizitia pe canalul selectat este pornita automat.

Exemplul 3 - Conversia A/D

Figura 4 - Ciclii TAD de conversie

Figura 5 - Diagrama de desfasurare a operatiilor A/D

Compromisul intre o conversie mai rapida si o rezolutie mai slaba

Nu toate aplicatiile necesita un rezultat cu o rezolutie de 10 biti, in schimb pot necesita un timp de conversie mai mic. Modulul A/D permite utilizatorilor sa faca compromisul intre viteza de conversie si rezolutie. Indiferent de solutia necesitata, timpul de achizitie este acelasi. Pentru a accelera conversia, sursa pentru clock-ul modulului A/D poate fi schimbata astfel incat timpul TAD incalca timpul minim specificat. Odata ce TAD a incalcat timpul minim, toti bitii rezultatului conversiei A/D nu sunt valizi. Sursa clock-ului poate fi comutata doar intre cele trei versiuni de oscilator (nu si cea RC). Ecuatia pentru determinarea timpului inainte ca oscilatorul sa poata fi schimbat este :

Timpul de conversie = TAD + N*TAD + (11-N)*2*TOSC , unde N este numarul de biti de rezolutie necesari.

De vreme ce TAD este bazat pe oscilatorul dispozitivului, utilizatorul trebuie sa foloseasca o metoda (un timer, o bucla software,etc) pentru a determina cand poate fi schimbat oscilatorul A/D. Exemplul 4 arata o comparatie intre timpul necesar pentru o conversie cu rezolutia de 4 biti si o conversie cu rezolutia de 10 biti. Exemplul este pentru dispozitive ce opereaza la 20MHz (clock-ul A/D este programat pentru 32*TOSC) si presupune ca imediat dupa 6*TAD clock-ul A /D este programat pentru 2*TOSC.

Valoarea 2*TOSC incalca timpul TAD minim, de vreme ce ultimii 4 biti nu vor fi convertiti in valori corecte.

Exemplul 4 - Timpii de conversie pentru rezolutii de 4 si 8 biti

Note : 1. Este necesar un timp TAD minim de 1.6us

2.Daca este necesara conversia completa pe 8 biti, sursa pentru clock- ul A/D nu ar trebui schimbata.

Registrele pentru rezultatul conversiei A/D

Perechea de registre ADRESH :ADRESL este locul unde este incarcat rezultatul pe 10 biti al conversiei A/D, la incheierea acesteia. Perechea de registre este pe 16 biti. Modulul A /D da posibilitatea alinierii la stanga sau la dreapta a rezultatului pe 10 biti in registrul de 16 biti. Bitul de selectie a formatului A/D (ADFM) controleaza aceasta aliniere. Figura 6 arata operatia de aliniere a rezultatului. Bitii in plus sunt incarcati cu '0'. Cand un rezultat A/D nu va suprascrie acesti registri (A/D este dezactivat), ei pot fi folositi ca 2 registre de uz general pe 8 biti.

Figura 6 - Alinierea rezultatului conversiei A/D

Functionarea in modul SLEEP

![]() Modulul A/D poate opera

si in modul SLEEP. Aceasta

necesita ca sursa pentru clock-ul A/D sa fie RC (ADCS1:ADCS0=11). Cand este

selectata sursa de clock RC, modulul A/D asteapta un ciclu instructiune inainte

de a porni conversia. Aceasta

permite executia instructiunii SLEEP , ceea ce

elimina toate zgomotele digitale de comutare interne din conversie. Cand

conversia s-a incheiat, bitul GO/DONE va fi resetat si

rezultatul este incarcat in registrul ADRES. Daca intreruperea A/D

este validata, dispozitivul se va trezi din SLEEP. Daca intreruperea este

dezactivata, modulul A/D va fi oprit, desi bitul ADON va ramane setat.

Modulul A/D poate opera

si in modul SLEEP. Aceasta

necesita ca sursa pentru clock-ul A/D sa fie RC (ADCS1:ADCS0=11). Cand este

selectata sursa de clock RC, modulul A/D asteapta un ciclu instructiune inainte

de a porni conversia. Aceasta

permite executia instructiunii SLEEP , ceea ce

elimina toate zgomotele digitale de comutare interne din conversie. Cand

conversia s-a incheiat, bitul GO/DONE va fi resetat si

rezultatul este incarcat in registrul ADRES. Daca intreruperea A/D

este validata, dispozitivul se va trezi din SLEEP. Daca intreruperea este

dezactivata, modulul A/D va fi oprit, desi bitul ADON va ramane setat.

Cand sursa pentru clock-ul A/D este alta decat RC, o instructiune SLEEP va abandona conversia curenta si va opri modulul A/D (pentru conservarea energiei), desi bitul ADON va ramane setat.

Oprirea modulului A/D il pune pe acesta in starea de consum minim de curent.

![]() Nota : Pentru ca

modulul A/D sa opereze in modul SLEEP, sursa pentru clock-ul A/D trebuie sa fie

RC (ADCS1:ADCS0=11). Pentru a

permite conversiei sa aiba loc in SLEEP, asigurati-va

ca instructiunea SLEEP urmeaza imediat dupa instructiunea care seteaza

bitul GO/DONE.

Nota : Pentru ca

modulul A/D sa opereze in modul SLEEP, sursa pentru clock-ul A/D trebuie sa fie

RC (ADCS1:ADCS0=11). Pentru a

permite conversiei sa aiba loc in SLEEP, asigurati-va

ca instructiunea SLEEP urmeaza imediat dupa instructiunea care seteaza

bitul GO/DONE.

Efectele unui Reset

Resetarea unui dispozitiv forteaza toate registrele sa intre in starea lor de reset. Acest lucru forteaza oprirea modulului A/D si abandonarea oricarei conversii in desfasurare.

Valoarea care este in registrele ADRESH:ADRESL nu este modificata de un Reset la pornire (Power-on Reset). Registrele ADRESH:ADRESL vor contine valori necunoscute dupa un Power-on Reset.

Acuratetea/Eroarea conversiei A/D

In sistemele in care frecventa dispozitivului este joasa, este de preferat utilizarea clock-ului RC pentru A/D. Pentru frecvente medii si inalte TAD trebuie derivat din oscilatorul dispozitivului.

Acuratetea absoluta specificata pentru convertorul A/D include suma tuturor contributiilor pentru eroarea de cuantizare, eroarea integrala, eroarea diferentiala, eroarea de scala completa, eroarea de offset si monotonia. Este definita ca deviatia maxima intre tranzitia reala si cea ideala pentru orice cod. Eroarea absoluta a convertorului A/D este specificata ca < ±1 LSb pentru VDD=VREF (in gama de operare specificata pentru dispozitiv). Totusi acuratetea convertorului A/D se va degrada pe masura ce VDD se indeparteaza de VREF.

Pentru o gama data de intrari analogice, codul digital de iesire va fi acelasi. Aceasta se datoreaza cuantizarii intrarii analogice intr-un cod digital. Eroarea de cuantizare este tipic de ± ½ LSb si este inerenta in procesul de conversie din analogic in digital. Singura cale de a reduce eroarea de cuantizare este cresterea rezolutiei convertorului A/D.

Eroarea de offset masoara prima tranzitie reala fata de prima tranzitie ideala pentru unui cod. Eroarea de offset deplaseaza intreaga functie de transfer. Eroarea de offset poate fi calibrata in sistem sau introdusa in sistem prin interactiunea curentului total de scurgere si a impedantei sursei la intrarea analogica.

Eroarea de castig (gain error) masoara deviatia maxima intre ultima tranzitie reala si ultima tranzitie ideala ajustata cu eroarea de offset. Aceasta eroare apare ca o modificare in panta functiei de transfer. Diferenta intre eroarea de castig si eroarea de scala completa este aceea ca scara completa nu ia in calcul eroarea de offset. Eroarea de castig poate fi calibrata prin software.

Eroarea de linearitate se refera la uniformitatea schimbarii codului. Erorile de linearitate nu pot fi calibrate in afara sistemului. Eroarea de nelinearitate integrala masoara tranzitia reala a codului fata de tranzitia ideala a codului ajustata cu eroarea de castig pentru fiecare cod.

Nelinearitatea diferentiala masoara latimea maxima reala a codului fata de latimea ideala a codului. Aceasta marime este neajustata.

Curentul de scurgere maxim prin pin este specificat in parametrul D060 din specificatiile electrice cuprinse in documentatia dispozitivului.

TAD nu trebuie sa incalce valoarea minima si ar trebui minimizat pentru a reduce inacuratetea datorata zgomotului si descarcarii condensatorului de esantionare.

In sistemele in care dispozitivul va intra in modul SLEEP dupa inceputul conversiei A/D, selectarea sursei RC pentru clock este necesara. In acest fel zgomotul digital dela modulele in SLEEP este oprit. Aceasta metoda da o mare acuratete.

Consideratii legate de conexiuni

Daca tensiunea de intrare depaseste valorile limita (VSS sau VDD) cu mai mult de 0.3V, acuratetea conversiei este in afara specificatiilor.

Un filtru RC extern este adaugat uneori pentru a contracara deplasarea semnalului de intrare. Componenta R trebuie aleasa pentru a asigura ca impedanta totala a sursei este mentinuta sub 10Kohmi (specificatie recomandata). Orice componenta externa conectata (prin impedanta mare) la un pin de intrare analogica (condensator, dioda Zener,etc) trebuie sa aiba un curent de scurgere foarte mic prin pin.

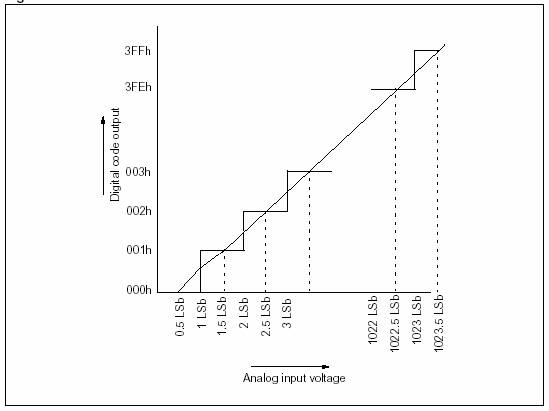

Functia de transfer

Functia de transfer ideala a convertorului A/D este urmatoarea : prima tranzitie se produce cand tensiunea analogica de intrare (VAIN) este 1 LSb (sau VREF/1024) (figura 7).

Figura 7 - Functia de transfer A/D

Initializari

Exemplul 5 prezinta o initializare a modulului A/D.

Exemplul 5 - Initializarea modulului A/D

Sfaturi de proiectare

Intrebarea 1 : Am gasit ca rezultatul convertorului analogic-digital nu este

intotdeauna precis. Ce pot face pentru a imbunatati acuratetea?

Raspunsul 1 : - Asigurati-va ca indepliniti toate specificatiile de timp. Daca

porniti si opriti modulul, exista o intarziere minima ce trebuie sa treaca inainte de a lua un esantion. Daca schimbati canalele de intrare, apare si aici o intarziere, plus TAD, care este timpul necesar conversiei pentru fiecare bit. Acesta este selectat in ADCON0 si ar trebui sa fie intre 1.6us si 6us. Daca TAD este prea scurt, se poate ca rezultatul sa nu fie complet convertit inainte ca sa se termine conversia, iar daca TAD este prea mare, tensiunea de pe condensatorul de esantionare poate scadea inainte de terminarea conversiei. Aceste specificatii de timp sunt prezentate in sectiunea "Specificatii electrice". Vezi documentatia dispozitivului pentru informatiile specifice ale acestuia.

Adesea impedanta sursei semnalului analogic este mare (mai mare de 1Kohm), incat curentul absorbit de la sursa pentru a incarca condensatorul de esantionare poate afecta acuratetea. Daca semnalul de intrare nu se modifica prea rapid, incercati sa puneti un condensator de 0.1uF pe intrarea analogica. Acest condensator se va incarca la tensiunea analogica ce este esantionata si asigura curentul instantaneu necesar pentru a incarca condensatorul intern de pastrare de 120pF.

Direct din manual: "In sistemele in care frecventa dispozitivului este joasa, este de preferat folosirea clock-ului A/D derivat din oscilatorul dispozitivului Aceasta reduce, intr-o mare masura, efectele zgomotului digital de comutare." si "In sistemele in care dispozitivul va intra in modul SLEEP dupa inceputul conversiei A/D, este necesara selectarea sursei RC pentru clock. Aceasta metoda da cea mai mare acuratete."

Intrebarea 2 : Dupa pornirea unei conversii A/D pot schimba canalul de intrare

(pentru urmatoarea conversie)?

Raspunsul 2 : Dupa ce condensatorul de pastrare este deconectat de la canalul de

intrare, tipic la 100ns dupa ce bitul GO este setat, canalul de intrare

poate fi schimbat.

Intrebarea 3 : Cunoasteti referinte bune cu privire la A/D ?

Raspunsul 3 : O referinta foarte buna pentru a intelege conversiile A/D este

"Analog-Digital Conversion Handbook", editia a treia, Prentice

Hall.

Note de aplicatie care au legatura cu modulul

Aceasta sectiune prezinta notele de aplicatie care au legatura cu aceasta sectiune a manualului. Acestea pot sa nu fie implementate doar pentru aceste tipuri de circuite, dar conceptele sunt pertinente si pot fi utilizate (cu modificari si posibile limitari). Notele de aplicatie care au legatura cu modulul A/D pe 10 biti sunt:

Titlu Numarul notei de aplicatie

Utilizarea Convertorului analogic-digital AN546

Voltmetru digital cu 4 canale, display si tastatura AN557

Copyright © 2025 - Toate drepturile rezervate