| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Interfata seriala UART (Universal Asynchronous Receiver and Transmitter).

1. Prezentare generala

AT90S8535 este prevazut cu un UART duplex complet. Principalele caracteristici ale acestuia sunt:

Generatorul intern pentru orice rata de Baud;

Date pe 8 sau 9 biti;

Filtrare a zgomotului;

Detectie de depasire;

Detectia erorilor de incadrare;

Detectia unui eventual bit fals de start;

Trei intreruperi separate: TX complet, registru de date TX gol, RX complet.

Forma de unda pe linia de interfata seriala contine un bit de start (valoare 0 logic), 8 sau 9 biti de date si 1 bit de stop (valoare 1 logic), ca in figura 9.1

![]()

![]()

![]()

Start B1 B2 B3 B4 B5 B6 B7 B8

Figura 9.1. - Structura unui cadru de date transmise serial

2. Transmisia datelor.

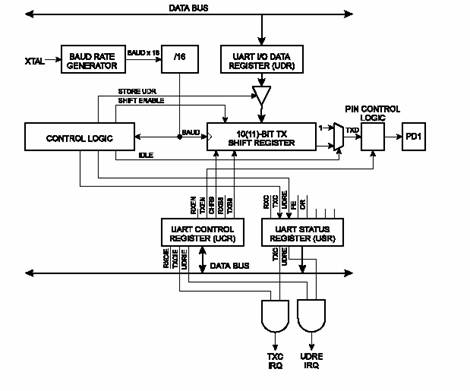

Schema bloc a transmitatorului UART-ului este prezentata in figura 9.2.

Figura 9.2. - Transmitatorul UART

Transmisia de date este initiata prin scrierea datelor ce urmeaza a fi transmise in registrul de date I/O al UART-ului, UDR. Transferul datelor din UDR in registrul de deplasare se realizeaza atunci cand:

Un nou caracter a fost scris in UDR dupa ce a fost transmis bitul stop al caracterului anterior. Registrul de deplasare este incarcat imediat;

Un nou caracter a fost scris in UDR inainte ca bitul stop al caracterului anterior sa fi fost transmis. Registrul de deplasare este incarcat atunci cand a fost transmis bitul stop al caracterului in curs de transmitere.

Daca registrul de deplasare al transmisiei de 10 sau 11 biti este gol, datele sunt transferate din UDR catre registrul de deplasare. In acest moment, este setat bitul UDRE (indicator ca registrul de date al UART-ului este gol) din registrul de stare al UART-ului, USR. In momentul setarii acestui bit (in 1), UART-ul este pregatit sa primeasca urmatorul caracter. In paralel, cand datele sunt transferate din UDR catre registrul de transfer de 10 sau 11 biti, bitul 0 al registrului de deplasare este sters (bitul Start), iar bitul 9 sau 10 este setat (bitul stop). Daca se lucreaza cu cuvinte de date de 9 biti (aceasta inseamnand ca bitul CHR9 din registrul UCR - registrul de control al UART-ului - este setat), atunci bitul TXB8 din UCR este transferat in bitul 9 din registrul de deplasare al transmisiei.

Pe tactul de ceas dat de rata de Baud, ce urmeaza operatiei de transfer catre registrul de deplasare, bitul start este scos afara pe pinul TXD. Apoi, incepand cu LSB, urmeaza datele.

Imediat dupa transmiterea Bitului de stop, daca au fost scrise date noi in UDR pe durata transmisiei, acestea se vor transfera in registrul de deplasare. In timpul acestui transfer, bitul UDRE este setat. El va ramane in starea 1 pana cand UDR-ul va fi scris din nou. Atunci cand nu au fost scrise noi date iar bitul stop a fost prezent pe TXD pentru o lungime de bit, flagul TX complet (TXC) din USR este setat.

Atunci cand bitul TXEN din UCR este setat (1), se activeaza emitatorul UART-ului. Cand acest bit este sters (0), pinul PD1 poate fi folosit drept pin de I/O general. Cand TXEN este setat, emitatorul UART-ului va fi conectat la PD1, acesta fiind fortat sa fie iesire indiferent de setarea bitului DD1 din DDRD.

3. Receptia datelor.

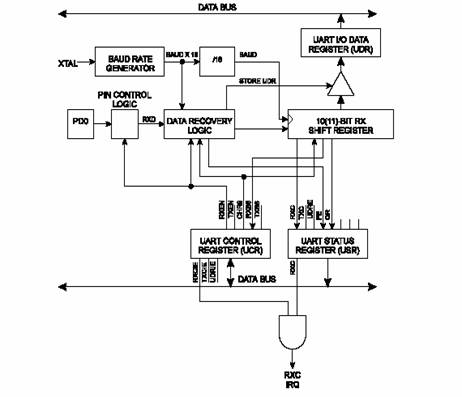

Interfata receptorului (figura 9.3) esantioneaza semnalul pe pinul RXD cu o frecventa de 16 ori mai mare decat rata de Baud. Atunci cand linia este in modul IDLE, o valoare de zero logic va fi interpretata drept front descrescator al bitului start, in acest fel fiind initializata secventa de detectare a bitului start. Dupa tranzitia de la 1 la 0, receptorul preia ca esantioane ale pinului RXD, mostrele 8, 9 si 10. Daca doua sau mai multe din aceste trei mostre sunt detectate a fi unu logic, bitul start este respins fiind considerat eroare data de zgomotul pe linie, iar receptorul incepe sa caute urmatoarea tranzitie de la 1 la 0.

Daca este detectat un bit de start valid, se executa preluarea ca esantioane a bitilor de date care urmeaza dupa bitul start. Acesti biti sunt de asemenea preluati prin vot majoritar intre esantioanele 8, 9 si 10. Valoarea logica gasita in cel putin doua din trei esantioane este luata ca valoare a bitului. Pe masura ce sunt preluati ca esantioane, toti bitii sunt transferati in registrul de deplasare al transmitatorului.

Atunci cand bitul stop intra in receptor, pentru ca acesta sa fie acceptat, majoritatea dintre cele trei esantioane trebuie sa fie unu. In situatia in care cel putin doua esantioane sunt zero logic, este setat flagul de eroare de incadrare (FE) din registrul de stare al UART-ului (USR).

Figura 9.3. - Receptorul UART

Inainte de a citi registrul UDR, utilizatorul ar trebui sa verifice intotdeauna bitul FE pentru a detecta erorile de incadrare. Chiar daca la sfarsitul unui ciclu de receptionare de caracter este sau nu este detectat un bit stop valid, datele sunt transferate in UDR iar flagul RXC din USR este setat.

UDR-ul este alcatuit de fapt din doua registre fizic separate, unul pentru transmiterea de date iar celalalt pentru receptia lor. La citirea UDR-ului este accesat registrul de receptionare a datelor, iar la scrierea sa este accesat registrul de transmitere a datelor. Pe durata transferului de date catre UDR, daca este selectat un cuvant de date de 9 biti (bitul CHR9 din UCR - registrul de control al UART-ului este setat), atunci bitul RXB8 din UCR este incarcat cu bitul 9 din registrul de deplasare al transmitatorului.

Indicatorul de depasire (OR) din UCR este setat in situatia in care, dupa ce a receptionat un caracter, registrul UDR nu a mai fost citit din momentul inregistrarii penultimei receptii. Aceasta inseamna ca ultimul octet de date transferat in registrul de transfer nu a putut fi transferat catre UDR si a fost pierdut. Bitul OR este buferat si este actualizat in momentul in care este citit un octet de date valid din UDR. In concluzie, utilizatorul ar trebui sa verifice intotdeauna bitul OR in urma unei citiri a registrului UDR, pentru ca astfel sa detecteze orice depasire.

Receptorul este dezactivat atunci cand bitul RXEN din registrul UCR este sters (zero). In acest caz, pinul PD0 poate fi folosit ca pin I/O general. Atunci cand RXEN este setat, receptorul UART-ului va fi conectat la PD0, acesta fiind fortat sa fie pin intrare, oricare ar fi setarea bitului DDD0 din DDRD. In situatia in care PD0 este fortat de catre UART sa fie intrare, bitul PORTD0 poate sa fie inca folosit pentru a controla rezistorul de tragere in Vcc (pull-up resistor) de pe pin.

4. Controlul blocului UART.

Registrul de date I/O al UART-ului - UDR.

UDR

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

$0C($2C) |

MSB |

LSB |

||||||

|

Citeste/Scrie |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

|

Valoare initiala |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Registrul UDR este alcatuit din doua registre separate fizic care impart aceeiasi adresa I/O. Prin scriere in UDR este de fapt scris registrul de transmitere a datelor UART-ului, iar prin citirea din UDR este de fapt citit registrul de receptie a datelor UART-ului.

Registrul de stare a UART-ului - USR.

USR

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

$0B($2B) |

RXC |

TXC |

UDRE |

FE |

OR |

- |

- |

- |

|

Citeste/Scrie |

C |

C/S |

C |

C |

C |

C |

C |

C |

|

Valoare initiala |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Registrul USR este un registru de citire (cu exceptia TXC - C/S) ce furnizeaza informatii privitoare la starea UART-ului.

Bitul 7 - RXC: Receptie completa in UART.

Acest bit este setat (in 1) atunci cand un caracter receptionat este transferat din registrul de deplasare al receptorului catre UDR. Bitul este setat indiferent de detectarea oricaror erori de incadrare. Intreruperea de receptie completa a UART-ului va fi executata atunci cand atat bitul RXCIE din UCR, cat si bitul RXC, sunt fiecare setati. RXC este sters prin citirea UDR-ului. Atunci cand este folosita receptia prin intreruperi, rutina de intrerupere a UART-ului trebuie sa citeasca UDR-ul pentru a realiza stergerea RXC-ului; altfel, indata ce rutina de intrerupere se termina, o noua intrerupere va apare.

Bitul 6 - TXC: Transmitere completa din UART.

Bitul este setat atunci cand amandoua conditiile urmatoare sunt satisfacute:

Intregul caracter (inclusiv bitul stop) din registrul de deplasare a transmiterii a fost scos afara;

Nu au mai fost scrise date noi in UDR.

Acest indicator este foarte util la interfetele de comunicare semi-duplex, atunci cand dupa o transmisie trebuie trecut in starea de receptie si eliberata magistrala de comunicatie imediat dupa terminarea transmisiei.

In situatia in care bitul TXCIE din UCR este setat, setarea si a TXC-ului conduce la executarea intreruperii de terminare a transmisiei din UART. Indicatorul TXC este sters de catre hardware atunci cand este executat vectorul de deservire a intreruperii corespunzator. Ca alternativa, bitul TXC este sters (zero) prin scrierea unui unu logic in el.

Bitul 5 - UDRE: Golirea registrului de date al UART-ului.

Bitul este setat (unu) atunci cand un caracter scris in UDR este transferat in registrul de deplasare pentru transmitere. Setarea acestui bit indica faptul ca emitatorul UART-ului este pregatit sa primeasca un nou caracter in vederea transmiterii.

Intreruperea UART-ului de finalizare a transmiterii este executata atunci cand atat bitul UDRIE din UCR, cat si UDRE sunt fiecare setati. UDRE este sters prin scrierea UDR-ului. Pentru stergerea UDRE in situatia in care este folosita transmisia cu intrerupere, rutina de deservire a intreruperii respective trebuie sa scrie in UDR; altfel, in momentul in care rutina de intrerupere este terminata, va apare o noua intrerupere.

In timpul resetarii, pentru a indica faptul ca emitatorul UART-ului este pregatit de lucru, UDRE este setat (unu).

Bitul 4 - FE: Eroare de incadrare.

In situatia in care este detectata o eroare de incadrare, ca de exemplu atunci cand bitul stop al unui caracter ce soseste este zero, bitul FE este setat. FE-ul este sters atunci cand bitul stop al unei date primite este unu.

Bitul 3 - OR: Depasire.

Acest bit este setat daca este detectata o situatie de depasire; de exemplu atuci cand un caracter deja existent in registrul UDR nu este citit inainte ca urmatorul caracter sa fi fost transferat in registrul de deplasare receptor. Bitul OR este citit din buffer, ceea ce inseamna ca el va fi setat imediat ce o data valida aflata inca in UDR este citita.

Bitul OR este sters (zero) atunci cand un caracter este receptionat si transferat in UDR.

Bitii 20 - Res: Biti rezervati.

Acesti biti sunt biti rezervati in AT90S8535 si se vor fi cititi intotdeauna ca zero.

Registrul de control al UART-ului - UCR.

UCR

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

$0A($2A) |

RXCIE |

TXCIE |

UDRIE |

RXEN |

TXEN |

CHR9 |

RXB8 |

TXB8 |

|

Citeste/Scrie |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

C |

C/S |

|

Valoare initiala |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Bitul 7 - RXCIE: Activarea intreruperii cand RX este completa.

Rutina de intrerupere in cazul unei receptionarii complete va fi executata atunci cand:

1. Bitul RXCIE este setat (unu);

2. Bitul RXC din USR este setat (unu);

3. Intreruperile globale sunt activate.

Bitul 6 - TXCIE: Activarea intreruperii cand TX este completa.

Rutina de intrerupere in cazul unei transmisii complete va fi executata atunci cand:

1. Bitul TXCIE este setat (unu);

2. Bitul TXC din USR este setat (unu);

3. Intreruperile globale sunt activate.

Bitul 5 - UDRIE: Activarea intreruperii UART-ului la golirea registrului de date.

Rutina de intrerupere a UART-ului la golirea registrului de date va fi executata atunci cand:

1. Bitul UDRIE este setat (unu);

2. Bitul UDRE din USR este setat (unu);

3. Intreruperile globale sunt activate.

Bitul 4 - RXEN: Activarea receptorului.

Setarea acestui bit activeaza receptorul UART-ului. Prin

dezactivarea receptorului indicatorii

Bitul 3 - TXEN: Activarea emitatorului.

Atunci cand este setat (unu), acest bit activeaza emitatorul UART-ului. La dezactivarea emitatorului in timpul transmiterii unui caracter, el nu este dezactivat pana in momentul in care caracterul din registrul de transfer plus oricare alt caracter care se afla deja in UDR nu au fost complet transmisi.

Bitul 2 - CHR 9: Caractere de 9 biti.

Cand acest bit este setat (unu), lungimea caracterelor transmise si receptionate este de 9 biti plus bitii start si stop. Cel de-al 9-lea bit este citit si scris prin folosirea respectiv a bitilor RXB 8 si TXB 8 din UCR. Al 9-lea bit de date poate fi folosit drept bit de stop suplimentar sau drept bit de paritate.

Bitul 1 - RXB 8: bitul de date 8 la receptie.

Atunci cand bitul CHR 9 este setat (unu), bitul RXB 8 este al 9-lea bit de date al caracterului receptionat.

Bitul 0 - TXB 8: bitul de date 8 la transmisie.

Atunci cand bitul CHR 9 este setat (unu), bitul TXB 8 este al 9-lea bit de date al caracterului de transmis.

5. Generatorul de rata de Baud.

Generatorul de rata de Baud este un dispozitiv divizor de frecventa care genereaza frecventa dorita pentru comunicatie conform cu urmatoarea ecuatie:

BAUD = ck/(16 (UBRR + 1))

in care:

BAUD = rata de Baud;

ck = frecventa oscilatorului cu cristal;

UBRR = continutul registrului rata de Baud al UART-ului, UBRR (0-255), aflat la adresa $09.

Rezulta ca pentru o frecventa a ceasului si o rata de Baud date, trebuie scrisa in UBRR urmatoarea valoare:

UBRR=fck/(16 BAUD) - 1

De exemplu, pentru un cristal de 4 MHz si o rata de baud dorita de 9600 bps, valoarea care trebuie scrisa in UBRR este $19.

Se va realiza un program de transmisie seriala catre un calculator, fara receptie.

Initializarile vor fi urmatoarele:

Stiva la $025F;

Validare numai a transmisiei, fara intreruperi;

Rata de baud 9600 bps.

Indicatii:

In programul principal se va citi continuu portul PINA si se va detecta aparitia unei schimbari. Aceasta se poate face prin memorarea valorii initiale intr-un registru si comparatia in bucla a acestuia cu registrul in care se citeste portul APIN. In caz de egalitate se ramine in bucla, iar in caz de neegalitate se reactualizeaza registrul starii curente si se cheama rutina de transmisie dupa care se revine in bucla principala.

Rutina de transmisie va scrie in UDR valoarea citita. Nu se va reveni din aceasta rutina pana cand nu s-a terminat transmisia, fapt constatat prin citirea in bucla a bitului TXC din USR, pana cand este gasit in 1 logic.

Pe calculator se va rula un program de comunicatie seriala, de exemplu Hyperterminal, setat pe portul COM1 sau COM2 (cel disponibil), cu parametrii 9600/n/8/1 (fara paritate, caracter de 8 biti si un bit de stop).

Un exemplu de realizare a programului este urmatorul:

.Include "8535def.inc"

.equ Leds=PORTC

;RESET

rjmp Reset

.ORG $0020

Reset:

;Initializare stiva

ldi r17,high(RAMEND);Octet sup. al ultimei adr. din RAM

ldi r16,low(RAMEND) ;octet inf. al ultimei adr. din RAM

out SPH,r17 ;trimisi in octetul superior al SP

out SPL,r16 ;si in octetul inferior al SP

;Initializare In-Out

ldi r16,$ff ;C ca iesire

out DDRC,r16

ldi r16,$00 ;A ca intrare

out DDRA,r16

;validarea transmisiei

ldi r16,(1<<TXEN)

out UCR,r16

;stabilirea vitezei(baud=9600)

ldi r16,$19

out UBRR,r16

main:

in r18,PINA ;citeste valoarea actuala a pinilor

cp r18,r20 ;compara cu valoarea anterioara

breq main ;daca e egala, nu s-a modificat nimic

mov r20,r18 ;daca nu e egala, se reactualizeaza

rcall trans ;si se transmite noua valoare

rjmp main

trans:

out $0c,r18 ;Scrie caracterul in UDR

test:

in r17,USR ;Testeaza in bucla

andi r17,$40 ;terminarea transmisiei

cpi r17,$40

brne test

ret

2. Se va modifica programul anterior astfel ca sa fie activata si receptia de la calculator (datele fiind afisate pe leduri) iar transmisia sa se faca numai cand apare o schimbare in datele de pe portul A. Receptia se va executa prin intreruperi.

Indicatii:

Va fi activata si receptia, si va fi validata intreruperea la receptie.

Rutina de receptie este chemata de vectorul $0B din tabela de intreruperi. Aici se va afisa pe led-uri valoarea receptionata.

3. Se vor cupla doua microcontrolere prin interfata seriala cu inversarea liniilor TX si RX. Tastele apasate pe portul de intrare al unui microcontroler vor fi afisate pe portul de iesire al celuilalt, cu eventuale prelucrari.

Copyright © 2025 - Toate drepturile rezervate