| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

PROCESOARE NUMERICE DE SEMNAL

![]()

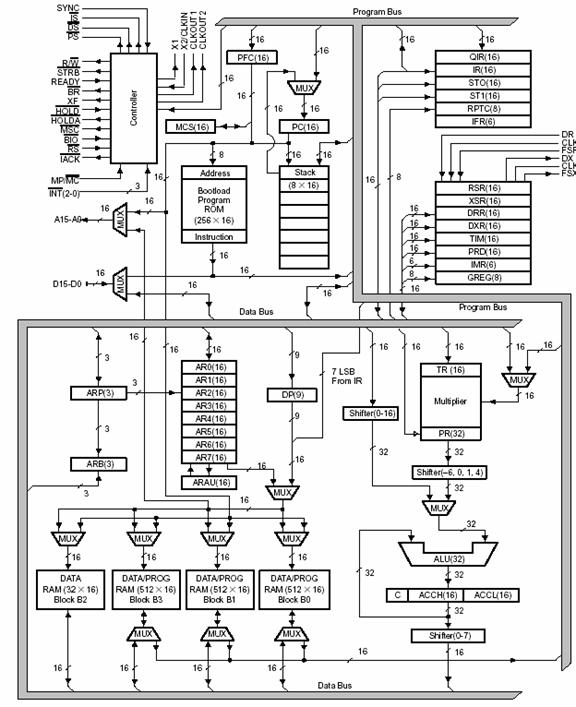

Proiectate initial pentru aplicatii audio/video precum codari si recunoasteri de imagini procesoarele numerice de semnal (DSP) si-au gasit aplicabilitatea si in domeniul controlului proceselor rapide. Sistemele de comanda numerica bazate pe DSP-uri, sunt perfect adaptate controlului aplicatiilor de mare viteza Arhitectura de principiu a unui astfel de sistem este prezentata in figura 3.

Arhitectura de tip Harward, ce asigura cai separate pentru cod si date, permite procesari simultane de date si instructiuni facilitand utilizarea tehnicilor pipe-line.

Unitatea ALU a unui DSP este caracterizata de existenta unui multiplicator hardware ceea ce permite efectuarea unei operatii de tip MAC (Multiply and Accumulate) pe durata unui singur ciclu instructiune, aspect deosebit de important in implementarea algoritmilor de prelucrare a semnalelor. O imbunatatire importanta adusa odata cu folosirea DSP-urilor este si existenta unui set de instructiuni orientat spre tehnicile specifice procesarii semnalelor. Astfel dimensiunea programului si timpul de calcul se reduc considerabil.

Arhitectura DSP-urilor a cunoscut modificari importante, de fapt perfectionari plus completari cu implementari de noi functiuni. Daca spre exemplu primul procesor al firmei Texas Instruments, TMS320C10 continea doar unitatea CPU, RAM pentru date, ROM pentru programe si porturi I/O, unul dintre ultimele procesoare in virgula fixa venit in cadrul familiei, TMS320C54, contine unitatea CPU, RAM pentru date si pentru programe, ROM pentru programe, porturi I/O, ceas programabil, port serial full-duplex, optiune pentru Boot ROM, posibilitate de a adresa un spatiu mai mare de memorie exterioara si altele. Adaugand la toate aceste aspecte si faptul ca timpul pe ciclu instructiune a fost micsorat de la 160 ns la 25ns, ne putem da seama cat de larga este gama de procesoare de semnal disponibile la aceasta ora. Facilitatile de control ale intreruperilor sunt destul de limitate in cazul procesoarelor DSP. In aceste conditii este necesar a se prevedea un hard suplimentar, care sa poata permite programului. aplicatiei sa depisteze rapid cine a cerut o intrerupere si sa stabileasca matricea prioritatii de tratare a intreruperilor, daca este cazul.

Dupa arhitectura si modul de functionare al unitatii de comanda procesoarele pot fi impartite in categoriile CISC, RISC si DSP. n continuare vom incerca sa comparam cele trei arhitecturi amintite:

CISC - complex instruction set computer

Setul de instructiuni este implementat prin microcod permitand instructiuni foarte complexe.

Timpul de executie depinde de comanda sau de secventa de microcod ce trebuie executata si necesita mai multe cicluri de ceas.

Se pot utiliza compilatoare dar in conducerea proceselor rapide acestea nu sunt foarte eficiente deoarece compilatorul nu poate exploata avantajul modurilor de adresare si al seturilor de instructiuni foarte complexe.

Se interfateaza usor cu periferice specifice aplicatiilor de conducere ca: temporizator, ceas de garda, modulator PWM, UART, convertoare A/N si N/A, etc.

Microprocesoarele (CISC) sunt cele mai ieftine si mai flexibile procesoare dar si cele mai lente.

RISC - reduced instruction set computer

Arhitectura de tip load-store:

Operatiile de baza sunt efectuate intre registre

Operatiile ce implica transfer cu memoria sunt efectuate dupa ce data a fost incarcata intr-un registru

Incorporeaza structuri pipe-line care permit executia catorva instructiuni in paralel, conducand la reducerea semnificativa a timpilor de executie (de regula o instructiune pe ciclu de ceas). Structura pipe-line permite ca in acelasi moment in procesor sa se execute mai multe instructiuni aflate in faze diferite. Majoritatea sistemelor RISC sunt organizate pe 5 nivele, permitand executia simultana a 5 instructiuni.

IF (Instruction Fetch) extrage instructiunea din memorie

ID (Instruction Decode) decodifica instructiunea extrasa anterior

EX efectueaza operatiile asupra datelor si calculeaza adresele conform decodificarii anterioare

MA (Memory Access) acceseaza data din memorie in cazul instructiunilor care implica transfer cu memoria

WB (Write Back) scrie rezultatul in memorie la adresa specificata

Foarte multe controlere RISC au adoptat arhitecturi de tip Harward avand spatii separate pentru adrese si date. In acest fel structura se reduce la 4 nivele, extragerea operanzilor fiind efectuata in paralel cu decodificarea instructiunii: IF, ID, EX, WB.

Au un set de instructiuni mic dar foarte eficient.

De regula setul de instructiuni este codificat hard (prin PLA) pentru a optimiza timpul de executie

Setul de instructiuni este ortogonal (format fix - modurile de adresare si tipurile de date sunt specificate independent pentru fiecare instructiune)

Tipurile de date si modurile de adresare alese pentru a genera usor cod optimizat cu ajutorul compilatorului.

Pentru a nu corupe contextul pipe-line la executia instructiunilor de ramificare foarte multe procesoare au instructiuni de salt neconditionat intarziate - adica intai se executa instructiunea aflata dupa instructiunea de ramificare.

Poseda seturi mari de registre, comutabile, asigurand latenta mica la intreruperi. Incorporeaza structuri hard, dedicate pentru implementarea facila a sistemelor de operare (UNIX sau similare).

Pretul circuitelor si al instrumentelor de dezvoltare, in special, le fac mai putin accesibile.

DSP - digital signal processor

Setul de instructiuni codificat hard, optimizat pentru operatii matematice si manipulari de siruri de date.

Se executa o instructiune pe ciclu, in plus o instructiune poate defini cateva operat

Exista compilatoare (C sau PL/M) dar programarea cea mai eficienta se face tot in limbaj de asamblare.

Au cai separate pentru date si program pentru cresterea vitezei. Multiplicatorul hard permite realizarea unei inmultiri intr-un ciclu masina.

Initial procesoarele RISC sau DSP au fost utilizate pentru aplicatii speciale Din punctul de vedere al integrarii componentelor de sistem procesoarele pot fi considerate ca fiind de tip microprocesor sau microcontroler. Diferitele campuri de aplicatii reclama utilizarea unor procesoare diferite. In functie de tipul de procesor se pot particulariza si arhitecturile tipice.

q procesoare pe 16 biti in virgula fixa: 'C1x, 'C2x, 'C2xx, 'C5x, 'C54x si 'C62x(32 biti);

q procesoare pe 32 de biti in virgula mobila: 'C3x, 'C4x, 'C67x;

q DSP multiprocesor 'C8x(cu 4 procesoare numerice de semnal si unul RISC);

q Procesoare dedicate 'AVxxx.

Flexibilitatea functionala si posibilitatile deosebite de calcul numeric fac din membrii familiei TMS320 alternative necostisitoare ale procesoarelor bit-slice sau ale celor VLSI fabricate la comanda. Aceasta familie este ideala pentru o gama larga de aplicatii datorita urmatoarelor calitati:

arhitectura paralela avansata;

executie de mare viteza;

set de instructiuni foarte flexibil;

flexibilitate functionala;

cost eficient.

Toate generatiile familiei TMS320 au un grad superior de paralelizare a functionarii si seturi de instructiuni specializate pentru prelucrarea numerica a semnalului, oferind posibilitatea executiei de pana la 50 MFLOP(milioane de operatii flotante pe secunda) sau 275 MOPS(milioane de operatii pe secunda) cu variantele monoprocesor si peste 2000 MOPS cu cel mai performant membru al familiei, multiprocesorul TMS320C80.

Optimizarea vitezei de functionare a familiei TMS320 s-a obtinut prin implementarea hardware a unor functii implementate software sau microcod la alte familii de microprocesoare.

Fiecare generatie de monoprocesoare a familiei TMS320 are un nucleu de unitate centrala si mai multe configuratii de memorie si periferice integrate in cip, realizate astfel incat sa poata sa satisfaca o gama cat mai larga de necesitati performanta-pret.

Fiecare membru al familiei este insotit de un larg evantai de instrumente de dezvoltare, de la seturi de evaluare pana la sisteme hardware si software complexe ce cuprind: compilatoare optimizatoare pentru limbaje de nivel inalt, depanatoare la nivel de limbaj sursa(C sau asamblare), simulatoare, emulatoare, sisteme de operare in timp real si software de aplicatie.

Familia TMS320 de procesoare numerice de

semnale (16 sau 32 biti) combina intr-un singur cip flexibilitatea

specifica controlerelor de mare viteza cu puterea de calcul a unui

procesor. DSP de inalta performanta TMS320C2x, la fel cu

circuitul TMS320C1x, este implementat printr-o arhitectura de tip Harvard,

care maximizeaza puterea de procesare prin mentinerea a 2 magistrale

separate pentru cele 2 structuri de memorie, de programe si de date,

pentru o executie la viteza maxima. Instructiunile sunt realizate astfel incat sa permita

transferul de date intre cele doua spat Extern, memoriile de date

si programe sunt multiplexate pe aceeasi magistrala, astfel

incat sa se asigure rangurile maxime pentru adrese pentru ambele

spatii in timp ce numarul pinilor circuitului este minim. Generatia 'C2x a debutat cu TMS32020 in tehnologie NMOS care a fost perfectionat

si trecut in tehnologie CMOS, noul produs fiind botezat TMS320C25 (vezi

schema bloc simplificata din fig. 1. La o frecventa tipica de

40MHz procesorul are un ciclu de instructiune de 100 ns.

Familia TMS320 de procesoare numerice de

semnale (16 sau 32 biti) combina intr-un singur cip flexibilitatea

specifica controlerelor de mare viteza cu puterea de calcul a unui

procesor. DSP de inalta performanta TMS320C2x, la fel cu

circuitul TMS320C1x, este implementat printr-o arhitectura de tip Harvard,

care maximizeaza puterea de procesare prin mentinerea a 2 magistrale

separate pentru cele 2 structuri de memorie, de programe si de date,

pentru o executie la viteza maxima. Instructiunile sunt realizate astfel incat sa permita

transferul de date intre cele doua spat Extern, memoriile de date

si programe sunt multiplexate pe aceeasi magistrala, astfel

incat sa se asigure rangurile maxime pentru adrese pentru ambele

spatii in timp ce numarul pinilor circuitului este minim. Generatia 'C2x a debutat cu TMS32020 in tehnologie NMOS care a fost perfectionat

si trecut in tehnologie CMOS, noul produs fiind botezat TMS320C25 (vezi

schema bloc simplificata din fig. 1. La o frecventa tipica de

40MHz procesorul are un ciclu de instructiune de 100 ns.

TMS320C26 are numai 256W ROM in care este implementat un incarcator de initializare (Boot ROM), dar dispune de 1536W RAM Date/Program (B0, B1, B3) si 32 W RAM Date (B2).

Flexibilitatea ridicata a proiectarii sistemului este asigurata prin 2 blocuri de memorie RAM pe circuit(in total 544 de cuvinte pe 16 biti), fiecare fiind configurabil fie ca memorie de program, fi ca memorie de date. Un spatiu de adresare pentru 64K-cuvinte de memorie de date(in afara circuitului) este inclus ca o facilitate pentru implementarea algoritmilor pentru DSP.

Programele pana la 4K-cuvinte pot fi programate in memoria interna ROM. Restul de 64Kcuvinte de memorie program sunt situate extern.

TMS320C2x realizeaza operatii aritmetice in complement fata de 2 folosind ALU de 32 de biti si acumulatorul(ACC). ALU este o unitate aritmetica de uz general, care opereaza folosind cuvinte pe 16 biti preluate din memoria RAM de date sau derivate din instructiunile imediate sau folosind rezultatul pe 32 de biti al registrului multiplicator. Pe langa instructiunile aritmetice uzuale, ALU poate realiza operatii booleene, permitand manipulari de bit cerute de un controler de mare viteza. Acu mulatorul stocheaza rezultatul de la iesirea ALU si este totodata a 2-a intrare in ALU.

Multiplicatorul realizeaza o inmultire 16X16 biti in complement fata de 2, cu rezultatul pe 32 de biti, intr-un singur ciclu instructiune. Multiplicatorul este format din 3 elemente: registrul T(pe 16 biti, stocheaza temporar multiplicatorul), registrul P(pe 32 biti, stocheaza produsul) si aria de multiplicatoare. Valorile de inmultit vin fie din memoria de date, fie din memoria program cand se folosesc instructiunile MAC/MACD fie deriva imediat din instructiunea MPYK(multiply imediate).Multiplicatorul de mare viteza de pe circuit permite realizarea eficienta a operatiilor fundamentale ale procesarii de semnal: convolutia, corelatia si filtrarea.

Circuitul de deplasare si scalare a lui TMS320C2x are o intrare pe 16 biti legata la magistrala de date si o iesire pe 32 de biti legata la ALU. El produce o rotire la stanga cu 0-16 pozitii a datelor de intrare, dupa cum este programat prin instructiune.

Interfata pentru memoria locala a lui TMS320C2x este formata dintr-o magistrala de date paralela pe 16 biti(D15-D0), o magistrala de adrese pe 16 biti(A15-A0), 3 pini pentru selectia memoriei de date sau de program, sau pentru selectarea spatiului de I/O(DS, PS, IS), si alte semnale de control(/STRB, R/W, READY).

Operatiile de control pot fi asistate in TMS320C2x de catre un circuit timer intern pe 16 biti cu registre mapate in memorie, un numarator de repetari, 3 intreruperi externe mascabile pentru utilizator si intreruperi interne generate de operatiile portului serial sau de catre timer.

Un port serial full-duplex realizeaza comunicarea directa cu circuitele seriale cum sunt: codecurile, covertoarele seriale A/D si alte circuite seriale. Cele doua registre ale portului serial mapate in memorie (dat transmisie/receptie) pot opera atat in modul octet cat si modul cuvant.

Comunicatiile seriale intre procesoare pot fi folosite in aplicatii de multiprocesare. TMS320C2x are posibilitatea de a aloca un spatiu global de memorie de date si de a comunica cu acest spatiu prin semnalele BR (bus request) si semnalul de control READY. Exista un registru mapat in memorie pe 8 biti numit GREG(global memory allocation register) care indica modul de alocare al memoriei globale. Un alt procesor poate prelua controlul asupra memoriei externe a lui TMS320C2x trecandu-l pe HOLD in low.

La TMS320C25 sunt disponibile 2 moduri de functionare: modul asemanator lui TMS32020, in care executia este suspendata cat timp HOLD=L si modul DMA, in care TMS320C25 continua sa execute programul sau, in timp ce se opereaza din memoria RAM sau ROM interna, marindu-se astfel eficienta in aplicatii cu prelucrare intensiva.

TMS 320C25 (26) sunt incapsulate in capsule de material plastic cu 68 de terminale de tip PLCC (Plastic Leaded Chip Carrier) sau PGA (Pin Grid Area). Asignarea pinilor pentru capsula PLCC este prezentata in Fig. 2.

(semnal de: Z-inalta impedanta, E-iesire, I-intrare)

A15 . A0 : E, Z

Magistrala de adrese A15 MSB . A0 LSB. Este multiplexata pentru a adresa memoria externa de date/program sau porturile I/E . In modul HOLD liniile A15 . A0 trec in inalta impedanta

Magistrala de date D15 MSB . D0 LSB. Este multiplexata pentru a transfera datele intre TMS320C2x si memoria externa de date/program sau porturile I/E . Plasata in inalta impedanta cand nu se scot date in exterior, sau cand este activat unul din semnalele /RS sau /HOLD .

/DS, /PS, /IS : E, Z

Semnale pentru selectia spatiilor de memorie date, program, respectiv porturi I/E. Sunt tot timpul in 'high', nivelul 'low' indicand selectarea unui anumit spatiu extern. .

READY : I

Semnal de intrare ce indica faptul ca circuitul extern adresat este capabil pentru efectuarea unui transfer pe magistrala. Daca dispozitivul extern nu este gata (READY = 0), TMS320C2x asteapta un ciclu, apoi testeaza din nou semnalul READY. De asemenea READY indica acceptarea unui acces la magistrala unui dispozitiv extern dupa un semnal /BR.

R/W : E, Z

Semnal citire/scriere ce indica directia transferului in cazul comunicatiei cu un dispozitiv extern. In mod normalul semnalul este in 'high' (mod citire), nivelul 'low' indicand o operatie de scriere. In modul HOLD este plasat in inalta impedanta.

/STRB : E, Z

Semnal de strob (validare. In mod normalul este in 'high', nivelul 'low' indicand un ciclu extern de magistrala. In modul HOLD este plasat in inalta impedanta.

/BR: E

Semnal de cerere a magistralei. Este activat cand TMS320C2x solicita accesul la un spatiu din memoria de date externa globala. Semnalul READY va fi activat de dispozitivul extern pentru a indica disponibilitatea memoriei globale de date si a magistralei externe pentru efectuarea transferului.

/HOLD: I

Intrare de oprire. Cand semnal este activat TMS320C2x plaseaza liniile de adrese, date si control in inalta impedanta.

/HOLDA: E

Semnal de confirmare oprire. Indica faptul ca TMS320C2x a trecut in starea hold si dispozitivul extern poate accesa memoria externa locala a lui TMS320C2x.

/SYNC: I

Intrare de sincronizare. Permite sincronizarea ceasului a doua sau mai multor circuite TMS320C2x. /SYNC este un semnal activ 'low' si trebuie activat pe frontul crescator al CLKIN.

/BIO: I

Intrare de control a salturilor prin program. Este interogat de instructiunile BIOZ. Daca /BIO este 'low' se executa saltul. Acest semnal trebuie sa fie activ pe durata ciclului de extragere a instructiunii BIOZ cand TMS320C2x solicita accesul la un spatiu din memoria de date externa globala. Semnalul READY va fi activat de dispozitivul extern pentru a indica disponibilitatea memoriei globale de date si a magistralei externe pentru efectuarea transferului.

/INT2, /INT1, /INT0: I

Intrari externe de intrerupere. Pot fi ierarhizate si mascate prin registrul de mascare a intreruperilor si bitul modului de intrerupere.

/IACK: E

Semnal de acceptare a intreruperilor. Iesirea este valida numai pe durata cat CLKOUT1 este 'low'. Indica receptionarea unei intreruperi si faptul ca programul se va ramifica la locatia vectorului de intreruperi desemnat de A15 . A0.

XF: E

Semnal de iesire (bistabil de conditie) ce poate fi programat soft. Utilizat ca semnal de comunicatie in sisteme multiprocesor sau ca linie de iesire de uz general.

MP/MC: I

Intrare de selectie mod microprocesor/microcalculator.Cand este trecut in 'low' memoria ROM interna este plasata in harta memoriei in primii 4K de adrese (000 . 3FF). In mod microprocesor primii 4K de memorie program sunt mapati in memoria externa.

/MSC: E

Semnal terminare microstare. Este activat 'low' si valid doar pe durata cat CLKOUT1 este 'low' cand TMS320C2x a terminat o operatie cu memoria, de exemplu un ciclu de extragere cod operatie sau un ciclu de citire/scriere din/in memora de date . /MSC poate fi utilizat pentru a genera o stare de asteptare (prin conectare la pinul READY) in cazul lucrului cu memorii lente.

/RS: I

Intrare de initializare, activa 'low'. Determina TMS320C2x sa termine executia instructiunii in curs si forteaza numaratorul de program in 0. Cand este readus in starea 'high' executia incepe de la locatia zero a memoriei program. /RS afecteaza diverse registre si biti de stare.

Vcc: 4 pini de alimentare cu +5V conectati impreuna in exterior

Vss: 3 pini de masa conectati impreuna in exterior.

Pinul de iesire al oscilatorului intern utilizat pentru conectarea cristalului. Daca nu se utilizeaza un cristal acest pin trebuie sa ramana neconectat.

Pinul de intrare al oscilatorului intern utilizat pentru conectarea cristalului. Daca nu se utilizeaza un cristal la acest pin se conecteaza semnalul de ceas.

Semnal de iesire ceas principal (master clock). Are frecventa ¼ din frecventa ceasului de intrare. Trece in 'high' la inceputul fazei 3 (Q3) si revine in 'low' la inceputul fazei 1 (Q1).

Semnal de iesire ceas secundar. Trece in 'high' la inceputul fazei 2 (Q2) si revine in 'low' la inceputul fazei 4 (Q4).

Intrare de ceas pentru receptie. Semnal de ceas extern pentru deplasarea datelor de la pinul DR (receptie date) in registrul de receptie al portului serial RSR. Trebuie sa fie prezent pe durata transferurilor prin portul serial.

Intrare de ceas pentru transmisie. Semnal de ceas extern pentru deplasarea datelor de la registrul de transmisie al portului serial XSR la pinul DX (transmisie date) . Trebuie sa fie prezent pe durata transferurilor prin portul serial. in

Intrare receptie date seriale. Utilizat receptia datelor in registrul de deplasare pentru receptie RSR.

Iesire transmisie date seriale. Datele din registrul de deplasare pentru transmisie XSR sunt scoase la exterior prin intermediul pinului DX. Este plasat in inalta impedanta cand nu se efectueaza transmisie.

Impuls de sincronizare cadru pentru receptie. Frontul cazator al FSR initiaza procesul de receptie incepand transmiterea semnalului de ceas catre RSR.

Impuls de sincronizare cadru pentru transmisie. Frontul cazator al FSX initiaza procesul de transmisie incepand transmiterea semnalului de ceas catre XSR. Dupa reset, FSX este implicit un pin de intrare. Acest pin poate fi programat prin soft ca fiind o iesire cand bitul TXM din registrul de stare este pus pe '1'.

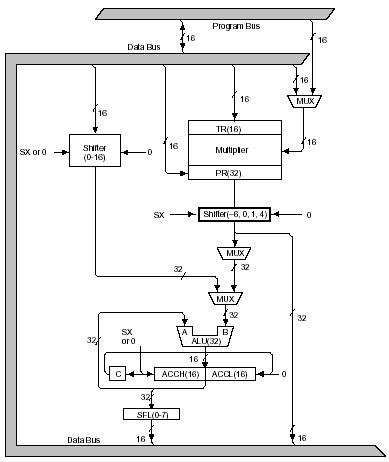

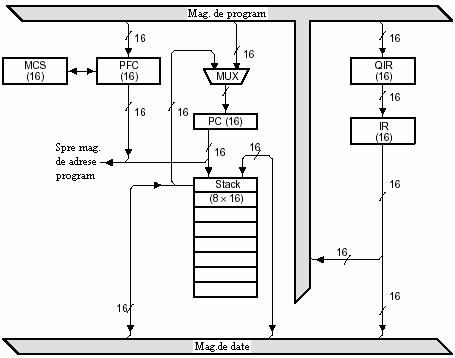

Circuitele DSP implementeaza functii pe care alte procesoare le realizeaza de obicei prin soft sau microcod : inmultire, manevrare adrese, circuite de deplasare a datelor, toate aceste operatii executandu-se intr-un singur ciclu instructiune si de multe ori in paralel cu operatiile ALU. In figura este prezentata schema bloc functionala a TMS320C26.

Fig.3 NOTA:

Zonele umbrite indica magistrale

Fig.3 NOTA:

Zonele umbrite indica magistrale

Arhitectura lui TMS320C2x este construita in jurul a 2 magistrale majore : magistrala de programe si magistrala de date.

Magistrala de program manipuleaza codul instructiunilor si operanzii imediati din memoria program.

Magistrala de date interconecteaza diferite elemente, cum ar fi: CALU(Central Arithmetic Logic Unit) si bancul registrelor auxiliare, la memoria de date RAM. Impreuna, magistrala de programe si de date pot transporta datele de la memoria RAM de pe circuit sau de la memoria externa la multiplicator, intr-un singur ciclu pentru operatii de multiplicare/acumulare. TMS320Cx are un grad inalt de paralelism, adica in timp ce datele sunt prelucrate in CALU alte operatii aritmetice pot fi de asemenea executate in ARAU(Auxiliary Register Arithmetic Unit). Un astfel de paralelism duce la un puternic set de operatii aritmetice, logice si lucru la nivel de bit care pot fi implementate toate intr-un ciclu masina.

4.2.1.Unitatea Aritmetica si Logica Centrala - CALU

Contine un circuit de deplasare si

scalare pe16 biti , un multiplicator paralel pe 16X16 biti, o ALU pe

32 de biti, un acumulator pe 32 biti(ACC) si circuite de

deplasare suplimentare la iesirile acumulatorului si

multiplicatorului(SFL).

Contine un circuit de deplasare si

scalare pe16 biti , un multiplicator paralel pe 16X16 biti, o ALU pe

32 de biti, un acumulator pe 32 biti(ACC) si circuite de

deplasare suplimentare la iesirile acumulatorului si

multiplicatorului(SFL).

In implementarea unei instructiuni tipice a ALU, pasii care apar sunt urmatorii :

1)Data este adusa din RAM pe magistrala de date.

2)Data este trecuta prin circuitul de deplasare in ALU, unde este executata operatia aritmetica.

3)Rezultatul este transferat in acumulator.

O intrare in ALU este intotdeauna furnizata de acumulator, iar cealalta intrare poate fi transferata de la registrul de produs PR al multiplicatorului, sau scalling shifter care este incarcat din memoria de date.

Circuitul de deplasare pe partea de iesire, cu intrare pe 32 biti si iesire pe 16 biti SFL(0-7), este utilizat pentru salvarea si scalarea ACCL sau ACCH.

![]() Multiplicatorul este

realizat din 3 elemente: registrul temporar TR, (16 bit) registrul produs PR

(32 bit) si aria de multiplicatoare care efectueaza inmultirea

intre continutul TR si data

provenita de pe magistrala de date. La iesirea multiplicatorului este prevazut un

Multiplicatorul este

realizat din 3 elemente: registrul temporar TR, (16 bit) registrul produs PR

(32 bit) si aria de multiplicatoare care efectueaza inmultirea

intre continutul TR si data

provenita de pe magistrala de date. La iesirea multiplicatorului este prevazut un  circuit de deplasare SFL-R(-6,0,1,4) care asigura scalarea rezultatului in

functie de modul de efectuare a produsului stabilit prin pozitionarea

bitilor PM din registrul de stare ST1.

circuit de deplasare SFL-R(-6,0,1,4) care asigura scalarea rezultatului in

functie de modul de efectuare a produsului stabilit prin pozitionarea

bitilor PM din registrul de stare ST1.

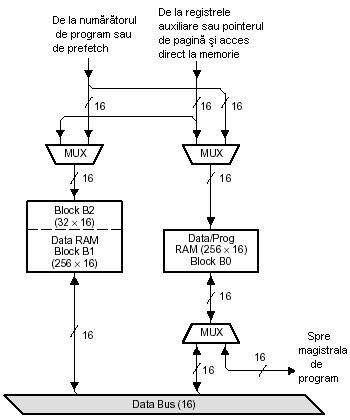

4.2.2.Organizarea memoriei

Memoria de date. Cele544 cuvinte de memorie de date RAM sunt impartite in 3 blocuri separate:

BLOCUL B0:256 cuvinte de memorie RAM, configurabile fie ca memorie de date, fie ca memorie de program, prin instructiuni prevazute in acest scop.

BLOCURILE B1,B2:288 cuvinte; sunt intotdeauna memorie de date.

Memoria de program .Poate fi constituita din memoria RAM de pe circuit, ROM sau memorii externe de program de mare viteza care se folosesc la viteza integrala, fara stari de asteptare. Ca o alternativa ieftina, prin READY se poate asigura adaptarea TMS320C2x la memoriile mai lente si mai ieftine(memorii externe). Este disponibil un spatiu adresabil de memorie de 64 Kcuvinte.

Fig.5 Memoria de date de pe circuit

TMS320C2x suporta 3 spatii separate de adrese de memorie:

-pentru memoria program

-pentru memoria de date

-pentru periferice I/O

Aceste spatii se disting in exterior prin semnalele PS, DS, IS(selectare program, date si I/O).

La TMS320C25, memoria de program ROM de pe circuit este localizata in cele mai putin semnificative 4Kcuvinte de memorie program, cand sunt selectate de MP//MC=0.Cand MP//MC=1, cele mai de jos 4Kcuvinte ale memoriei program sunt externe.

Memoria externa este adresata prin magistrale unice de adrese si de date care multiplexeaza magistralele celor doua spatii de memorie.

Organizarea memoriei este prezentata in fig. 6.

Obs. acest mod de lucru cu blocuri de memorie comutabile este specific la

toate procesoarele TMS 320 .

4.2.3. Registele

Registrele mapate in memorie pot fi accesate in aceeasi maniera ca orice alta locatie de memorie cu exceptia instructiunilor de transfer bloc de date (BLKD)

Pe langa operatiile de calcul a adreselor ARAU poate fi utilizata si ca o unitate aritmetica de uz general care implementeaza operatii aritmetice cu numere pe 16 biti fara semn. De asemenea se pot efectua salturi conditionate prin compararea registrului curent, indicat de ARP cu AR0 (instructiunea BANZ).

TMS320C2x poate adresa 64KW memorie program si 64KW memorie date. Magistrala de Adrese memorie Date (DAB), pe 16 biti, poate adresa memoria intr-unul din urmatoarele moduri:

Prin magistrala de adresare directa (DRB) utilizand modul de adresare directa (de ex. ADD 10h)

Prin magistrala bancului de registre auxiliare (AFB) utilizand modul de adresare indirecta (de ex. ADD *)

Operanzii mai pot fi adresati de catre continutul numaratorului de program in modul de adresare imediata.

In modul de adresare directa cei 9 biti ai pointer-ului de pagina memorie (DP) indica unadin cele 512 pagini de memorie, fiecarea pagina avand128 cuvinte. Adresa pe magistrala de adrese directe (DRB) se formeaza concatenand cei 9 biti ai DP cu cei 7 biti de adresa directa din instructiune (dma).

In modul de adresare indirecta, registrul auxiliar curent (AR), selectat de pointerul registrelor auxiliare (ARP), adreseaza memoria de date prin magistrala bancului de registre auxiliare (AFB). Pe durata in care registrul auxiliar selectat furnizeaza adresa datei de memorie si data este manipulata de CALU, continutul AR poate fi manipulat prin ARAU.

Cand se utilizeaza un operand imediat, acesta este continut fie in cuvantul instructiunii insasi sau, in cazul operanzilor imediati pe 16 biti, in cuvantul ce urmeaza dupa codul instructiun

4.4 Controlul sistemului

Controlul de sistem al procesorului TMS320C2x este asigurat de numaratorul de program(PC), stiva, conexiunile hard, semnalul reset extern,intreruperi, timer si un numarator de repetari. In figura urmatoare se prezinta schema functionala :

Fig.8 Numaratorul de program, stiva si circuitele anexe

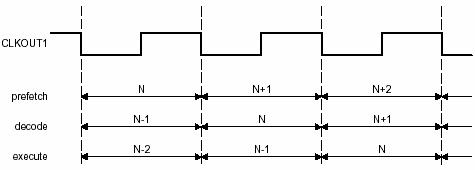

Pipelining-ul instructiunilor consta din secventierea de operatii ale magistralei externe care apar in cursul executiei instructiunIn timpul oricarui ciclu dat doua sau trei instructiuni pot fi active la un moment dat, fiecare in diverse stadii de executie, rezultand in doua respectiv trei nivele de pipeline pentru TMS320C20 si TMS320C25.

Fig.9 Functionarea magistralei pipeline cu trei nivele(TMS320C25)

Mai multe instructiuni sunt executate in acelasi numar de perioade, indiferent daca sunt executate din memoria interna ROM, RAM sau in memoria de program externa.

|

Ciclu |

Faza |

Operatie |

|

Noul PC este depus pe magistrala de adrese Citire externa a instructiunii Citire externa a instructiunii Citire externa a instructiunii |

||

|

Decodarea instructiunii Decodarea instructiunii/Executie in ARAU Acces la memoria RAM/Executie in ARAU |

||

|

Aces la memoria RAM/In carcarea noii valori a registrului auxiliar/Reinnoirea registrului ARP Executie in ALU Executie in ALU Incarcarea acumulatorului |

||

|

Incarcarea registrului de stare |

TMS320CX are trei intrari de

intreruperi (/INT2 /INT0) la care pot fi conectate dispozitivele externe.

Intreruperile interne pot fi generate de portul serial (RINT si XINT), de

temporizatorul intern (TINT) si de prin instructiunea de intrerupere

soft (TRAP). Sistemul de intreruperi este vectorizat, ca raspuns la o

cerere de intrerupere fiind generat un apel la o adresa din memoria

program. Localizarea vectorilor se intrerupere si nivele de prioritate

asociate sunt prezentate in TAB. 1. Cand apare o intrerupere aceasta este

memorata intr-unul din cei 6 biti ai registrului indicatorilor de

intreruperi IFR. Acest registru poate fi inscris de intreruperile externe /INT(2-0) si de intreruperile

interne RINT, XINT si TINT. Fiecare intrerupere este memorata in IFR

pana cand este achitata si stearsa automat de semnalul

/IACK sau de /RS. Nu sunt prevazute instructiuni pentru citirea sau

inscrierea IFR.

TMS320CX are trei intrari de

intreruperi (/INT2 /INT0) la care pot fi conectate dispozitivele externe.

Intreruperile interne pot fi generate de portul serial (RINT si XINT), de

temporizatorul intern (TINT) si de prin instructiunea de intrerupere

soft (TRAP). Sistemul de intreruperi este vectorizat, ca raspuns la o

cerere de intrerupere fiind generat un apel la o adresa din memoria

program. Localizarea vectorilor se intrerupere si nivele de prioritate

asociate sunt prezentate in TAB. 1. Cand apare o intrerupere aceasta este

memorata intr-unul din cei 6 biti ai registrului indicatorilor de

intreruperi IFR. Acest registru poate fi inscris de intreruperile externe /INT(2-0) si de intreruperile

interne RINT, XINT si TINT. Fiecare intrerupere este memorata in IFR

pana cand este achitata si stearsa automat de semnalul

/IACK sau de /RS. Nu sunt prevazute instructiuni pentru citirea sau

inscrierea IFR.

Pentru mascarea intreruperilor TMS320C2x are un registru de mascare a intreruperilor (IMR) mapat in memorie

![]()

Un bit 1 intr-una din pozitiile 5 . 0 valideaza intreruperea corespunzatoare (daca INTM=0). IMR poate fi atat inscris cat si citit.

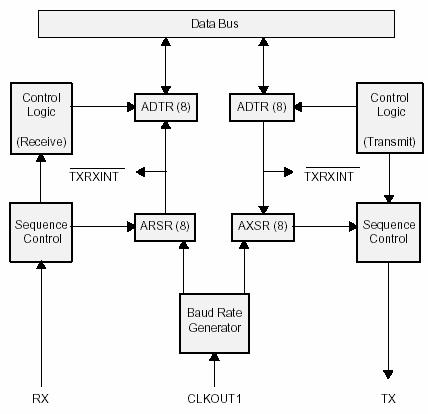

Portul serial este full-duplex si asigura comunicarea cu dispozitivele seriale externe(codec, convertoare A/D seriale). Poate fi folosit la intercomunicarea intre procesoare in aplicatiile multiprocesor.Atat receptia cat si transmisia sunt dublu bufferate la TMS320C25, asigurandu-se un flux continuu de biti.Portul serial are doua registre: DXR ce pastreaza datele ce vor fi transmise si DDR ce pastreaza datele receptionate, la adresele 0000h respectiv la 0001h. Opreratiile de transmisie si receptie sunt implementate separat.Datele de pe liniile DX si DR sunt receptionate sau trimise in XSR sau RSR, pe fronturile CLKX sau CLKR.Pentru a incepe o noua transmisie,continutul registrului DXR este transferat in XSR, iar dupa ce au fost receptionati toti bitii,continutul lui RSR este transferat in in DRR(la TMS320C25).

Copyright © 2025 - Toate drepturile rezervate