| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

PLACA DE DEZVOLTARE MSK2812 CU PROCESOR DE SEMNAL DIGITAL TMS320F2812

DSP - atunci si acum

In anul 1978 Intel a lansat 'prodesorul de semnal anaogic'. Acesta era compus dintr-un chip ADC/DAC cu un procesor de semnal intern dar nu a avut succes pe piata. In anul 1979, AMI a lansat S281. Acesta fusese conceput ca un microprocesor periferic care trebuia initializat de gazda; a fost de asemenea un esec.

In acelasi an, Laboratoarele Bell au lansat primul DSP cu un singur chip (single chip), numit Microprocesorul Mac 4. Dupa aceasta, in 1980, au aparut primele DSP-uri independente NEC µPD7720 si AT&T DSP1 - prezentate la IEEE International Solid-State Circuits Conference '80. Ambele procesoare au fost realizate in urma cercetarii in domeniul telecomunicatiilor PSTN (Public Switched Telecommunications Network).

Primul DSP produs de Texas Instruments, TMS32010 prezentat in 1983, s-a dovedit a fi un succes. Acesta se baza pe aritectura Harvard deci avea memorii separate pentru instructiuni si date. Era dotat cu un set special de instructiuni, putea lucra cu numere de 16 biti si avea nevoie de 390ns pentru o operatie de inmultire prin adunare repetata. Texas Instruments este acum lider de piata in domeniul DSP-urilor. Un alt procesor de succes a fost Motorola 56000.

La apoxiativ 5 ani de la lansarea TMS32010, a doua generatie de DSP-uri s-a extins. Acestea contineau 3 registrii pentru a procesa doua operatii simultan si includeau hardware pentru accelerarea buclelor. Unele DSP-uri puteau lucra cu variabile de 24-biti, iar modelul tipic avea nevoie de 21ns pentru o operatie de multiplicare prin adunari repetate. Membrii acestei generatii au fost: AT&T DSP16A si Motorola DSP56001.

Cea mai mare imbunatatire adusa de a treia generatie a fost aparitia unitatilor si instructiunilor, specifice anumitor aplicatii, in calea de date sau a coprocesoarelor. Aceste unitati permiteau accelerarea hardware directa pentru probleme matematice complexe, cum ar fi transformata Fourier sau operatiile cu matrici. Unele chipuri, ca Motorola MC68356, includeau chiar mai multe nuclee de procesare care lucrau in paralel. Alte DSP-uri din 1995 au fost TMS320C541 sau TMS320C80.

A patra generatie este caracterizata de modificarile aduse setului de instructiuni si modului de codare/decodare a instructiunilor. Au fost adaugate extensiile SIMD si MMX, a aparut arhitectura superscalara VLIW. De asemenea vitezele de procesare au crescut, 3ns erau suficiente pentru o multiplicare.

Procesoarele de semnal digital moderne au furnizat o performanta mult mai ridicata. Aceasta a fost posibila datorita progreselor inregistrate in domeniul tehnologic si cel al arhitecturii procesoarelor cum ar fi: cache pe doua niveluri cu acces rapid, circuit (E)DMA si un sistem de bus mai extins. Este evident faptul ca nu toate DSP-urile ofera aceeasi viteza de procesare. Exista numeroase modele de DSP-uri fiecare dintre acestea fiind potrivit anumitei aplicatii.

DSP - Generalitati

Un DSP (Digital Signal Processor) sau procesor de semnal numeric este un tip de procesor optimizat pentru procesarea rapida (in timp real) a unui flux numeric de natura diversa precum sunet, video etc.

Caracteristici ale unui procesor de semnal numeric

Fig. 1 Sistem simplu de procesare digitala a semnalului.

Procesoarele digitale de semnal pot fi intalnite in aparatele de monitorizare medicale, in aparatele auditive, supercalculatoare sau modemuri. Sunt folosite in detectoare radar, in televizoare digitale sau combine audio, instalatii de amplificare si laser pentru spectacole. DSP-urile sunt, de fapt, o parte componenta a existentei noastre moderne, translatand semnalele in inteligenta si permitandu-ne sa luam decizii mai precise, intr-un timp mult mai scurt.

Arhitectura DSP

Desi exista o multitudine de procesoare DSP, ele contin un set comun de caracteristici care pot fi clasificate in trei categorii: o aritmetica specializata de mare viteza, o capacitate de transfer de date din si catre procesul continuu si o arhitectura de accesare multipla a memoriei.

Functionarea unui DSP consta dintr-un numar de operatii specifice: adunari si multiplicari, intarzieri (delay) si calcul matricial. Fiecare dintre aceste operatii necesita cateva conditii specifice: adunarile si multiplicarile presupun citirea simultana a doi operanzi, executarea operatiilor (de obicei in acelasi timp), salvarea rezultatului sau retinerea lui pentru repetare; intarzierile presupun retinerea unei valori pentru utilizarea sa ulterioara; calculul matricial consta in preluarea datelor din locatii consecutive de memorie sau copierea datelor intre zone diferite de memorie.

Pentru a putea obtine aceste performante obligatorii, procesoarele de semnal trebuie sa ofere posibilitatea efectuarii in paralel a multiplicarii si adunarii, accesarii multiple a memoriei si generarii eficiente a adreselor, sa contina o multitudine de registri de retinere temporara a datelor, precum si facilitati speciale cum ar fi intarzierile si adresarea circulara.

Cele mai multe operatii pe care le efectueaza un DSP constau in multiple adunari si multiplicari. Pentru a citi doi operanzi intr-un singur ciclu de instructiune va trebui sa avem simultan doua accesari ale memoriei. De fapt, gandindu-ne ca va trebui sa salvam rezultatul si sa citim instructiunea insasi, vom dori sa avem mai mult de doua accesari ale memoriei intr-un acelasi ciclu de instructiune. Se stie ca nu se pot accesa doua adrese de memorie diferite pe aceeasi magistrala (bus) de date. Totusi, accesarea multipla este posibila in cazul DSP folosind doua tehnologii derivate din modelele arhitecturale adoptate: arhitectura Harvard sau arhitectura von Neuman modificata.

In arhitectura Harvard, DSP are doua magistrale separate de memorie. Acestea permit accesarea simultana a doua locatii de memorie. In procesoarele de uz general, una dintre magistrale este dedicata citirii codului instructiunii, iar cealalta aducerii operanzilor. Arhitectura Harvard-DSP permite ca magistrala de program sa poata fi folosita pentru citirea operanzilor. Deoarece avem simultan nevoie de trei informatii, Harvard-DSP include o memorie cache care poate stoca instructiunile comune ce vor fi reutilizate, lasand ambele magistrale libere pentru operanzi.

Exista si un dezavantaj al arhitecturii Harvard. Un DSP care proceseaza cuvinte de 32 de biti, la un spatiu de memorie cu adrese de 32 de biti, necesita cel putin 64 de pini pentru fiecare magistrala de date, deci un total de 128 de pini pentru conectarea cu exteriorul. Rezultatul este un cip foarte mare, greu de amplasat in circuite dedicate.

In acelasi timp, chiar si cea mai simpla operatie DSP - o adunare de doi operanzi si o stocare a rezultatului in memorie - necesita patru accesari ale memoriei (trei pentru aducerea operanzilor si instructiunii si o salvare a rezultatului). Depasirea capacitatilor oferite de arhitectura Harvard este realizata, in unele procesoare, prin adoptarea unei alte arhitecturi, denumita von Neuman modificata.

Arhitectura von Neuman foloseste o singura magistrala de memorie. Din acest motiv este mai ieftina (necesitand mai putini pini) si mai simplu de utilizat deoarece programatorul poate plasa instructiuni sau date oriunde in memoria disponibila. In schimb, arhitectura nu permite acces multiplu de memorie. Totusi, structura von Neuman modificata poate permite accesul multiplu intr-un ciclu de instructiune folosind un simplu truc de setare a frecventei de memorie mai ridicata decat cea a ciclului de instructiune.

In ambele cazuri, rolul programatorului este de a administra cu atentie locatiile de memorie unde este amplasata informatia: de exemplu, in cazul arhitecturii Harvard, daca ambii operanzi se gasesc in acelasi banc de memorie, ei nu pot fi accesati simultan.

Hardware intr-un cip

Desi exista multe tipuri de procesoare, majoritatea sunt

proiectate pentru a detine cateva caracteristici

comune. Nucleul arhitecturii DSP este unitatea centrala

de procesare (CPU). Aceasta este alcatuita

din urmatoarele elemente: un multiplicator in virgula fixa sau

mobila, o unitate aritmetica si logica (ALU), un set de registri

si magistralele aferente. Primii opt dintre registri suporta

operatii cu numere in virgula mobila de 40 de biti, sau intregi

de 32 de biti. Urmatorii opt sunt registrii auxiliari a caror

functie principala este generarea adreselor

de memorie. Doi registri aritmetici auxiliari pot genera

doua adrese intr-un singur ciclu de tact, functionand in paralel cu

multiplicatorul si ALU. Ceilalti registri sunt denumiti

registri de control, avand acces la o multitudine de functii:

adresare, managementul stivelor, intreruperi etc.

In cipul DSP se afla un

controler DMA (Direct Memory Access). Acesta este

capabil sa citeasca si sa scrie in orice locatie de

memorie fara a intrerupe functionarea CPU-ului. Controllerul DMA are propriile sale generatoare de adrese, registrii

sursa si destinatie, un numarator de transfer si

un mecanism de raspuns la intreruperi.

Comunicatia DSP cu exteriorul se efectueaza printr-o serie de module periferice, accesate prin registrii speciali de memorie si amplasate pe o magistrala dedicata. Cele mai importante module periferice sunt timerele si porturile seriale, insa ele pot fi extinse in functie de aplicatie si sistemul in care DSP-ul este integrat. Timerele contin cate un pin bidirectional care poate fi folosit ca intrare de ceas, sau ca semnal de iesire controlat de timer. Pinii porturilor seriale sunt configurabili pentru a indeplini functii generale de intrare-iesire.

Contactul cu realitatea

Pe langa calcule matematice, in practica, procesorul digital de semnal trebuie sa comunice cu lumea reala. Intr-o aplicatie DSP tipica, procesorul va trebui sa prelucreze date provenite de la multiple surse.

El va trebui sa poata primi si transmite date in timp real, fara a-si intrerupe calculele matematice interne. Majoritatea aplicatiilor DSP implica tratarea semnalelor analogice. Acestea trebuie convertite in forma digitala (cu ajutorul unor convertoare A/D), intr-o secventa discreta de valori masurabile. O buna parte din informatie este pierduta la conversia analog - digitala datorita impreciziei de masurare, inacuratetei in sincronizare, limitari ale duratei de efectuare a masurarii. Aceste efecte sunt numite erori de cuantizare.

Semnalul continuu, analog, trebuie sa fie retinut inainte de a fi esantionat. Altfel s-ar putea modifica in timpul masurarii. Dupa ce a fost retinut, semnalul va fi masurat si apoi convertit intr-o valoare digitala. Prin esantionare obtinem o multime de numere in format binar ce reprezinta marimi ale semnalului, luate de obicei la intervale constante de timp.

Exista trei moduri de interactiune a DSP-ului cu lumea reala: prin semnale care sunt receptionate si transmise direct, prin comunicarea cu un sistem de control de tip diferit sau prin comunicarea cu alte procesoare DSP de acelasi tip. Aceste cai de comunicatie multiple marcheaza cea mai importanta distinctie dintre procesoarele DSP si procesoarele obisnuite.

Sistemele care contin DSP trebuie sa functioneze in timp real, capturand si procesand informatia pe masura ce se schimba. Mai intai convertoarele analog - digitale trebuie sa tina pasul cu modificarile continue ale datelor reale. Daca raman in urma, informatia se pierde, iar semnalul este distorsionat. Convertorul A/D "fotografiaza" semnalul la intervale suficient de mici pentru a observa fluctuatiile relevante, iar DSP efectueaza toate calculele necesare pana in momentul in care o noua "fotografie" apare pentru a fi procesata. Semnalul audio stereo trebuie prelucrat la frecvente de pana la 20 kHz (20.000 de cicluri pe secunda), obligand DSP-ul sa realizeze sute de milioane de operatii pe secunda. Alte semnale, cum ar fi transmisiile prin satelit, sunt si mai rapide, ajungand la ordinul gigahertzilor (miliarde de cicluri pe secunda).

Pimele procesoare DSP aparute pe piata erau destul de rapide: de exemplu primul DSP - AT&T DSP32 - functiona la 16 MHz, in perioada in care frecventa procesoarelor din PC-uri era de 5 MHz. Intr-o demonstratie a superioritatii de viteza a DSP, celebra la vremea respectiva, un calcul de fractal (Mandelbrot) era rulat in paralel pe un PC obisnuit si pe unul in care se introdusese o placa cu DSP. Astazi, insa, cel mai rapid procesor DSP este cel produs de Texas Instruments, TMS 320C6201, care ruleaza la 200 MHz. Evident, nu este cel mai rapid in comparatie cu un microprocesor obisnuit, iar acelasi fractal va rula astazi mai repede pe un PC decat pe un DSP. Totusi, de ce procesoarele DSP prezinta inca un atat de mare interes? Motivatia este dubla: in primul rand DSP poate efectua mai multe operatii in paralel si, mai ales, poate lucra cu semnale externe mult mai bine decat cel mai performant Pentium.

Avantajele proiectarii cu DSP sunt multiple, dintre care putem aminti:

Cost - Cu un hardware foarte simplu, in absenta unor elemente electronice sofisticate, si cu un chip DSP cu pretul intre 2$ si 100$ pentru performante variind intre 10 MFLOPS (FLoating point Operations Per Second) pana la 500 MFLOPS, putem construi dispozitive cu o putere de procesare extrem de mare.

Fiabilitate - Orice circuit electronic este supus modificarilor de performanta, datorate variatiilor termice, imbatranirii, care pot duce la o functionare incorecta. Un DSP, insa, va putea sa functioneze perfect in urmatorii 50 de ani.

Flexibilitate - Prin folosirea tehnologiei DSP putem concepe un produs cu o anumita functie, care, printr-o modificare de software, se transforma intr-un cu totul alt produs, cu noi functionalitati. Poate ca ati avut ocazia sa folositi un simplu modem care incearca sa fie, la inceput, unul foarte rapid, dupa care isi incetineste rata de transfer pana cand ajunge la o viteza convenabila pentru comunicarea pe liniile RomTelecom. In realitate software-ul este reconfigurat in timp real, astfel incat vom avea succesiv mai multe modemuri (si o factura mai mare catre operatorul de telefonie).

DSP TMS320F2812 Texas Instruments

Familia TMS320 este alcatuita din procesoare digitale de semnal (DSP) in virgula mobila si in virgula fixa. Arhitectura TMS320 este destinata in special pentru procesare de semnal in timp real. Posibilitatea de procesare in timp real a TMS320 impreuna cu perifericele controllerului ofera o solutie optima pentru sistemul de control al aplicatiilor. Urmatoarele caracteristici face ca familia TMS320 sa fie o buna alegere pentru procesarea unei game largi de aplicatii:

setul de instructiuni foarte flexibil

performante la viteze mari

flexibilitate in operare

cost redus.

Structura DSP-ului TMS320F2812

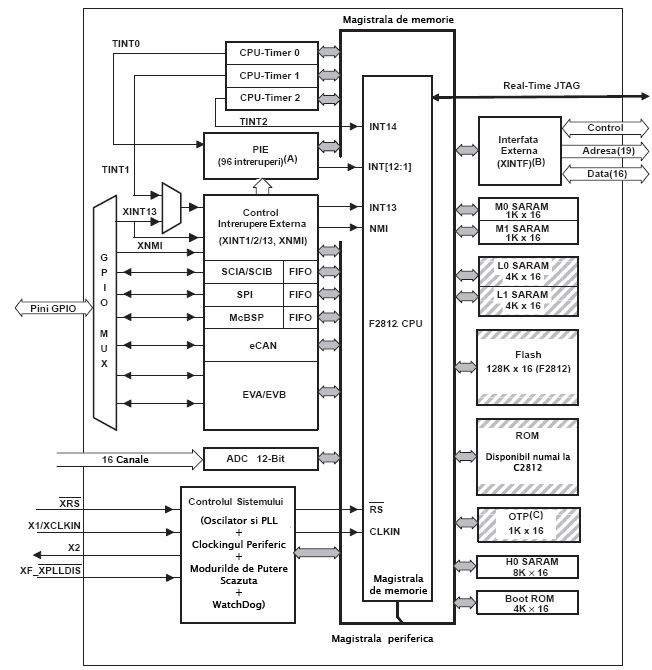

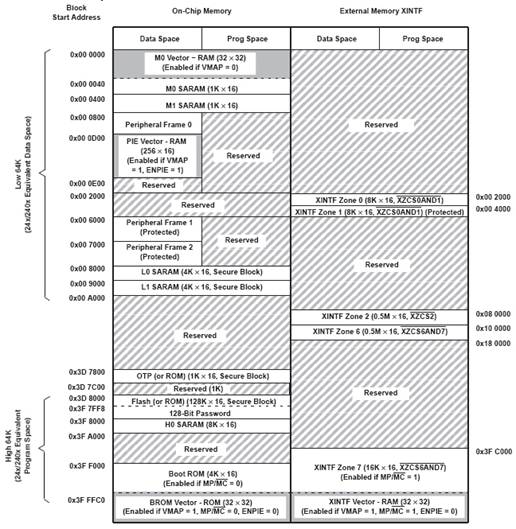

Structura DSP-ului TMS320F2812 este prezentata in figura 2. Structura memoriei DSPului TMS320F2812 este prezantata in figura

Generatia DSP F281x este membra a familiei TMS320 produsa de Texas Instruments. Procesorul F2812 este compatibil din punct de vedere al codului sursa cu dispozitivele DSP 24x/240x. In plus, procesorul F2812 este un motor C/C++ foarte eficient, permitand utilizatorilor sa dezvolte, pe langa aplicatiile de control al sistemului, si algoritmi matematici complecsi. Procesorul F2812 este la fel de eficient in dezvoltarea sarcinilor matematice cat este si in dezvoltarea aplicatiilor tipice de control al sistemelor. Capacitatea 32x32-bit MAC a F2812 cat si capacitatea de procesare pe 64biti, permit acestuia sa trateze probleme care in mod mormal ar necesita un procesor in virgula mobila, mult mai scump. Adaugand la aceasta si respunsul rapid la cererile de intrerupere cu salvarea automata a contextului registilor critici, va rezulta un dispozitiv pregatit sa intretina o multitudine de evenimente asincrone cu latenta minima.

F2812 contine un pipeline protejat de 8 nivele adancime cu acces la memorie. Acest sistem permite executia aplicatiilor la viteze ridicate fara a necesita memorii scumpe.

Fig. 2 Structura DSP-ului TMS320F2812 de la Texas Intruments

Magistrala de memorie

F2812 utilizeaza multiple magstrale pentru a deplasa datele intre memorii, CPU si periferice. Arhitectura magistralelor de memorie contine o magistrala a programului citit, o magistrala a datelor citite cat si o magistrala a datelor scrise.

Magistrala programului citit consta in 22 de linii de adresa si 32 de linii de date. Magistralele de date citite, respectiv scrise constau fiecare in 32 de linii de adresa si 32 de linii de date. Magistrala de date de 32 de biti permite operatii pe un singur ciclu de 32 de biti. Arhitectura magistralelor multiple, denumita "Arhitectura Harvard", permite procesorului F2812 extragerea unei instructiuni, citirea unei date si scrierea unei date intr-un singur ciclu. Toate perifericele si memoriile atasate magistralei de memorie vor avea o anumita prioritate in accesarea memoriei. In general prioritatile pot fi insumate dupa cum urmeaza:

|

Cea mai mare prioritate: |

- Scrierea de date (scrierea simultana a datelor si programului nu poate aparea) |

|

- Scrierea programului - Citirea de date - Citirea programului(nu se pot executa simultan citirea programului si extragerea unei instructiuni) |

|

|

Cea mai mica prioritate: |

- Extragerea instructiunilor |

Fig. 3 Structura memoriei DSP-ului TMS320F2812

Magistrala perifericelor

Texas Instruments a stabilit un standard pentru magistrala perifericelor a DSP-urilor din familiile F281x si C281x. Magistrala perifericelor multiplexeaza diferitele magistrale care formeaza "Magistrala de Memorie" a procesorului intr-o singura magistrala constand in 16 linii de adresa si 16 sau 32 linii de date si semnale de control asociate. C281x si F281x suporta doua versiuni de magistrale periferice. O versiune suporta accesul numai pe 16biti (denumita si frame-ul periferic 2). Cealalta versiune suporta si accesul pe 16 biti si pe 32 biti (denumita si frameul periferic 1).

JTAG in timp real si Analiza

F281x si C281x implementeaza interfata JTAG (Joint Test Action Group) 1149.1 din standardul IEEE. In plus acestea suporta modul de operare in timp real (real-time) prin intermediul caruia continutul memoriei, perifericelor si locatiile registrilor pot fi modificate in timp ce procesorul functioneaza, executa cod si serveste intreruperile. F281x si C281x implementeaza hardware modul real-time in cadrul procesorului. Aceasta este o caracteristica unica a DSP-urilor C281x si F281x, nu este necesar un monitor software. In plus, este furnizat si un hardware de analiza speciala care permite utilizatorului setarea punctului de intrerupere hardware sau a punctelor de urmarire a datelor sau adreselor si generarea evenimentelor de intrerupere.

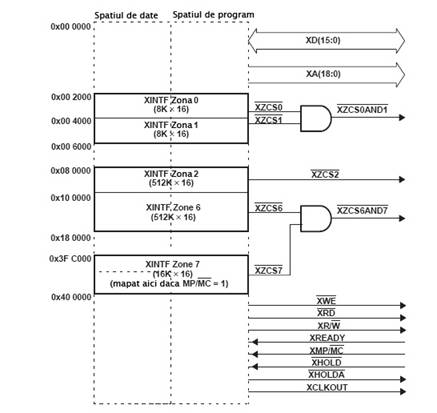

Interfata Externa (XINTF)

Aceasta interfata asincrona consta in 19 linii de adresa, 16 linii de date, si 3 linii de chip-select. Aceste 3 linii sunt mapate in cinci zone externe, Zonele 0, 1, 2, 6 si 7. Zonele 0 si 1 impart o singura line chip-select, Zonele 6 si 7 de asemenea impart o singura linie. Fiecare dintre aceste cinci zone poate fi progamata cu un numar diferit de stari de asteptare, setup pentru semalul de strobe si fiecare zona poate fi programata pentru stari de asteptare externe sau nu.

Flash

F2812 contin 128K x 16 chipuri de memorie flash intergrate, izolate in sectoare 8K x 16, si sase sectoare 16K x 16. De asemenea acesta contine o singura memorie OTP 1K x 16 in banda de adrese 0x3D 7800 - 0x3D 7BFF. Utilizatorul poate sterge, programa si valida un sector de memorie flash in timp ce restul de sectoare raman nemodificate. Totusi, nu este posibila utilizarea unui sector de flash sau OTP-ul pentru executarea algoritmilor flash care sterg sau prtogrameaza alte sectoare de flash. Pepelining-ul special de memorie este furnizat pentru ca modulul de memorie sa atinga o performanta ridicata. Flash-ul/OTP-ul sunt mapate in spatiile de program si date; in consecinta poate fi utilizata la executarea codului si stocarea informatiilor.

SARAM L0, L1, H0

F281x contine in plus o memorie RAM 16K x 16 cu acces singular, impartita in 3 blocuri (4K + 4K + 8K). Fiecare bloc poate fi accesat independent, in consecinta se obtine minimizarea dimensiunii pipeline-urilor. Fiecare bloc este mapat in spatii de date si de program.

ROM-ul de Boot

ROM-ul de boot este programat din fabrica cu un soft-ware de incarcare la boot. Programul de boot din ROM se executa dupa ce dispozitivul a fost resetat si verifica pinii de GPIO pentru stabilirea modului de boot. De exemplu, userul poate alege sa execute codul care exista deja in flash-ul intern sau sa downloadeze un nou software in memoria interna RAM, prin intermediul porturilor seriale. Exista de asemenea si alte moduri de boot. ROM-ul de boot contine de asemenea functii standard, cum ar fi forme de unda SIN/COS, pentru utilizarea in algoritmii matematici.

Securitate

F281x suporta niveluri ridicate de securitate pentru a proteja utilizatorul firmware-ului. Acesta accepta o parola de 128-biti, pe care userul o poate programa in flash. Un modul de securitate (CSM) este utilizat pentru protejarea flash-ului/ROM/OTP si a blocurilor L0/L1/SARAM. Caracteristica de securitate previne examinarea contiutului memoriei de catre useri neautorizati prin intermediul portului JTAG, executand codul din memoria externa. Pentru a avea acces la blocurile de memorie, userul trebuie sa scrie corect valoarea parolei de 128-biti, care se potriveste cu valoarea stocata in locatiile de parola din Flash-ROM.

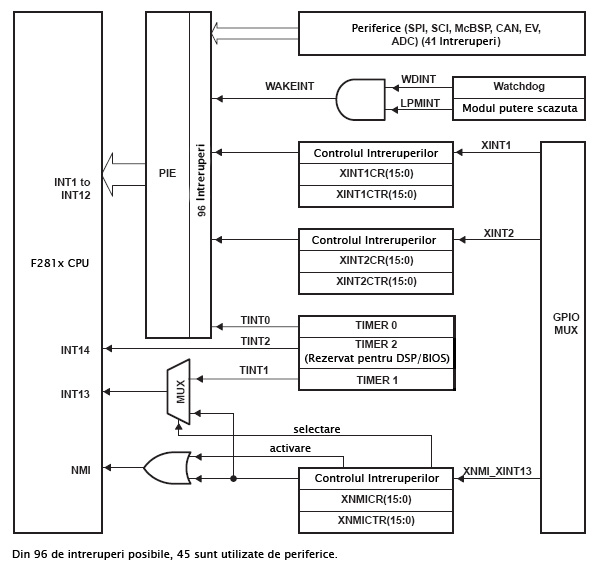

Blocul de expansiune a intreruperilor periferice (PIE - Peripheral Interrupt Expansion)

Blocul PIE serveste la multiplexarea numeroaselor surse de intreruperi intr-un set restrans de intrari. Blocul PIE poate suporta pana la 96 de intreruperi. In cadrul procesorului F281x dintre cele 96 de intreruperi 45 sunt utilizate de periferice. Cele 96 de intreruperi sunt grupate in 8 blocuri, si fiecare bloc contine de la 1 la 12 linii de intrerupere (INT1 - INT12). Fiecare dintre cele 96 de intreruperi este sustinuta de propriul vector stocat intr-un bloc RAM dedicat care poate fi suprascris de utilizator. Vectorul este extras automat de CPU cand apare intreruperea. Sunt necesare opt cicluri de ceas de CPU pentru a extrage vectorul si a salva registri critici. In concluzie procesorul poate raspunde repede evenimentelor de intrerupere. Prioritatile intreruperilor sunt controlate atat hardware cat si software. Fiecare intrerupere individuala poate fi activata/dezactivata in blocul PIE.

Intreruperi externe

F281x suporta trei intreruperi externe mascate (XINT1, 2, 13). XINT13 este combinata cu o intrerupere externa nemascata (XNMI). Numele semnalului combinat este XNMI_XINT1 Fiecare dintre intreruperi poate fi selectata pentru lansarea pe frontul pozitiv sau negativ, si de asemenea poate fi activata sau dezactivata (inclusiv XNMI). Intreruperile mascate contin de asemenea un numarator crescator liber pe 16 biti, care este resetat la zero in momentul in care frontul de intrerupere valid este detectat.

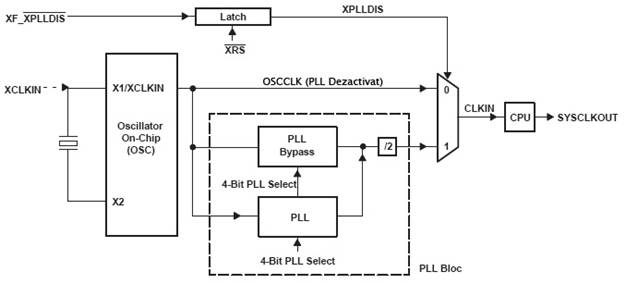

PLL-ul si Oscilatorul

F281x poate fi sincronizat de un oscilator extern sau de un cristal atasat de circuitul oscilator de pe chip. De asemenea este furnizat si un PLL care suporta pana la 10 rapoarte de scalare a clock-ului. Rapoartele PLL pot fi modificate software, permitand utilizatorului sa micsoreze frecventa de operare, daca se doreste efectuarea operatiilor de putere scazuta. Blocul PLL poate fi setat in modul bypass. Figura 4 ilustreaza oscliatorul si blocul PLL.

Fig. 4 OCS si blocul PLL

Circuitul oscilator on-chip permite atasarea unui cristal la F281x prin intermediul pinilor X2 X1/XCLKIN. Daca acesta nu este utilizat atunci se poate conecta direct un oscilator extern la pinul XCLKIN in timp ce X2 ramane neconectat.

Wachdog

F281x suporta un timmer wachdog. Softwareul utilizator trebuie sa reseteze regulat numaratorul wachdog intr-o anumita perioada de timp; altfel wachdog-ul va genera semnale de reset ale procesorului. Acesta poare fi dezactivat daca este necesar.

Clocking-ul perifericelor

Clock-ul fiecarui periferic in parte poate fi activat/dezactivat in scopul reducerii consumului de energie daca perfericul nu este utilizat.

Module de putere scazuta

Dispozitivele F281x sunt dispozitive CMOS in intregime statice. Sunt furnizate trei module de putere mica.

IDLE: Plaseaza CPU-ul in modul low-power. Ceasurile periferice sunt oprite sectiv si numai acele periferice care trebuie sa functioneze pe perioada de IDLE sunt lasate in fuctiune. O cerere de intrerupere provenita de la un periferic poate scoate procesorul din modul IDLE.

STANDBY: Se opresc ceasurile procesorului si ale perifericelor. Acest mod pastreaza in functiune oscilatorul si PPL-ul. Un eveniment de intrerupere din exterior va scoate din aceasta stare procesorul si perifericele. Executia va incepe la urmatorul ciclu valid dupa detectarea evenimentului de intrerupere.

HALT: Scoate din functiune oscilatorul intern. Acest mod practic opreste dispozitivul si il plaseaza modul cu cea mai mare economie de energie. Numai reset-ul poate repune in functiune dispozitivul din acest mod.

Frameuri Periferice 0, 1, 2 (PFn)

F281x imparte perifericele in trei sectiuni. Maparea perifericelor este uratoarea:

PF0: XINTF: Registri de configurare a interfetei externe.

(external INTerFace configuration registers)

PIE: Activarea intreruperii PIE si Control Registers Plus PIE Vector Table.

FLASH: Controlul Flash, Programare, Stergere, Verificarea Registrilor.

Timere: Timerele de procesor 0, 1, 2, Registri.

CMS: Code Securit Module KEY Registers.

PF1: eCAN: Mailbox-ul eCAN si Registri de control.

PF2: SYS: Registri de control al sistemului (System Control Registers).

GPIO: Configuratia MUX a GPIO si Registrii de Control.

EV: Managerul de Evenimente si Registrii de Control.

McBSP: Controul McBSP si Registrii TX/RX.

SCI: Controlul Interfetei de comunicare seriala (Serial

Communications Interface) si registrii RX/TX.

SPI: Controlul Interfetei Periferice Serialeb (Serial Peripheral Interface) si registrii RX/TX.

ADC: Regitrii ADC(Convertor Analogic Digital) de 12 biti.

Multiplexorul Intrarilor/Iesirilor cu Scop General (GPIO - General-Purpose Input/Output)

Majoritatea semnalelor de intrare/iesire sunt multiplexate prin intermediul semnalelor GPIO. Aceasta mutiplexare permite utilizarea unui pin ca un GPIO daca semnalul perferic sau functia nu sunt utilizate. La reset, toate GPIO sunt configurate ca si intrari. Utilizatorul poate programa individual fiecare prin pentru modul GPIO sau pentru modul semnalelor periferice.

Timerele de 32 de biti ale procesorului (0, 1, 2)

Timerele procesorului 0, 1, 2 sunt timere de 32 de biti identice, cu perioade presetabile si cu prescalare de 16 biti de clock. Timerele au un registru numarator descrescator de 32 de biti, care genereaza o intrerupere atunci cand acesta ajunge la valoarea 0. Numaratorul este decrementat la viteza de clock a procesorului impartita la valoarea setata pentru prescalare. Atunci cand numaratorul ajunge a valoarea zero, acesta este automat incarcat cu o valoare de 32 de biti. Timerul 2 este rezervat pentru Sistemul de Operare in Timp Real DSP/BIOS, si este conectat la INT14 a CPU-ului. Daca DSP/BIOS nu este utilizat, Timerul 2 este disponibil. Timerul 1 este pentru uz general si se poate conecta pe INT13 a CPU-ului. Timerul 0 este de asemenea pentru uz general si este conectat la blocul PIE.

Perifericele de Control

F281x suporta urmatoarele periferice utilizate pentru control si comunicatie:

EV: Modulul Manager de Eveniment(Event Manager) include timere de uz general, unitati de comparare/PWM, intrari de captura (CAP) si circuite QEP (quadrature-encoder pulse). Sunt furnizate doua managere de evenimente care permit controlul a doua motoare trifazate sau a patru motoare bifazate.

ADC: Blocul ADC este un convertor pe 12 biti, cu o singura iesire, si 16 canale. Acesta contine doua unitati esantion-si-asteptare (sample-and-hold) pentru esantionari simultane.

Perifericele Portului Serial

F281x suporta urmatoarele periferice pentru comunicarea seriala:

eCAN: Aceasta este versiunea dezvoltata a perifericului CAN. Suporta 32 de mailboxes, si de asemenea este compilator de CAN 2.0B.

McBSP: Multichannel buffered serial port conecteaza la liniile E1/T1 codec-uri phone-quality pentru aplicatiile de modem sau pentru dispozitivele DAC audio-stereo. Registrii McBSP de receptie si transmitere sunt suportati de o FIFO de 16 nivele.

SPI: SPI este un port I/O serial asincron, de mare viteza care permite mutarea in interiorul si in afara dispozitivului a unui sir serial de biti de lungime programabila, la o rata de transfer programabila. In mod normal, SPI-ul este utilizat pentru a realiza comunicatia intre controllerul DSP si perifericele externe sau alt procesor.

SCI: Interfata de comunicare seriala este un port serial asincron, denumit UART. Portul suporta o FIFO de 16 nivele pentru receptie si transmisie.

Interfata externa, (XINTF)

Interfata externa este o magistrala asincrona ne-multiplexata. Interfata externa este mapata in cinci zone fixe ilustrate in figura 4. Aceasta prezinta semnalele XINTF (eXternal INTerFace) pentru procesorul F2812.

Fig. 5 Diagrama bloc a interfetei externe

Intreruperi

Figura 5 ilustreaza variatele surse de intreruperi multiplexate in cadrul dispozitivului F2812.

Opt intreruperi solicitate de blocul PIE sunt grupate intr-o singura intrerupere a CPU. In total, 12 grupuri de intrerupere, cu 8 intreruperi pe grup rezulta 96 posibile intreruperi. In cazul procesorului F281x, 45 dintre acetea sunt utilizate de periferice.

Fig. 6 Surse de intreruperi.

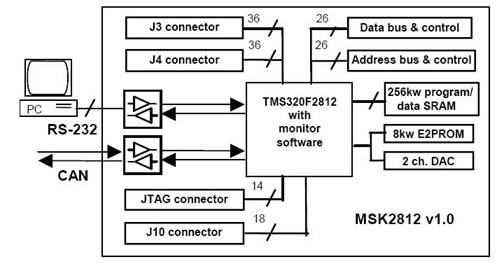

Placa de dezvoltare MSK2812 - Technosoft

Acest subcapitol furnizeaza informatii asupra placii MSK2812 cat si asupra urmatoarelor kituri de dezvoltare:

Platforma de dezvoltare MSWIN2812

Libraria Matlab Simulink DMCode-MS(BL).

Aceste kituri se bazeaza pe placa DSP MSK2812 si permit experimentarea si utilizarea controllerului DSP TMS320F2812 ('F2812) pentru aplicatii de control digital (DMC).

Controlerul DSP F2812 este un dipozitiv de tensiune mica, 3V, conceput pentru implementarea aplicatiilor DMC avansate, prin integrarea unui nucleu DSP performant, descris in subcapitolul 3, si a perifericelor on-chip ale microcontrolerului pe un singur chip. F2812 are toate perifericele necersare pentru controlul simultan a doua motoare alternative trifazate.

Hardware Placa MSK2812

Figura 7 prezinta schema bloc a placii DSP MSK2812. Placa include o interfata RS-232, utilizata pentru comunicarea cu PC-ul si un emitator-recepror CAN care permite conectarea mai multor placi DSP MSK2812 prin intermediul retelei CAN.

Placa DSP MSK2812 este echipata cu o memorie SRAM de 256-kword externa care poate fi utilizata fie ca memorie de date, fie ca memorie de program, si un E2ROM serial de 8kword conectat-SPI. Pentru evaluarea performantei si depanare MSK2812 include un convertor D/A serial pe 12biti cu doua canale conectat-SPI cu update simultan.

Conectorul JTAG ofera compatibilitate cu toate programele ce utilizeaza emulatorul XDS510 sau XDS510PP.

Placa DSP MSK2812 ofera acces direct la toate semnalele I/O ale F2812 prin intermediul celor 4 conectori. Doi dintre ei contin magistrala de date, magistrala de adresa si semnalele de control necesare pentru adaugarea unor noi interfete. Celalti doi conectori sunt utilizati in interfatarea cu modulele de alimentare. Fiecare dintre acesti conectori includ toate semnalele I/O necesare comenzii motoarelor de curent alternativ, de curent continuu si a celor pas-cu-pas. Prin intermediul acestor conectori placa DSP MSK2812 poate fi conectata la una sau doua module de putere externe de tipuri si puteri diferite, adaptate anumitor aplicatii.

Fig. 7 Diagrama bloc a placii MSK2812.

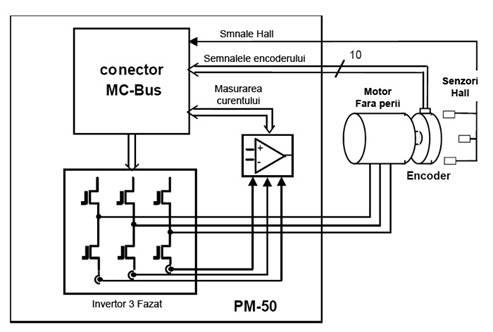

In figura 8 este reprezetata conectarea placii MSK2812 la modulul de putere PM50, utilizand unul dintre acesti conectori.

Fig. 8 Diagrama bloc a modului de putere PM50.

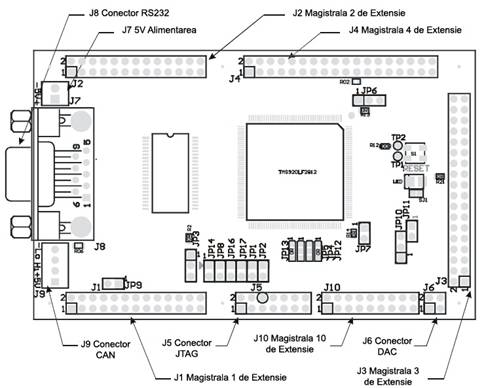

Figura 9 ilustreza placa MSK2812 cu conectorii specifici acesteia.

Fig. 9 Conectorii placii MSK2812.

Software Placa MSK2812

Platforma de dezvoltare MSWIN2812

Placa MSK2812 contine mai multe aplicatii software, ce constituie o platforma de dezvoltare numita MSWIN2812.

Aceasta platforma intergreaza un program de monitorizare a comunicatiei, cat si aplicatii de evaluare a controllerului DSP F2812. Utilizand modulul de comunicatie cu PC-ul, se poate accesa palaca MSK2812, se pot evalua aplicatiile si se pot executa progarame pe paca.

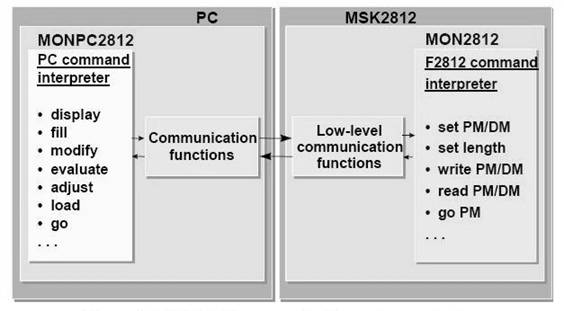

MON2812 - programul monitor al placii DSP MSK2812 - utilizeaza interfata SCI a F2812 pentru comunicatia seriala cu PC-ul.

Programul este structurat pe doua nivele:

Monitorul MONPC2812 - interpretorul comenzilor din programul implementat pe PC, care permite: afisarea continutului memoriei de date si memoriei program, scrierea in aceste memorii, modificarea continutului memoriei de proram si al memoriei de date, evaluarea continutului memoriei de date, ajustarea continutului memoriei de date, modificarea protocolului de comunicare, incarcarea programelor in memoria RAM sau in memoria flash, executarea programelor, etc.

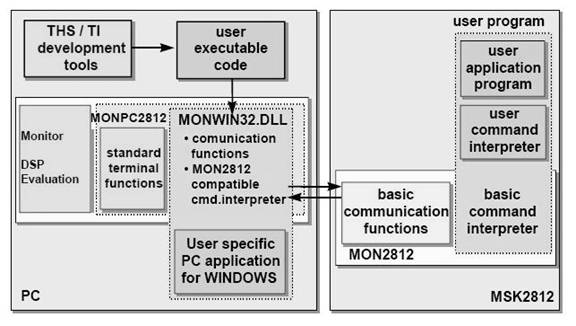

Fig. 9 Structura programelor de comunicatie de baza.

MONWIN32.DLL Toate functiile de comunicatie ale Monitorului MONPC2812 sunt incluse intr-un fisier .DLL denumit monwin32.dll. Acesta permite definirea aplicatiilor Windows care pot apela oricare dintre functiile de comunicatie disponibile.

Fig.

10 Structura software a comunicatiei intre PC si MSK2812.

Fig.

10 Structura software a comunicatiei intre PC si MSK2812.

MSK2812 include platforma DMC28x Developer Pro un mediu Windows IDE care ofera posibilitatea asamblarii si depanarii codului C, functii trace bazate pe achizitia datelor in timp real, plug-in-uri specifice controlului digital al motoarelor, cum ar fi generatorul de referinta, windows watch, panoul de control, etc.

DSPMOT este un instrument de analiza in mediu grafic integrat pentru aplicatiile DSP. Ofera posibilitatea analizarii variabilelor programului DSP utilizand observatoarele on-line sau urmarirea off-line a datelor stocate in timp real.

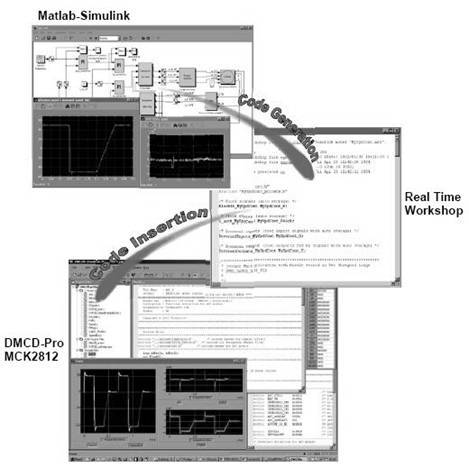

Libraria DMCode-MS(BL) pentru Matlab Simulink

Aceasta se poate utiliza pentru implementarea schemei de reglare a motorului in Matlab Simulink, pentru a simula reglarea si pentru a obtine rezultate in conditii teoretice. Odata ce simularea a fost realizata modelul poate fi testat pe Kitul DMC Developer Pro MSK2812 de la Tehnosoft.

Figura 11 ilustreaza procesul de implementare a aplicatiilor DMC, de la simularea software pana la implementarea DSP.

Fig. 11 Procesul de implementare a aplicatiilor DMC, de la simularea software pana la implementarea DSP.

Aceasta librarie permite:

pornirea cu un model complet al sistemului;

conceperea blocurilor de control si analizarea comportamentului prin intermediul simularii;

generarea automata a codului executabil pentru sitemul de control;

testarea pe un sistem real.

Simularea sistemului

In primul nivel, libraria Matlab DMCode-MS(BL) permite simularea unui intreg sistem de control digital al motorului fara perii. Sunt furnizate blocuri pentru: motor (motor sincron, motor fara perii si motor de inductie), senzori, converoare de putere, cat si pentru structurile de control digital.

Generarea Codului C

Odata ce sistemul a fost simulat, si s-au obtinut rezultate satisfacatoare se poate trece la urmatorul nivel: generarea codului C C++ pentru blocurile de control ale sistemului cu scopul de a-l implementa si testa pe controlerul DSP F2812. Pentru generarea codului se utilizeaza unealta Real Time Workshop din mediul Matlab. Selectand o componenta a schemei de control, si apoi alegand optiunea Build Subsystem, se poate genera codul C, care poate fi folosit in sistemul de control in timp real.

Implementarea Aplicatiei DSP in timp real

Codul generat in Matlab este introdus intr-o aplicatie de intreruperi in timp real, care poate fi executata pe un controler DSP TMS320F2812. Utilizand platforma IDE Digital Motor Control Developer PRO (DMCD-Pro), se pot descarca si rula aplicatiile in mediul real de control digital.

In acest moment se pot compara rezultatele obtinute de la simularea sistemului cu cele obtinute in cazul aplicatiei in timp real.

Copyright © 2026 - Toate drepturile rezervate