| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Convertorul analog numeric

1. Prezentare generala

Multe dintre microcontrolerele familiei ATMEL AVR, ca si ale altor producatori, includ pe chip un convertor analog numeric (ADC) pentru cuplarea cu surse de semal analogice. Principalele caracteristici ale acestui bloc sunt urmatoarele:

Convertorul

analog numeric este cu aproximatii succesive, de 10 biti. Intrarea sa este

cuplata la un multiplexor analogic de 8 canale, care permite ca fiecare pin al

portului A sa poata fi utilizat ca intrare pentru ADC. Este prevazut de

asemenea un circuit Sample and Hold (esantionare si mentinere) care asigura ca

tensiunea de intrare in ADC este mentinuta

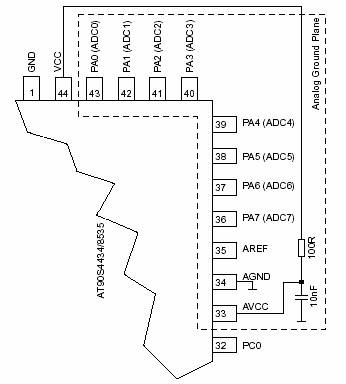

Sunt prevazuti doi pini de alimentare separati AVcc si AGND. AGND trebuie conectat cu GND (intr-un singur punct) iar AVcc nu trebuie sa difere de Vcc cu mai mult de ± 0,3 V. Detalii suplimentare despre conectarea acestor pini vor fi date la paragraful "Tehnici de reducere a zgomotului la ADC".

Pe pinul AREF trebuie aplicata o tensiune de referinta externa. Aceasta trebuie sa fie in domeniul AGND.. AVcc.

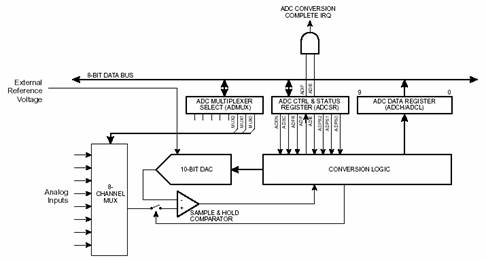

Figura 10.1 -Schema bloc a convertorului analog numeric

2. Functionarea ADC

Convertorul analog numeric poate functiona in doua moduri: 'Single Conversion' (o singura conversie) si 'Free Run' (Conversie continua). In modul Single Conversion, fiecare conversie trebuie sa fie initiata de utilizator. In modul Free Running convertotul analog numeric esantioneaza semnalul si reactualizeaza registrul de date al ADC in mod continuu. Selectia unuia din aceste doua moduri se face prin bitul ADFR din registrul ADCSR.

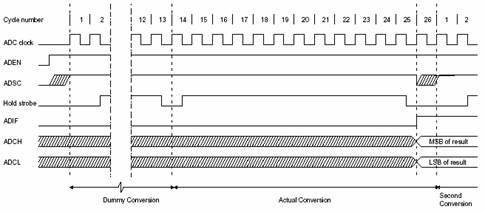

Figura 10.2 - Ciclul unei prime conversii in mod Single Conversion

Functionarea ADC este validata

prin scrierea in 1 logic a bitului de validare

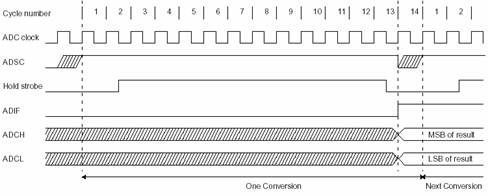

Figura 10.3 - Ciclu de conversie normala in mod Single Conversion

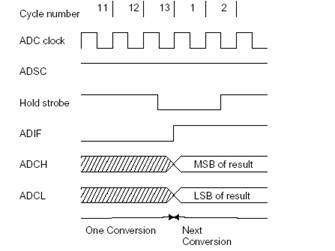

O conversie este pornita prin scrierea unui 1 logic in bitul de start conversie, ADSC. Acest bit va sta in 1 logic pe toata perioada conversiei si va fi trecut in 0 logic prin hardware atunci cand conversia s-a terminat (figurile 10.3 si 10.4).

.

Figura 10.4 - Ciclu de conversie normala in modul Free Run

Deoarece convertorul genereaza un rezultat pe 10 biti, trebuiesc citite doua registre de date, ADCL si ADCH, pentru a obtine rezultatul conversiei. S-au prevazut circuite logice in mod special pentru a asigura ca in cele doua registre se afla rezultatul aceleiasi conversii atunci cand sunt citite. Acestea functioneaza in felul urmator:

Cand se citesc datele, se citeste mai intai ADCL. Din momentul in care s-a citit ADCL accesul ADC la registrele de date este blocat. Aceasta inseamna ca daca s-a citit ADCL si o noua conversie se termina inainte de a se citi ADCH, nici unul dintre aceste registre nu este reactualizat si rezultatul noii conversii este pierdut. Atunci cand este citit ADCH, se permite din nou accesul ADC la registrele ADCL si ADCH.

ADC are propria sa intrerupere, ADIF, care poate fi declansata atunci cand se termina o conversie. Atunci cand accesul ADC la registrele de date este blocat, intre citirea ADCL si ADCH, intreruperea se va declansa totusi, chiar daca rezultatul se pierde.

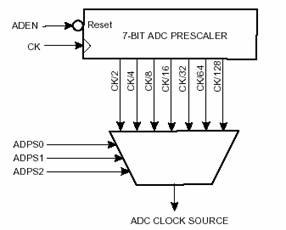

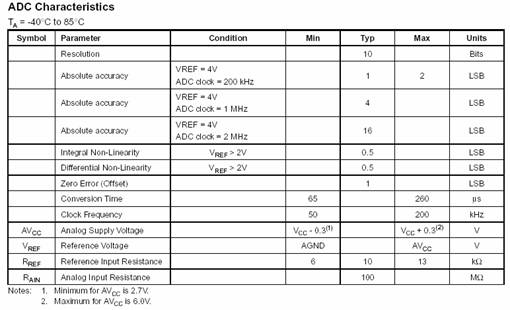

Convertorul analog-numeric are un prescaler, care divizeaza ceasul sistemului pana la o frecventa de ceas acceptabila pentru ADC, in domeniul 50-200 KHz (figura 10.5). Aplicarea unei frecvente de intrare mai mari conduce la o acuratete mai scazuta, cum se poate observa in paragraful 'Caracteristicile ADC'.

Bitii ADPS0-ADPS2 din registrul ADCSR sunt folositi pentru a selecta o frecventa convenabila pentru ADC, pornind de la orice cristal de cuart de minim 100 KHz. Prescalerul functioneaza atata timp cat bitul ADEN este in 1 logic si sta in reset atata timp cat bitul ADEN este in 0 logic.

Figura 10.5 - Prescalerul convertorului analog numeric

Atunci cand se comanda startul unei conversii prin punerea in 1 logic a bitului ADSC din registrul ADCSR, conversia porneste atunci cand apare urmatorul front crescator al ceasului ADC. Esantionarea si memorarea dureaza 1,5 cicluri de ceas al ADC dupa startul conversiei. Rezultatul este disponibil in registrul de rezultat al ADC dupa 13 cicluri de ceas. In modul de lucru Single Conversion ADC are in principiu nevoie de inca un ciclu inainte de a se da start pentru o noua conversie, conform figurii 10.3. Totusi , daca bitul ADSC este pus in 1 in aceasta perioada, o noua conversie va incepe imediat. In modul Free Running, o noua conversie incepe imediat dupa ce rezultatul este scris in registrele de rezultat ale ADC . Folosind modul Free Running si o frecventa de ceas de 200 KHz se obtine cea mai mica perioada de conversie - 65 µs echivalenta cu o viteza de conversie de 15,4 kSPS. Timpii de conversie sunt prezentati sintetic in tabelul 10.1.

|

Conditiile de functionare |

Ciclul in care se face Esantionarea |

Cicluri pana la obtinerea rezultatului |

Timp total de conversie (cicluri) |

Timp total de conversie (ms) |

|

Prima conversie, Free run |

14 |

25 |

25 |

125-500 |

|

Prima conversie Single |

14 |

25 |

25 |

130-520 |

|

Free Run |

2 |

13 |

13 |

65-260 |

|

Single Conv. |

2 |

13 |

13 |

70-280 |

Tabelul 10.1 - Timpii de conversie ai ADC

3. Functia de reducere a zgomotului.

Convertorul analog numeric este prevazut cu un reducator de zgomot care permite efectuarea unei conversii atunci cand procesorul intra in modul idle, micsorand astfel zgomotele datorate functionarii nucleului procesor. Pentru a folosi aceasta facilitate, se procedeaza in modul urmator:

1. Se va avea grija ca ADC sa fie validat si sa nu se fie ocupat cu o conversie (trebuie deci sa fie selectat modul Single Conversion). Trebuie de asemenea sa fie validata intreruperea de sfarsit de conversie

ADEN=1

ADSC=1

ADFR=0

ADIE=1

2. Se va intra in modul Idle. ADC va incepe automat o conversie atunci cand nucleul procesor se opreste.

3. Daca nici o alta intrerupere nu apare inainte ca ADC sa termine conversia intreruperea ADC va reporni nucleul procesor si va executa rutina de conversie terminata.

4. Registrele asociate convertorului analog numeric

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

$07($27) |

MUX2 |

MUX1 |

MUX0 |

|||||

|

Citeste/Scrie |

C |

C |

C |

C |

C |

C/S |

C/S |

C/S |

|

Valoare initiala |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Bitii MUX2-MUX0 ai acestui registru selecteaza de pe care dintre intrarile 7-0 se va citi semnalul analogic care va fi convertit numeric.

Registrul de stare si control al ADC - ADCSR

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

$06($26) |

ADEN |

ADSC |

ADFR |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

|

Citeste/ Scrie |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

C/S |

|

Valoare initiala |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Punerea in 1 logic a acestui bit activeaza ADC. Prin punerea in 0 logic, acesta este oprit, chiar daca in acel moment este in curs de efectuare o conversie.

In modul Single conversion se va scrie un 1 logic in acest bit pentru a porni o conversie. In modul Free Running, punerea in 1 logic a acestui bit va porni prima conversie. Prima oara cand este scris bitul ADSC dupa ce ADC a fost activat, sau daca aceste evenimente se petrec simultan, se va efectua mai intai o conversie de initializare ("dummy conversion") si abia dupa aceea conversiile normale.

ADSC ramane in 1 pe durata unei conversii si trece in 0 dupa ce conversia s-a terminat, dar inainte ca rezultatul sa fie scris in registrele de date. Aceasta permite ca o noua conversie sa fie initiata inainte ca prezenta conversie sa se termine. Noua conversie va porni astfel imediat ce se termina cea curenta. Cand se face conversia de initializare, bitul ADSC va ramane in 1 pana cand se va termina conversia reala care urmeaza automat.

Punerea in 0 a acestui bit nu are nici un efect.

Punerea in 1 logic a acestui bit va face ca ADC sa functioneze in modul Free Run. In acest mod de lucru, ADC esantioneaza semanlul de intrare si reactualizeaza registrele de date in mod continuu. Punerea in 0 a acestui bit va trece ADC in modul Single Conversion.

Acest bit este trecut in 1 logic atunci cand se termina o conversie si registrele de date sunt reactualizate. In continuare, daca bitul ADIE si bitul I din SREG sunt in 1 logic, se va executa o intrerupere de sfarsit de conversie. Cand se executa vectorul de intrerupere respectiv, acest bit este trecut automat in 0 logic prin hardware. Ca alternativa acest bit poate fi sters scriind un 1 peste el. Trebuie tinut seama ca daca se executa un ciclu citire-modificare-scriere a registrului ADCSR, o eventuala intrerupere an asteptare poate fi dezactivata. Acest lucru se poate intampla si daca se folosesc instructiunile SBI si CBI cu acest registru.

Cand acest bit este in 1 logic si bitul I din SREG este tot in 1 logic va putea fi generata o intrerupere de sfarsit de conversie.

Acesti biti determina factorul de divizare a frecventei cristalului si frecventa de intrare a ADC, conform tabelului 10.2

|

ADPS2 |

ADPS2 |

ADPS2 |

Factor de divizare |

|

0 |

0 |

0 |

2 |

|

0 |

0 |

1 |

2 |

|

0 |

1 |

0 |

4 |

|

0 |

1 |

1 |

8 |

|

1 |

0 |

0 |

16 |

|

1 |

0 |

1 |

32 |

|

1 |

1 |

0 |

64 |

|

1 |

1 |

1 |

128 |

Tabelul 10.2 - Factorul de divizare al prescalerului ADC

|

Bit |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

$05($25) |

ADC9 |

ADC8 |

||||||

|

$04($24) |

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADC1 |

ADC0 |

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Citeste/ Scrie |

C |

C |

C |

C |

C |

C |

C |

C |

|

C |

C |

C |

C |

C |

C |

C |

C |

|

|

Valoare initiala |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Atunci cand se termina o conversie, rezultatul acesteia se afla in aceste doua registre. In modul Free Run este esential ca ambele registre sa fie citite si ca ADCL sa fie citit inaintea lui ADCH.

5. Scanarea mai multor canale

Deoarece schimbarea unui canal analogic poate avea loc numai dupa ce s-a terminat conversia curenta, modul Free Run poate fi utilizat pentru scanarea mai multor canale fara a se intrerupe convertorul. In mod normal, subrutina de tratare a intreruperii de sfarsit de conversie va face schimbarea canalului. Totusi, utilizatorul trebuie sa tina seama de urmatoarele consideratii:

Intreruperea se declanseaza atunci cand rezultatul este pregatit pentru a fi citit. In modul Free Run urmatoarea conversie va fi insa declansata in acelasi moment cu intreruperea. Daca ADMUX este schimbata dupa declansarea intreruperii, urmatoarea conversie a inceput deja cu vechiul canal. Prin urmare, va exista un decalaj de un canal de care trebuie sa se tina seama in algoritm.

6. Tehnici de reducere a zgomotului ADC

Circuitele digitale din interiorul si exteriorul microcontrolerului genereaza inductii electomagnetice care pot afecta acuratetea masuratorilor analogice. Daca acuratetea conversiei este critica, nivelul de zgomot poate fi redus prin aplicarea urmatoarelor tehnici:

Figura 10.6 - Conexiunile de alimentare ale ADC

Tabelul 10.3 - Caracteristicile ADC

7. Modul de lucru

Indicatii: Se va folosi partea de transmisie seriala de la lucrarea precedenta. Pentru fiecare conversie se va transmite o secventa formata din 4 caractere: octetul superior rezultat, octetul inferior rezultat, caracterul Carriage Return ($0A) si caracterul Line Feed ($0D).

Copyright © 2025 - Toate drepturile rezervate