| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

PARAMETRII SI CARACTERISTICILE PORTILOR LOGICE

SCOPUL LUCRARII

Lucrarea are ca scop realizarea unei punti de legatura intre logica binara (booleana) si implementarea practica a operatorilor logici cu ajutorul circuitelor electronice. In prima parte a lucrarii se face o scurta prezentare a algebrei binare dupa care se trateaza problematica portilor logice realizate in tehnologie intgrata.

Considerente teoretice

Proprietatile agebrei binare

matematicianul englez George Boole (1815 - 1854 ) a elaborat o algebra (algebra booleana) ale carei axiome si teoreme pot fi utilizate pentru a transforma logica aristoteliana, a rationamentului pur, intr-un limbaj formal ce opereaza cu simboluri (logica formala). Aceasta logica formala poate fi utilizata ca un instrument operant in sistemele fizice (mecanice, pneumatice, hidraulice, electrice etc.) ale caror elemente prezinta in functionare doar doua stari distincte. Aplicatiile practice ale algebrei booleane au inceput din momentul in care C. E. Shannon a utilizat-o in descrierea functionarii circuitelor electrice ce contin contacte si relee.

Algebra booleana opereaza cu o multime binara B = peste care sunt definite trei legi de compozitie interna (operatori logici):

- negatia logica (operatorul NOT);

- produsul logic (operatorul AND);

- suma logica (operatorul OR).

Pe baza proprietatilor algebrei binare (prezentate in tabelul 1) se poate demonstra ca fiecare pereche de operatori (NOT, AND) sau (NOT, OR) este suficienta pentru descrierea cu succes a oricarei functii logice. Un ansamblu de operatori care prezinta aceasta proprietate poarta denumirea de sistem complet.

Tabelul 1

|

Nr. crt. |

Denumire |

Expresia matematica cu operator produs |

Expresia matematica cu operator suma |

|

Asociativitatea (axioma) |

X· (Y·Z) = (X· Y)·Z |

X+(Y+Z) = (X+Y)+Z |

|

|

Comutativitatea (axioma) |

X· Y = Y·X |

X+Y = Y+X |

|

|

Elementul neutru (axioma) |

X· 1=X |

X+0=X |

|

|

Distributivitatea (axioma) |

X· (Y+Z) = X·Y+ Y·Z |

X+Y·Z=(X+Y)· (X+Z) |

|

|

Existenta complementului (axioma) |

X· X' = 0 |

X + X' = 1 |

|

|

Idempotenta (teorema) |

X· X = X |

X + X = X |

|

|

(teorema) |

X· 0 = 0 |

X + 1 = 1 |

|

|

Dubla negatie (teorema) |

( X' )' = X |

( X' )' = X |

|

|

Absorbtia (teorema) |

X· (Y+Y) = X |

X + X· Y = X |

|

|

Absorbtia inversa (teorema) |

X'· (Y+Y) = X· Y X· (Y'+Y) = X· Y |

X' + X· Y = X X + X'· Y = X |

|

|

Teorema lui DeMorgan |

(X· Y)' = X' + Y' |

(X+Y)' = X'· Y' |

Sisteme complete mai simple, cu o singura componenta, rezulta prin combinarea intr-un singur operator a membrilor ce alcatuiesc un sistem complet. Astfel prin cuplarea operatorului NOT cu AND se obtine operatorul NAND iar prin cuplarea operatorului NOT cu OR se obtine operatorul NOR. Particularitatea noilor operatori consta tocmai in faptul ca fiecare in parte realizeaza un sistem complet. Acest lucru prezinta o importanta practica deosebita deoarece arata posibilitatea de a reliza sisteme logice utilizand doar un singur tip de circuit distinct, circuit ce implementeaza fie operatorul NAND fie operatorul NOR.

Pe langa operatorii deja mentionati, in practica se mai utilizeaza operatorul , sumare modulo doi, XOR si complementarul sau XNOR.

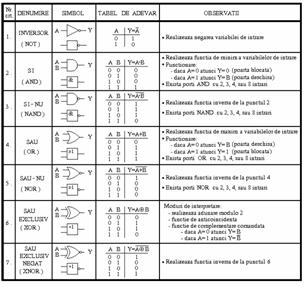

2.2. Porti logice

Circuitele electronice care modeleaza operatorii logici capata o reprezentare specifica si sunt tratate ca entitati distincte in tehnica digitala. Aceste entitati se numesc porti logice si sunt realizate cu circuite care lucreaza, atat la intrare cat si la iesire, cu doua nivele de tensiune distincte. In general, se considera ca portile logice sunt cele mai simple circuite digitale. Tabelul de adevar si simbolurile asociate portilor logice sunt reprezentate in tabelul 2.

2.3. Tehnologii de realizare a portilor logice

In decursul timpului, pe masura dezvoltarii tehnologiei si in functie de necesitatile de viteza si consum au fost elaborate mai multe familii de circuite integrate digitale. In momentul de fata exista doua tehnologii de realizare a circuitelor integrate care au ca structura de baza siliciul: tehnologia bipolara - care foloseste tranzistoare NPN sau PNP, si tehnologia unipolara - care utilizeaza tranzistoare MOS cu canal N sau canal P.

In cadrul tehnologiei bipolare se disting urmatoarele familii de circuite integrate digitale:

- in logica saturata:

-TTL (transistor transistor logic) standard seriile 54*** si 74***

-STTL (Schottky TTL) .. seriile 54S*** si 74S***

-ASTTL (Advanced Schottky TTL) seriile 54AS*** si 74AS***

-LSTTL (Low-power Schottky TTL) .. seriile 54LS*** si 74LS***

-FTTL (Fast TTL) seriile 54F*** si 74F***

-ALSTTL (Advanced Low-power Schottky TTL) seriile 54ALS*** si 74ALS***

- in logica nesaturata:

-ECL 10K (Emitter Coupled Logic)

-ECL 100K (Emitter Coupled Logic).

In cadrul tehnologiei unipolare se disting urmatoarele familii de circuite integrate digitale:

- CMOS (Complementary MOS) normale:

- CMOS .. seria 4000

- HCMOS (High speed CMOS) seria HC

- ACMOS (Advanced CMOS) .. seria AC

- CMOS (Complementary MOS) compatibile TTL:

- seria 74C*** compatibila cu seria 74S***

- seria HCT*** compatibila cu seria 74LS***

- seria ACT*** compatibila cu seria 74ALS***

- NMOS ( MOS cu canal N)

- PMOS (MOS cu canal P).

Tehnologii alternative non-silicon sunt cele in arsenura de galiu, GaAS, sau cele cu jonctiuni Josephson. Dispozitivele in GaAs au viteze de lucru cam de cinci ori mai ridicate decat cele care se pot obtine in Si, sunt mai rezistente la radiatii dar sunt mai scumpe. Dispozitivele Josephson sunt foarte rapide dar lucreaza la temperaturi foarte scazute.

2.5. Prezentarea familiei TTL standard

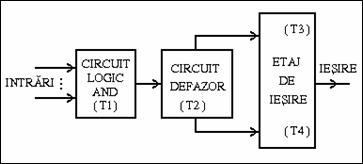

Circuitul de baza al familiei TTL il constituie poarta NAND cu doua intrari a carei schema bloc este prezentata in figura 1.

Fig.1

Etajele ce alcatuiesc poarta NAND pot avea mai multe scheme de realizare, functie de performantele cerute, desi pe ansamblu, functia logica este acceasi. In figura 2 se prezinta schema electrica a portii NAND realizata in tehnologie TTL standard.

Etajul de intrare pentru acest caz, este realizat cu un tranzistor NPN multiemitor (T1). Diodele D1 si D2 au rolul de a scurtcircuita impulsurile negative ce pot apare pe intrarile portii, ca urmare a supracresterilor si a reflexiilor negative datorate fronturilor abrupte si transmisiei pe linii lungi de interconectare. Pot exista si etaje de intrare cu tranzistoare PNP ce ofera avantajul unor curenti de intrare mici.

Etajul defazor este realizat cu tranzistorul T2 si are rolul de a genera doua semnale, defazate intre ele cu 180 , necesare atacului in contratimp al etajului de iesire.

Etajul de iesire pate fi realizat in una din urmatoarele variante: TOTEM POLE, OPEN COLLECTOR sau THREE STATE ( TRISTATE).

a) Etajul TOTEM POLE (denumit si etaj in contratimp), este specific familiei TTL standard si este alcatuit din tranzistoarele T3 si T4 comandate in antifaza de catre etajul defazor. In regim stionar acest etaj prezinta un tranzistor blocat iar celalalt saturat. Impedanta de iesire este de accelasi ordin de marime atat pentru "zero logic" (T3 saturat si T4 blocat), cat si pentru starea de "unu logic" (T3 blocat si T4 saturat).

|

Fig. 2. Schema electrica a portii NAND - TTL standard |

w Daca emitoarele sunt conectate la Vcc (A=B= "1"), atunci jonctiunile BE ale tranzistorului T1 sunt polarizate invers, deci T1 este in regiunea activa inversa si asigura curent de baza pentru T2. Tranzistorul T2 este saturat puternic, iar curentul sau de emitor satureza si tranzistorul T3. Potentialul bazei tranzistorului T4 este dat de relatia:

VB4 = VBE3sat + VCE2sat 1V

si este insuficient pentru deschiderea tranzistorului T4 datorita prezentei diodei D3. In consecinta, potentialul de iesire este: Vo= VCE3sat 0,2V, deci iesirea este in starea "zero logic".

w Daca cel putin una din intrari este adusa la un potential corespunzator starii de zero logic ( 0.2 V) atunci jonctiunea BE a tranzistorului T1 se deschide. Curentul din baza lui T1 va circula acum prin terminalul de intrare si nu prin baza lui T2. Deci T2 si T3 vor fi blocate, iar T4 deschis de curentul prin R3. In acest caz la iesire avem un potential dat de relatia: Vo = Vcc - ( IB2 R 2+ VBE3 + VD ) 3,8V valoare ce se incadreaza in banda de "unu logic".

Proprietatile (particularitatile) iesirilor cu etaje totem pole:

t Nu pot fi conectate in paralel deoarece apare o circulatie de curent de valoare mare pentru cazul in care starea logica a iesirilor este complementara. Aceasta situatie este prezentata in figura 3.

|

Fig. 3. Cazul conectarii in paralel a portilor TTL standard |

t Tranzistoarele T3 si T4 conduc simultan, un interval scurt de timp, la tranzitia iesirii din "1" in "0". In acest interval curentul absorbit de circuit este mare. Conexiunile de alimentare ale circuitului raspund, acum preponderent inductiv, provocand o scadere a tensiunii de alimentare. Din acest motiv, langa capsula circuitului integrat, intre Vcc si masa, se conecteaza un condensator de cca. 10nF cu inductanta parazita redusa (condensator de decuplare);

t Asigura cu resurse interne nivelul de tensiune pentru ambele stari logice;

t Prezinta impedante de iesire reduse si au acelasi ordin de marime pentru ambele stari logice.

b) Etajul OPEN COLLECTOR (colector in gol) se obtine dintr-un etaj totem pole prin eliminarea repetorului pe emitor T4, ramane tranzistorul T3 al carui colector este conectat la iesirea portii.

|

Fig. 4. Etaj de iesire open collector |

Acest etaj poate genera un bun "zero logic", prin saturarea tranzistorului T3, dar pentru "unu logic" va fi necesara, pe langa blocarea lui T3, si utilizarea unei rezistente externe conectate inspre Vcc. Deci circuitul genereaza autoritar "zero logic" iar pentru "unu logic" este permisiv.

Valoarea rezistentei externe adaugta de catre utilizator se calculeaza in fuctie de conditiile concrete de lucru ale portii.

Cuplarea portii la o sarcina capacitiva, constituita de intrarea altor porti, duce la obtinerea unor timpi de front inegali deoarece constantele de incarcare si descarcare sunt ingale.

Proprietatile (particularitatile) iesirilor cu etaje open collector:

t Functionarea portii este posibila doar in prezenta portii externe.

t Impedantele de iesire sunt net diferite.

t Iesirile pot fi conectate in paralel prin utilizarea in comun a aceleasi rezistente externe. Acest mod de lucru face ca nodul de conexiune sa se comporte ca o poarta AND virtuala, denumita SI CABLAT, ale carei intrari sunt iesirile portilor concrete.

t Nivelul de "unu logic" este generat precar, prin intermediul rezistentei externe.

t Timpii de front pentru sarcini capacitive sunt inegali.

c) Etajul de iesire tristate

Iesirea tristate prezinta pe langa cele doua stari logice bine cunoscute LOW si HIGH o stare suplimentara denumita stare de inalta impedanta, notata HiZ. Aceste circuite au prevazute o intrare suplimentara de comanda, denumita ENABLE, prin intemediul careia se poate obtine starea HiZ. Starea HiZ inseamna dezactivarea completa a iesirii, lucru posibil prin blocarea simultana a celor doua tranzistoare ale etajului totem pole.

Fig. 5. Poarta cu iesire tristate: a) structura; b) simbol, tabel de adevar; c) exemplu de conectare in paralel

In starea de inalta impedanta tensiunea de iesire are valoarea fixata de potentialul care exista pe linia de magistrala la care este cuplata iesirea portii (acest potential este fortat pe magistrala de catre o alta poarta).

O structura de inversor tristate este prezentata in figura 5.

Cand semnalul de validare a iesirii E , OE, (ENABLE, OUTPUT ENABLE ) este activ, adica este "zero logic", dioda D2 este blocata iar emitorul doi al tranzistorului T1 este la potential ridicat deci poarta functioneaza ca un inversor normal. Daca semnalul de validare nu este activat, E="1", atunci emitorul doi al tranzistorului T1 este la potential zero, tranzistoarele T2 si T3 sunt blocate, dar si T4 este blocat deoarece prin dioda D2 baza acestuuia ste la potential apropiat de al masei. Aceasta stare, cu ambele tranzistoare bloate, este denumita starea de inalta impedanta.

Proprietatile (particularitatile) iesirilor cu etaje tristate:

t Permite conectarea in acelasi punct a mai multor iesiri, cu conditia ca numai una sa fie activa la un moment dat;

t Ofera impedante mici la iesire, si de accelasi ordin de marime, pentru ambele stari logice (ca la poarta TTL standard);

t Nu necesita rezistenta externa ca in cazul etajelor open collector;

t In starea de inalta impedanta incarca nesemnificativ circuitele cu care sunt cuplate la iesire.

Schemele echivalente intuitive ale celor trei variante de relizare a etajelor de iesire ale portilor logice sunt prezentate in figura 6.

Fig. 6 Schemele echivalente ale etajelor de iesire

2.4. Parametrii portilor logice

Prin parametrii unui circuit logic se inteleg valorile de catalog ale marimilor care ii caracterizeaza functionarea sa, in conditii de test, sau la interconectarea cu alte circuite din aceasi familie. Parametrii trebuie astfel alesi incat sa caracterizeze cat mai bine regimul de curent continuu, regimul tranzitoriu si comportamentul la zgomot al circuitului digital. Frecvent acesti parametrii sunt dati in cataloage ca valori tipice (normale) sau ca valori pentru cazul cel mai defavorabil.

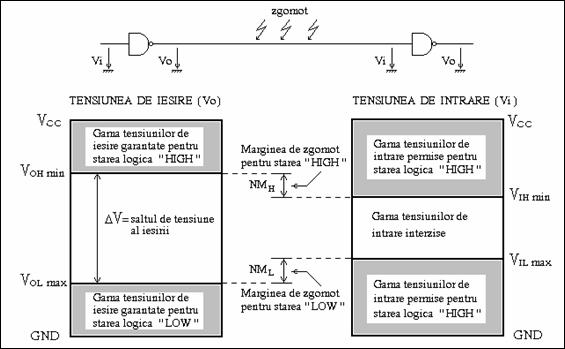

a) Nivelurile de tensiune asociate starilor logice

La prima vedere, modelarea celor doua cifre binare in circuite electronice s-ar putea face asociind prin conventie un nivel de tensiune pentru "unu logic" si un altul pentru "zero logic". Acest mod de lucru nu pote fi adoptat in practica deoarece nivelurile de tensiune sunt afectate de o serie de factori perturbatori cum sunt: dispersia tehnologica, imbatranirea componentelor, variatiile tensiunii de alimentare etc. Din aceste motive pentru fiecare stare logica s-a alocat cate o banda de tensiuni permise. Pentru a putea face distinctie intre cele doua stari logice, benzile de tensiune asociate sunt separate de o zona interzisa (vezi fig. 7).

b) Marginea de zgomot

Pe traseul de legatura intre iesirea unui circuit si intrarea altuia se transmite un semnal util peste care se poate suprapune un altul asimilabil cu un zgomot. Se pune in mod firesc intrebarea cat de mare poate fi acest zgomot penru a nu perturba functionarea sistemului? Parametrul ce defineste imunitatea la zgomot este denumit margine de zgomot (noise margin) si se noteaza cu NMH, pentru starea logica "high", si NML pentru starea logica "low".

Marginea de zgomot reprezinta unul dintre cei mai importanti parametrii ai circuitelor digitale deoarece ofera o masura a imunitatii acestora la perturbatii. Marginea de zgomot se defineste in doua moduri: marginea de zgomot statica si marginea de zgomot dinamica.

Fig.7. Nivelurile de tensiune alocate starilor logice

Marginea de zgomot statica este data de amplitudinea maxima a semnalului de zgomot lent variabil care se poate suprapune peste semnalul util fara ca acesta sa perturbe functionarea normala a circuitului. In foile de catalog ale circuitelor digitale sunt specificate valorile extreme ale tensiunii garantate la iesire (VOL max ,VOH min ) si ale tensiunii admisibile la intrare (VIL max , VIH min) pentru fiecare stare logica in parte. Analizand fig.1 se observa ca valorile extreme ale tensiunii de iesire au fost alese acoperitor in raport cu valorile admisibile ale tensiunii de intrare in scopul preintampinarii influientei zgomotelor.

Marginea de zgomot poate fi diferita pentru cele doua stari logice si se calculeaza cu relatiile:

NMH = VOH min - VIH min

NML = VOL max - VIL max

in care:

- VOL max reprezinta valoarea maxima (garantata de fabricant) pentru tensiunea de iesire corespunzatoare unei iesiri logice aflata in starea "low" ;

- VOHmin reprezinta valoarea minima (garantata de fabricant) pentru tensiunea de iesire corespunzatoare unei iesiri logice aflata in starea "high" ;

- VIHmin reprezinta valoarea minim necesara a tensiunii de intrare (garantata de fabricant) pentru a fi interpretata drept "unu logic" (stare "high" );

-VOLmax reprezinta valoarea maxima (garantata de fabricant) a tensiunii de intrare care e ste interpretata drept "zero logic" (starea "low" ).

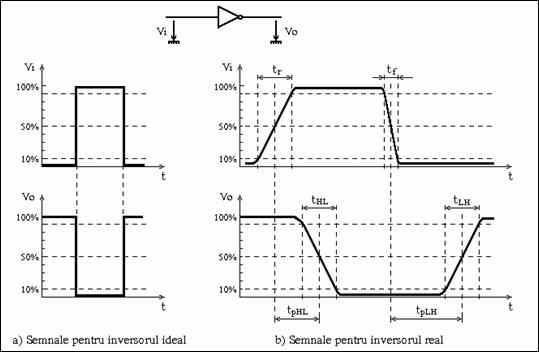

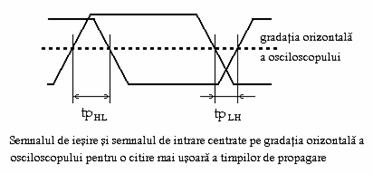

c) Timpul de propagare

Acest parametru reprezinta intarzierea in timp intre momentul aplicarii unui semnal logic la intrarea unei poarti si momentul aparitiei raspunsului la iesirea acesteia. Timpul de propagare fiind un apect nedorit, care apare in functionarea portilor logice, este necesar ca valoarea acestuia sa fie cat mai redusa. In functie de tehnologia de realizare intarzierea introdusa este ordinul unitati - zeci de nanosecunde ( 10- 9 s).

Modul de definire a intervalelor de timp specifice semnalelor digitale se prezinta in figura 8 considerand cazul unui inversor. Semnificatia acestor marimi temporale este urmatoarea:

- tr - (rise time) timpul de crestere al semnalul de intrare in poarta masurat intre 10% si 90% din amplitudinea tensiunii de nivel "unu logic";

- tf - (fall time) timpul de descrestere al semnalul de intrare masurat intre 90% si 10% din amplitudinea tensiunii de nivel "unu logic";

- tpHL - timpul de propagare al semnalului pentru tranzitia iesirii din "1" in "0";

- tpLH - timpul de propagare al semnalului pentru tranzitia iesirii din "0" in "1";

- tHL - durata frontului cazator pentruu semnalul de iesire;

- tHL - durata frontului crescator pentru semnalul de la iesire;

- tp - timpul mediu de propagare definit prin relatia:

tp = (tpHL + tpHL)

Pentru circuitele logice concrete tpHL tpLH , chiar daca in catalog vom gasi pentru anumite tipuri de porti ca tpHLmax = tpLHmax . Valorile limita pot fi egale, dar nu si cele efective la nivelul fiecarei porti. Se recomanda ca perioada T a semnalului de intrare sa satisfaca relatia:

T tp

Fig. 8. Definirea timpilor de propagare

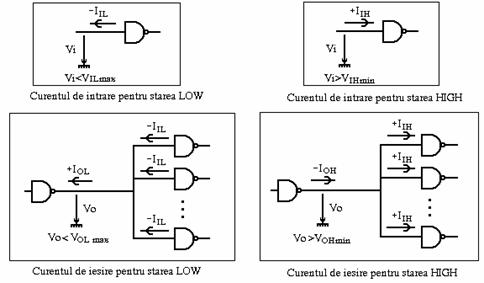

d) Factorul de incarcare

Un circuit logic trebuie sa poata genera/absorbi la iesire un curent mai mare sau egal cu suma curentilor absorbiti/generati de toate portile care sunt conectate la acea iesire asigurand totodata nivelul garantat al tensiunii in starea "0" sau "1".

Se introduce conventia de semne pentru curentii referitori la o borna, curentul care intra intr-o borna are semnul pozitiv, iar cel care iese dintr-o borna are semnul negativ. Circulatia curentilor pentru o poarta logica este ilustrata in figura 9.

Pentru circuitele TTL vom face o serie de observatii referitoare la marimile ce apar in figura 9:

t IIL - curentul de intrare in starea low. Valoarea maxima a acestui curent este de 1,6 mA. Urmarind schema portii NAND remarcam ca, la legarea mai multor intrari ale unei porti impreuna, curentul total, debitat de acet grup, va avea tot valoarea IIL deoarece:

IIL = (Vcc- VOL - VBE) R1

t IIH - curentul de intrare in starea high, are valoarea maxima de 40mA. Este un curent dual provenind din insumarea curentului BE, ai tranzistoarelor laterale si ai diodei de protectie. Pentru acest motiv, datorita naturii lui, daca se leaga impreuna mai multe intrari, curentul prin nod va fi egal cu suma curentilor corespunzatori fiecarei intrari;

t IOL - curentul de iesire in starea low, are valoarea maxima de 16mA. Este limitat de puterea disipata de tranzistorul T3 si de marimea valorii VOL .

Fig. 9.

t IOH - curentul de iesire in starea high, are valoarea maxima garantata de cel putin de 0,8mA. Aceasta limitare este data de scaderea nivelului de "unu logic" si de puterea disipata. Pentru etajul open collector apare un curent diferit de cel de la totem-pole, un curent rezidual absorbit de tranzistorul blocat, valoarea lui este de 100 mA.

Factorul de incarcare la iesirii FO, (fan-out, output loading factor, sortance), este un numar ce indica capacitatea iesirii de a comanda intrarile altor circuite similare.

Fan-out este, in general, diferit pentru cele doua stari logice putandu-se calcula cu relatiile:

FOLOW = IOL min / IIL max

FOHIGH = IOH min / IIH max

FO = min

Factorul de incarcare al intrarii FI, (fan-in, input loading factor, facteur de charge) reprezinta numarul de unitati de sarcina percepute la intrarea unui circuit digital. FI este dependent de complexitatea circuitului logic si poate avea valori mai mari decat 1. De exemplu, o iesire TTL standard poate comanda 10 intrari cu FI=1 sau 5 intrari cu FI=2. Valorile curentilor de intrare / iesire specifici familiei TTL sunt dati in tabelul 3

Tabelul 3

|

SERIA |

INTRARE nivel LOW nivel HIGH IIL max [mA] IIH max[mA] |

IESIRE nivel LOW nivel HIGH IOL max[mA] IOL max[mA] |

|

40 |

16 - 0,4 / - 0,8 |

|

|

74 S ** |

50 |

20 - 1,0 |

|

74 LS ** |

20 |

8 - 0,4 |

|

74 AS ** |

20 |

4 / 8 - 0,4 |

|

74 ALS ** |

20 |

8 - 0,4 |

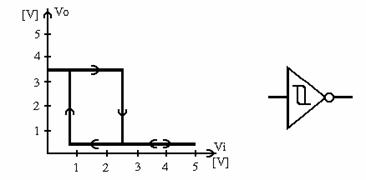

e) Caracteristica de transfer, VTC (Voltage Transfer Characteristic)

Caracteristica de transfer reprezinta dependenta statica intre tensiunea de intrare in poarta, si tensiunea de iesire, Vo=f (Vi). Aceasta, prezinta o importanta deosebita deoarece ofera informatii despre valorile efective ale unor marimi ca: marginea de zgomot, nivelele limita ale tensiunii de intrare, latimea benzii interzise, etc.

Forma caracteristicii de transfer pentru circuite din acceasi familie este asemanatoare dar, coordonatele punctelor de frangere sunt specifice fiecarui circuit in parte. Spre exemplu,in figura 9, se prezinta caracteristica de transfer tipica pentru poarta SN 7400 (familia TTL standard).

Analizand caracteristica din fig. 10 se observa ca segmentele AB si respectiv DE corespund benzilor permise tensiunii de intrare pentru cele doua starari logice, iar segmentele BC si CD corespund benzii interzise. Dintr-un alt punct de vedere, daca ne raportam la un semnal dreptunghiular aplicat la intrare, segmentele AB si DE corespund palierelor, iar BC in prelungire cu CD fronturilor.

Marginea de zgomot efectiva se determina observand ca semnalul suma (semnal util + zgomot), nu trebuie sa depaseasca abscisa punctului C pentru "unu logic", respectiv D pentru "zero logic".

Nivelele de tensiune garantate pentru intrare, 0,8V respectiv 2V sunt, dupa cum se vede in figura, mult in afara zonei interzise efective, in scopul de a reduce efectul variatiile de temperatura si dispersia tehnologica in buna functionare a portii. In practica zona interzisa este considerata acoperitor in intervalul 0,8V 2V.

Regimurile de lucru ale tranzistoarelor, conform notatiilor din figura 1, pentru fiecare segment al caracte-risticii de transfer sunt prezentate in tabelul 4.

Tabelul 4

|

T1 |

T2 |

T3 |

T4 |

|

|

|

saturat |

blocat |

blocat |

saturat |

|

|

saturat |

conduce |

blocat |

conduce |

|

Segmentul CD |

RAN |

RAN |

RAN |

RAN |

|

|

RAI |

saturat |

saturat |

blocat |

t Pentru segmentul CD toate tranzistoarele se afla in regiunea activa normala. Pentru acest caz, in circuitul format din T2, T3, si T4 apare o reactie pozitiva. Astfel, aparitia unei variatii in colectorul tranzistorului T2, este urmata de aducerea pe circuitul de reactie (bucla de reactie) a unui semnal ce tinde sa mareasca efectul variatiei initiale. Acest tip de reactie este util deoarece are ca efect accelerarea procesului de tranzitie, dar in momentul in care tensinea de intrare este mentinuta in regiunea CD, tot reactia pozitiva poate duce la aparitia unor oscilatii la iesire. Frecventa acestor oscilatii este de aproximativ 10 Mhz in cazul portilor TTL standard. Pentru a evita amorsarea acestor oscilatii, trebuie ca durata de traversare a zonei interzise (segmentul CD), de catre semnalul de intrare, sa nu depaseasca 40 50 ns. In consecinta, se recomanda ca durata fronturilor de atac, ale semnalului de intrare sa fie sub 50ns. Cu cat caracteristica de transfer va fi mai verticala, se vor putea utiliza fronturi de atac mai lungi.

Fig. 10. Caracteristica de transfer a inversorului TTL - standard

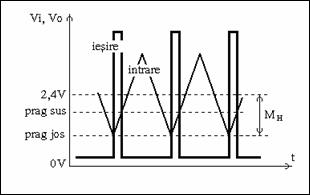

O mentiune speciala trebuie facuta pentru portile care au un etaj suplimentar, denumit "TRIGGER SCHMIT", plasat intre circuituul de intrare si etajul defazor. Referitor la aceste porti, a caror caracteristica de transfer este prezentata in fig. 10, se pot face urmatoarele observatii:

t Castigul suplimentar, datorat amplificatorul cu cuplaj in emitor ce este intercalat intre intrare si defazor, face ca zonele de tranzitie sa fie practic nule,caracteristica fiind verticala. Aceste porti pot fi comandate si cu fronturi lente; zona interzisa fiind foarte mica, traversare ei este posibila fara amorsarea oscilatiilor.

a) Caracteristica de transfer a inversorului trigger - Schmitt b) Simbol

t Apare un histerezis - doua drumuri diferite - la variatia in sens crescator si apoi descrescator a tensiunii de intrare. Acest histerez mareste marginea de zgomot reala permitand ca cele doua semnale sumate - zgomot si semnal util atat pentru "zero" cat si pentru "unu" pe intrare, sa se suprapuna in zona centrala. Nivelul de "zero" pote urca pana aproape de 1,6V iar nivelul de "unu" pote cobora pana la 0,8V.

3. REGULI DE OPERARE CU CIRCUITELE DIGITALE

3.1. REGULI PRIVIND ALIMENTAREA CIRCUITELOR INTEGRATE DIGITALE

t Functionarea circuitelor logice nu este posibila fara conectatea acestora la o tensine de alimentare corespunzatoare:

- 5V ± 0,25V pentru toate seriile TTL;

- 5V ± 0,5V pentru seria 74 HC ** , (CMOS);

- 3 15 V pentru seria CD 4000, (CMOS);

t Pentru

mentinerea

3.2. REGULI REFERITOARE LA INTRARILE CIRCUITELOR DIGITALE

t Intrarile neutilizate ale circuitelor digitale nu trebuie lasate neconectate deoarece sunt sensibile la zgomot si pot altera functionarea corecta a circuitului;

t Intrarile neutilizate se vor conecta la stari logice alese astfel incat sa nu intervina in functionarea normala a circuitului. Spre exemplu, daca se doreste starea de "unu logic" aceasta se poate obtine in mai multe moduri:

- prin conectarea intrarii la o sursa independenta de tensiune intre 2,4 3,5V;

- prin legare in paralel la intrari care indeplinesc aceasi functie logica - metoda prezinta dezavantajul ca incarca inutil poarta care comanda;

- prin conectarea la Vcc prin intermediul unei rezistente de 1kW

Starea de "zero logic" se otine prin conectarea directa la masa a intrarii, pentru familia TTL, sau prin intermediul unei rezistente pentru familia CMOS.

t Daca totusi o intrare TTL este neconectata ("lasata in aer"), aceasta va fi interpretata de circuit ca fiind in stare logica HIGH;

t Intrarile portilor pot fi conectate in paralel;

3.3. REGULI REFERITOARE LA IESIRILE CIRCUITELOR DIGITALE

t De regula, o iesire digitala se conecteaza, dupa caz, la una sau mai multe intrari digitale;

t Este interzisa conectarea iesirii unui circuit digital, chiar si pentru intervale scurte de timp, la masa, la tensiunea de alimentare, sau la oricare alta sursa de semnal;

t Iesirile nu pot fi conecte in paralel decat in cazul utilizarii etajelor tristate sau open collector;

t Daca numarul de intrari este insuficient, marirea acestuia se poate face prin:

- cuplarea mai multor porti la intrarea alteia;

- utilizarea unei porti expandoare;

- utilizarea de functii cablate utilizand porti open collector.

1. Verificarea functionarii corecte a portilor logice

Pentru circuitele din laborator al caror cod este cunoscut, se cauta in foile de catalog configuratia pinilor de intrare si de iesire, dupa care se testeaza daca sunt functionale din punct de vedere logic. Pentru circuitele fara marcaj, cereti indrumatorului configuratia pinilor si identificati ce porti contin.

Modul de lucru:

- se introduce circuitul de test in soclu ;

- se realizeza conexiuni intre punctele de pe panou notate cu A B C D si intrarile portii ce trebuie verificata. Realizarea conexiunilor se face cu ajutorul firelor, prevazute cu banane la ambele capete, din dotarea panoului;

- se alimenteaza panoul de test cu o tensiune continua de 5V ;

- actionand asupra comutatoarelor A B C D se formeaza toate combinatiile posibile urmarindu-se in accelsi timp starea logica a iesirii: bec aprins semnifica "unu logic", bec stins "zero logic". Rezultatele se trec intr-un tabel pentru identificarea functiei logice;

- testarea se repeta pentru toate portile din aceasi capsula de circuit integrat.

Observatii:

- portile situate in aceasi capsula de circuit integrt sunt independente si, de regula, de acelasi tip. Pot exista situatii in care o poarta sa fie defecta in timp ce restul sa functioneze corect.

2. Pe macheta de test realizati schema electrica din figura de mai jos:

Modul de lucru:

- se cauta in catalog configuratia pinilor pentru circuitul 7400;

- se asociaza, in mod arbitrar, portilor P1 P4 cate o poarta a circuitului 7400;

- se realizeaza conexiunile electrice conform asocierii facute anterior;

- se alimenteaza circuitul la 5V dupa care la intrarile A B se apica toate combinatiile logice in vederea completarii tabelului de adevar;

Intrebari:

L Ce functie logica realizeaza aceasta schema?

L Exita un circuit integrat care sa realizeze aceasta functie logica in mod direct?

3. Verificarea nivelelor logice

Pentru acest caz utilizam un inversor (NOT) din circuitul 7404. La intrarea acestuia conectam iesirea TTL a unui generator de semnal. Se vizualizeaza cu ajutorul osciloscopului semnalele de la intrarea si iesirea inversorului. Se masoara tensiunile de intrare si de iesire pentru ambele stari logice. Se deseneaza corelat formele de unda de la intrarea si iesirea portii NOT.

Modul de lucru:

- se introduce circuitul 7404 intr-un soclu de pe placa de test ;

- se realizeaza conexiunile pentru alimentarea integratului (Vcc = 5V);

- se conectea iesirea TTL a generatorul de semnal la intrare inversorului;

- verificati existenta traseelor de masa intre generatorul de semnal si placa, pe de o parte, si intre placa de test si osciloscop, pe de alta parte;

- o sonda a osciloscopului se conecteaza la intrare iar cealalta sonda la iesirea portii;

- frecventa semnalului de intrare se regleaza la 10kHz;

- se realizeaza masuratorile enumerate la inceputul acestui punct.

Intrebari:

L Ce se intampla cu semnalul de la iesirea portii daca se scoate firul de la borna minus a sursei de alimentare ?

L Refaceti legatura si urmariti efectul daca scoateti de aceasta data firul de la borna plus?

L Cat este tensiunea de la intrarea inversorului corect alimentat, daca inaturati generatorul de semnal (tensiunea unei intrari neconectate)?

Observatii:

- daca utilizati doar o singura sonda a osciloscopului pentru a vizualiza, mai intai semnalul de intrare, iar mai apoi semnalul de iesire, veti avea surpriza sa constatati ca ambele semnale incep cu acelasi front. Aceasta nu inseamna ca inversorul nu lucreaza corect, efectul este datorat principiului de functionare al osciloscopului care afiseaza semnalele incepand cu acelsi front. Pentru a vedea si faza reala a semnalelor, este necesara utilizarea simultana a doua sonde, una la intrare iar cealalta la iesire.

5. Determinarea tensiunii de comutare

Montajul necesar determinarii tensiunii de comutare este identic cu cel de la punctul anterior numai ca, de aceasta data, semnalul de intrare va fi triunghiular.

Semnalul nu trebuie sa aiba componenta negativa iar valoarea sa maxima sa fie mai mica de 5V.

Se vor studia doua cazuri: pentru un inversor 7404 si pentru un inversor trigger Schmitt. Pentru fiecare caz in parte se determina si se deseneaza la scara formele de unda obtinute .

|

Fig. 13 Determinarea tensiunii de prag |

Modul de lucru:

- montajul necesar este deja realizat de la punctul anterior;

- se deconecteaza legatura dintre intrarea portii si generatorul de semnal, pentru reglarea ampitudinii semnalului in gama 0 5V, dupa care se revine la montajul initial;

- se regleaza aceasi axa de referinta pentru ambele canale ale osciloscopului, caz in care tesiunea de prag se masoara la intersectia celor doua forme de unda -vezi fig. 13;

Intrebari:

L Ce reprezinta tensiunea de prag sau tensiune a de comutare cu se mai denumeste?

L Care sunt deosebirile intre un inersor si un inversor trigger schmitt ? Care este explicatia?

L Ce se intampla cu valorile tensiunii de comutare daca se inlocuieste un circuit cu un altul de acelasi tip ?

6. Determinarea marginii de zgomot statice

In partea teoretica s-a aratat ca marginea de zgomot este data de amplitudinea maxima a unui semnal perturbator, lent variabil, ce se pote suprapune peste semnalul util, fara ca acesta sa afecteze functionarea circuitului.

Pentru determinarea acestui parametru la intrarea portii se aplica un semnal triunghiular, de amplitudine variabila, suprapus peste o componenta continua a carei valoare este de 2,4V, egala deci cu limita minima a domeniului HIGH, VOHmin . Amplitudinea semnalului triunghiular, pe post de semnal de zgomot, se creste treptat pana cand tensiunea de iesire din inversor are varfuri cu amplitudinea de 0,4V.

Acelasi mod de lucru se utilizeaza si pentru determinarea marginii de zgomot a portilor cu intrari trigger Schmitt, care au un histerezis mult mai pronuntat. Pentru acest caz marginea superioara se masoara ca in figura 15.

In ambele cazuri se noteaza rezultatele obtinute si se deseneaza formele de unda.

Fig. 15

Modul de lucru:

- montajul necesar este identic cu cel de la punctul anterior;

- osciloscopul este conectat cu un canal la intrare si celalalt la iesirea portii de test, la portile trigger Schmitt se utilizeaza aceasi axa de zero pentru ambele canale;

- se regleaza componenta continua a semnalului triunghiular la valoarea de 2,4V si amplitudine minima;

- amplitudinea semnalului triunghiular se creste treptat pana cand, la iesire apar impulsuri de 0,4V in situatia portilor normale, sau un semnal dreptunghiular curat in cazul portilor trigger Schmitt;

Intrebari:

L Cum se explica faptul ca apar deosebiri intre poarta normala si poarta trigger Schmitt, desi sunt utilizate aceleasi conditii de masura?

L Exista diferente intre valorile gasite si cele specificate in catalog, daca da cum se explica?

L Valorile determinate de dumneavoastra se mentin si pentru alte capsule avand acelasi cod?

7. Trasarea caracteristicii de transfer a portilor logice

Folosind un semnal triunghiular, cu valori in gama 0 5V, cuplat la intrarea portilor se va conecta sonda de masura a semnalului de intrare pe canalul 1 si sonda de masura a semnalului de iesire pe canalul 2, iar comutatorul bazei de timp se aduce in pozitia XY. In acet mod pe ecranul osciloscopului va apare o figura ce exprima dependenta Vo = f(Vi) adica tocmai caracteristica de transfer.

Se vor masura valorile tensiunii de intrare la care apar punctele de frangere precum si panta medie a caracteristicii de transfer pentru circuite de tipul: 7404, 74S04, 74LS04, 7413. Pentru fiecare caz in parte se deseneaza caracteristica de transfer.

Modul de lucru:

- se utilizeaza montajul anterior;

- comutatorul bazei de timp a osciloscopului, SEC/DIV, se aduce in pozitia XY;

- daca figura afisata depaseste marginile ecranului se actioneaza asupra comutatoarelor V/DIV de pe fiecare canal;

- frecventa semnalului triunghiular este de cca. 10kHz;

Observatii:

- Datorita modului de lucru utilizat in ridicare functiei de transfer este posibil, ca pe ecranul osciloscopului, sa apara trasee diferite la parcurgerea in sens crescator respectiv descrescator a tensiunii de intrare. Acest fals histerezis se dat de timpul de propagare a unui semnal prin poarta. Astfel pe acest interval de timp apare o miscare a spotului pa axa OX, in sens pozitiv la parcurgerea crescatoare, respectiv in sens negativ la parecurgerea descrescatoare a tensiunii de intrare. Aceste doua deplasari insumate dau falsul histerezis.

- Pentru a obtine o caracteristica cat mai corecta trebuie ca variatia tensiunii de intrare sa se faca lent astfel incat efectul timpului de propagare sa fie neglijabil.

Intrebari:

L Valorile determinate la acest punct sunt in concordanta cu cele obtinute la punctele anterioare?

L Exista diferente intre caracteristicile de transfer ale circuitelor 7404, 74S04, 74LS04?

L Care este motivul pentru care, trasarea statica a caracteristicii de transfer nu se poate utiliza, desi aceasta ar prezinta avantajul ca nu este influentata de timpul de propagare?

8. Estimarea timpilor de propagare

Timpul de propagare, sau intarzierea intre momentul aplicarii unui semnal si aparitia raspunsului, este un fenomen nedorit ce apare in functionarea portilor reale. Ordinul de marime al intarzierilor este de zeci de nanosecunde. Modul de definire a marimilor ce descriu comportamentul real, in domeniul timp, al portilor este prezentat in figura 8.

Estimarea timpilor de propagare si de front se poate face cu ajutorul osciloscopului vizulalizand simultan semnalele de intrare si iesire. Timpul de propagare mai poate fi estimat si prin masurarea falsului histerezis - amintit la punctul anterior.

Modul de lucru:

- se utilizeaza montajul anterior;

- frecventa generatorului de semnal se regleaza la 1MHz;

- comutatorul bazei de timp a osciloscopului, SEC/DIV, se aduce in pozitia 0,2 ms div;

- pentru o masurare usoara a timpilor de propagare, vom deplasa pe verticala ambele semnale, astfel icat sa fie plasate simetric fata de linia punctata din centrul ecranului osciloscopului;

- timpii de propagare se determina inmultind numarul de diviziuni orizontale dintre cele doua puncte, determinate de intersectia fronturilor cu linia punctata din centrul ecranului, cu scara de timp;

- daca este necesar se poate utiliza si lupa de timp

Continutul referatului:

Pentru fiecare punct din desfasurarea lucrarii se cer:

- rezultatele experimentale obtinute, si interpretarea lor;

- formele de unda, acolo unde este cazul, cu valorile de timp si amplitudine trasate la scara;

- raspunsul la intrbari;

Copyright © 2025 - Toate drepturile rezervate