| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

CIRCUITE INTEGRATE NUMERICE

Circuitele integrate numerice (digitale) sunt circuite integrate care primesc la intrare semnale digitale si furnizeaza la iesirile circuitului semnale numerice. Iesirea este o functie de:

- valorile intrarilor,

- starea in care se afla circuitul (la momentul de timp in care se aplica semnale la vreo intrare),

- algoritmul intern de prelucrare.

Intre doua secvente de actualizare starile iesirilor se considera ca nu se modifica de catre nici unul din elementele precizate.

Pentru a desemna circuitele numerice se folosesc acronimele CIN sau CID.

Circuitele numerice sunt sincrone daca verificarea starii intrarilor si prelucrarea semnalelor are loc ciclic la momente de timp impuse de un semnal de sincronizare (semnal de tact), indiferent de faptul ca s-a modificat sau nu s-a modificat vreo intrare.

Circuitele numerice asincrone incep prelucrarea semnalelor, la momente de timp aleatorii, moment de timp impus de modificarea vreunei intrari sau de schimbarea starii interne a circuitului.

Pentru prelucrarea semnalelor circuitul numeric are nevoie de un timp mai lung sau mai scurt, timp numit timp de raspuns sau timp de intarziere sau tp timp de propagare (a impulsului de la intrare prin sistemul de prelucrare la iesirea circuitului).

Timpul de raspuns al unui circuit numeric depinde de volumul de calcule si de viteza de comutate a dispozitivelor electronice (cu ajutorul carora a fost implementat respectivul circuit integrat), altfel spus depinde de tehnologia de realizare a CIN.

In cazul particular al circuitelor numerice integrate termenul de tehnologie nu se refera numai la procesul de realizare a circuitului ci si la elementele cu ajutorul caruia se realizeaza circuitele logice din componenta integratului.

Din acest punct de vedere exista tehnologii : [2,3]

- bipolare, care au in componenta tranzistori bipolari ;

- unipolare, care au in componenta tranzistori cu efect de camp.

Proiectarea unui dispozitiv (aparat electronic) care sa indeplineasca diferite activitati logice incepe cu proiectarea logica a dispozitivului, este urmata de etapa de implementare cu circuite integrate numerice si se continua cu verificarea si testarea functionalitatii s.a.

Etapa de implementare consta in adoptarea unor circuite numerice integrate si interconectarea acestora in scopul realizarii functiilor logice precizate in etapa anterioara. In acest scop ar trebui sa studiem foile de catalog ale miilor de producatori pentru a identifica circuitele necesare si a stabili daca pot fi interconectate (daca au aceleasi reprezentari ale cifrelor binare, daca au aceeasi sursa de alimentare, daca au un timp de raspuns corespunzator, s.a.).

Pentru a micsora efortul de implementare a dispozitivului, in cadrul fiecarei clase de tehnologii, circuitele numerice au fost grupate in serii (familii) de circuite integrate numerice standardizate, diferentiate prin gradul de integrare si caracteristicile electrice (ce vor fi evidentiate in paragraful 1).

In raport cu gradul de integrare (numarul de tranzistori implementati pe pastila integratului) circuitele digitale pot fi:

SSI Small Scale Integration), cu mai putin de 50 tranzistori;

MSI Medium Scale Integration), intre 50 si 500 tranzistori;

LSI Large Scale Integration), intre 500 si 30.000 tranzistori;

VLSI Very Large Scale Integration), peste 30.000 tranzistori;

De mentionat faptul ca, datorita complexitatii circuitelor VLSI si a functiilor diferite pe care le implementeaza, acestea nu au fost standardizate, numai ca producatorul circuitului asigura interfete de intrare / iesire care sa permita comunicarea cu exteriorul, pe baza unui standard acceptat (unul din standardele enumerate in cele ce urmeaza ).

Principalele serii de circuite integrate numerice care au rezistat dea lungul timpului sunt:

in tehnologia bipolara, seriile TTL (Transistor Transistor Logic) si ECL (Emitter Coupled Logic

in tehnologia unipolara, seriile CMOS (Complementary Metal Oxide Semiconductor), NMOS (N- channel MOS) , PMOS (P-channel MOS);

in tehnologie combinata unipolara si bipolara pe aceeasi pastila de siliciu, seria BiCMOS (Bipolar Complementary MOS).

1. Parametrii care definesc o familie de circuite integrate logice

Caracteristcile interfetei electrice a standardului se exprima luind drept element de baza circuitul logic inversor (iesirea este valoarea negata a intrarii - daca la intrare se aplica "0" iesirea va fi in "1" si reciproc) al familiei respective, specificand:

Caracteristica statica de transfer;

Marginile de imunitate la perturbatiile statice;

Capacitatea de incarcare a circuitelor logice;

Timpul de propagare;

Consumul de putere.

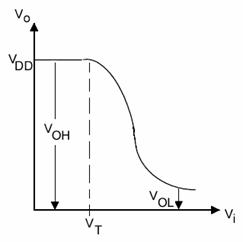

Caracteristica statica de transfer este familia de curbe care exprima dependenta tensiunii de iesire a circuitului in functie de valorile pe care le ia tensiunea de la intrare.

Se obtine o familie de curbe si nu o singura curba, ca in figura 1, deoarece cifrei "1" logic la intrare nu ii corespunde un singur nivel de tensiune ci un domeniu de tensiuni (la fel si pentru "0" logic).

Se definesc marimile: [10,11,12,13]

VILmin - nivelul de tensiune minim pentru '0' logic la intrare,

VILmax - nivelul de tensiune maxim pentru '0' logic la intrare,

VIHmin - nivelul de tensiune minim pentru '1' logic la intrare,

VIHmax - nivelul de tensiune maxim pentru '1' logic la intrare,

VOLmin - nivelul de tensiune minim pentru '0' logic la iesire,

VOLmax - nivelul de tensiune maxim pentru '0' logic la iesire,

VOHmin - nivelul de tensiune minim pentru '1' logic la iesire,

VOHmax - nivelul de tensiune maxim pentru '1' logic la iesire.

"Pentru " din fraza anterioara trebuie inteles astfel - pentru ca circuitul sa interpreteze respectiva valoare de tensiune drept "0 sau 1" logic si sa actioneze corespunzator.

Nivelele de tensiune notate cu cifre definesc zona de functionare normala in absenta perturbatiilor (VIL2 - VIL1 si VIH2 - VIH1) iar cu acolade s-au marcat zonele permise.

Intervalul (VIHmin - VILmax) reprezinta zona de tranzitie.

Marginea de imunitate la perturbatiile statice reprezinta

valoarea maxima a tensiunii perturbatoare care insumata cu semnalul util aplicat la intrare, in cazul cel mai defavorabil, nu conduce la schimbarea comportarii circuitului (in sensul ca daca la intrarea inversorului se aplica "0" iesirea devine "1" chiar si in prezenta unui semnal perturbator).

Marginea de imunitate la perturbatii garantata de producator se defineste prin diferenta nivelelor logice astfel:

pentru "0" logic ![]() ,

,

pentru "1" logic ![]() .

.

Capacitatea de incarcare a circuitelor logice se exprima prin factorul de incarcare la intrare FI (Fan-In) si respectiv factorul de incarcare la iesire FO (Fan-Out).

In cazul cel mai defavorabil curentii absorbiti de circuit de la intrare se noteaza IIL, IIH iar curentii furnizati de iesire se noteaza IOL, IOH.

Fiecare circuit conectat la iesirea circuitului logic in discutie absoarbe un curent. Suma curentilor absorbiti nu trebuie sa depaseasca curentul maxim pe care il poate furniza iesirea respectiva.

Capacitatea de incarcare a iesirii circuitului FO (Fan-Out) reprezinta numarul maxim de porti logice ce pot fi conectate la iesire fara degradarea nivelelor logice (fara ca nivelul de tensiune furnizat de iesirea portii pentru starea "1" sa scada sub pragul VOHmin) .

Din punctul de vedere al intrarii circuitului situatia se prezinta similar (pentru Fan-In).

Capacitatea de incarcare a circuitelor logice FO se exprima matematic prin valoarea cea mai mica dintre:

,

,

unde paranteza dreapta semnifica partea intreaga.

Timpul de propagare

Timpul de propagare exprima intarzierea cu care se stabileste iesirea la valoarea corespunzatoare semnalului aplicat la intrare.

Deoarece intrarea nu se modifica

instantaneu ci intr-un timp finit ![]() masurarea timpului de propagare se face, ca in figura 2.,

intre momentul cand intrarea ajunge la 50% din valoarea finala si

momentul cand iesirea ajunge la 50% din valoarea finala. Se

obtin doua intarzieri

masurarea timpului de propagare se face, ca in figura 2.,

intre momentul cand intrarea ajunge la 50% din valoarea finala si

momentul cand iesirea ajunge la 50% din valoarea finala. Se

obtin doua intarzieri ![]() - corespunzatoare caderii iesirii din H in L

si

- corespunzatoare caderii iesirii din H in L

si ![]() - corespunzatoare

cresterii semnalului de iesire

din L in starea H.

- corespunzatoare

cresterii semnalului de iesire

din L in starea H.

Uneori se calculeaza timpul mediu de propagare, ca medie aritmetica a celor doi timpi.

Consumul de putere, este in directa legatura cu valoarea tensiunii sursei de alimentare de curent continuu, asa incat se impune precizarea si a altor elemente:

tensiunea de alimentare (VCC sau VDD );

curentii absorbiti de circuit, cand iesirea este in starea '1' logic (ICCH), respectiv in starea '0' logic (ICCL);

curentul cu iesirea in scurtcircuit (IOSC);

puterea medie consumata (Pmed).

Datorita comutatiei circuitului logic dintr-o stare in alta se consuma o putere suplimentara, exprimata prin puterea necesara incarcarii / descarcarii capacitatilor parazite CP de la iesire:

![]() ,

,

putere dependenta de frecventa f a semnalului de comutare.

Puterea totala absorbita de la sursa de curent continuu este:

![]() .

.

2. Circuite integrate TTL

Familia TTL (Transistor Transistor Logic), este cea mai cunoscuta familie de circuite integrate digitale, fiind introdusa de firma Texas Instruments (SUA) in anul 1965.

Circuitele integrate sunt realizate cu tranzistori bipolari cu cuplaj direct (fara condensator de cuplaj intre etaje).

Circuitele realizate in tehnologie TTL

sunt alimentate (powered) de la o

sursa de c.c. cu valoarea VCC

= 5 V (![]() ).

).

Semnalele de la intrarea portii din domeniul 2 V,, 5 V sunt interpretate drept "1" logic iar semnalele din domeniul 0 V,, 0,8 V sunt interpretate drept "0" logic, ceea ce inseamna ca

VIHmin = 2 V , VILmax = 0,8 V.

Domeniul 0,8 V,, 2 V dintre cele doua nivele limita se numeste domeniul de incertitudine, pentru ca un nivel de tensiune din acest domeniu aplicat la intrare va determina la iesirea portii un semnal logic aleatoriu (uneori "0" si alteori "1" fara a putea fi precizat).

La iesirea portii avem urmatoarele nivele logice

VOLmax= 0,4 V, VOHmin= 2,4 V.

Producatorii de circuite integrate garanteaza, in conditii date, anumite valori limita pentru nivelele logice. Spre exemplu se garanteaza

VOHmin = 2,7 V , VILmax = 0,5 V .

Diferenta, in modul, dintre iesirea garantata a portii si nivelul logic standardizat reprezinta marginea de zgomot a portii, care

pentru "1" logic este MH (high-level noise margin) iar pentru "0" logic este ML (low-level noise margin

![]()

![]() .

.

Marginea de zgomot mai mare pentru "1" logic sugereaza recomandarea folosirii unui semnal de comutare a circuitului activ in zero logic, adica care efectueaza tranzitia din "1" logic in "0" logic atunci cand se doreste comutarea starii circuitului logic.

Necesitatile productiei de aparatura numerica si evolutia tehnologiei de realizare a circuitelor integrate au evidentiat 7 familii (serii) de circuite integrate TTL si anume:

normala, notata 74xxx pentru aplicatii comerciale si 54xxx pentru aplicatii militare;

rapida (High Speed) notata 74Hxxx este iesita din uz;

de mica putere (Low Power) notata 74Lxxx, este iesita din uz;

Schottky notata 74Sxxx pentru seria standard;

Schottky 74LSxxx pentru seria de mica putere;

Schottky 74ALSxxx pentru seria de mica putere performanta;

Schottky 74ASxxx pentru seria performanta (Advanced).

Toate seriile TTL au drept circuit fundamental poarta SI-NU.

Seria TTL normala are poarta logica fundamentala realizata cu 4 tranzistori bipolari, conectati ca in figura 3. [13,20]

Fig. 4.3.

Schema electronica se bazeaza pe tranzistorul multiemitor T1 care implementeaza functia logica SI pentru intrarile A si B.

Rezistorul R1 stabileste curentul injectat in baza tranzistorului T1.

Tranzistorul T2 amplifica in curent semnalul furnizat de tranzistorul multiemitor T1 si comanda (prin curentul care circula prin rezistorul R3) tranzistorul inversor T3 din etajul final si comanda (prin valoarea potentialului colectorului) tranzistorul T

Tranzistorul T4 are rol de sarcina activa pentru tranzistorul final asigurand o impedanta mica la tranzitia din "0" in "1" a iesirii.

Dioda D participa la formarea tensiunii baza - emitor a tranzistorului T4 impreuna cu rezistorul R2 care stabileste potentialul bazei tranzistorului T

Diodele D1 si D2 protejeaza tranzistorul multiemitor T1 la aplicarea unor tensiuni negative

Prin conventie curentul este pozitiv daca poarta absoarbe curent. Pentru poarta standard avem urmatorii curenti asociati nivelelor logice:

IIH A

IIL = -1,6 mA,

IOH A

IOL = 16 mA.

Pe

baza curentilor se obtine un factor de incarcare ![]() , ceea ce inseamna ca la iesirea portii

TTL normale se pot cupla maximum 10 intrari de porti logice.

, ceea ce inseamna ca la iesirea portii

TTL normale se pot cupla maximum 10 intrari de porti logice.

Din analiza functionarii schemei pentru diferite domenii ale tensiunii de intrare se obtine caracteristica statica din figura

In cadrul analizei consideram urmatoarele valori asociate unei diode si unui tranzistor tipic tehnologiei TTL :

![]() , caderea de tensiune pe o dioda in conductie;

, caderea de tensiune pe o dioda in conductie;

![]() , pentru zona activa de functionare;

, pentru zona activa de functionare;

![]() , pentru zona activa de functionare la saturatie;

, pentru zona activa de functionare la saturatie;

![]() , caderea de tensiune colector - emitor pentru zona de

saturatie.

, caderea de tensiune colector - emitor pentru zona de

saturatie.

Pentru domeniul 0V< Vi < 0,65 V, tranzistorul T1 este

saturat iar T2 este blocat - pentru ca tensiunea aplicata bazei este mica

![]() .

.

Va fi blocat si tranzistorul T3 deoarece curentul furnizat de T2 este foarte mic

![]() .

.

Situatia apare in conditiile cand la ambele intrari se aplica un potential mic, corespunzator lui "0" logic ( A=0, B=0). Cu teorema a doua a lui Kirchoff pentru ochiul de iesire se determina

![]() .

.

Dar  ,

,

pentru ca tranzistorul T2 este blocat, iar curentul de colector al T4 este curentul prin sarcina circuitului (IOH).

Tensiunile pe dioda si intrarea tranzistorului in conductie sunt

![]()

ceea ce inseamna ca ![]() pe toata zona AB a caracteristicii.

pe toata zona AB a caracteristicii.

Pentru 0,65 V< Vi < 1,3 V, T2 incepe sa conduca usor,

intrand in regiunea activa

normala. Amplificarea realizata pe portiunea BC de tranzistorul T2 este ![]() . Pe dreapta BC a caracteristicii T4 functioneaza ca repetor pe

emitor iar T3 este blocat.

. Pe dreapta BC a caracteristicii T4 functioneaza ca repetor pe

emitor iar T3 este blocat.

Pentru 1,3 V < Vi < 1,5V, T3 incepe sa conduca, Ve

scade mai rapid obtinand dreapta

CD.

Tranzistorii T2, T4 si T3

conduc in regiunea activa normala. Creste consumul de la sursa

de alimentare.

Pe zona 1,5 V < Vi < 2,25 V, T3 este saturat T4 iar este

blocat. Tensiunea de iesire pentru regiunea DE este

![]() .

.

Timpii de propagare specificati in datele de catalog sunt:

![]()

Consumul de putere este format din puterea de curent continuu (in jur de 10 mW) la care se adauga puterea datorata capacitatilor parazite.

Pentru o capacitate

parazita de CP = 15 pF puterea suplimentara este de 0,4

mW la frecventa de lucru de 1 MHz si creste la 7,5 mW pentru frecventa de operare de

20 MHz .

Seria TTL rapida (High Speed) notata 74Hxxx a fost implementata (conform denumirii) in scopul cresterii vitezei de comutare.

S-au obtinut timpi de propagare tp = 6 ns (fata de 10 ns la pentru seria standard).

Pentru a obtine aceasta performanta rezistorii din schema circuitului fundamental au fost micsorati , tranzistorul T4 a fost inlocuit cu un montaj Darlington, s.a.

Curentii de intrare sunt IiLM = 2 mA, IiHM = 50 A, iar puterea absorbita pe poarta ajunge la Pd = 22 mW.

Seria este iesita din uz si componentele sunt scose din fabricatie.

Seria TTL de mica putere (Low Power) notata 74Lxxx, a fost implementata (conform denumirii) in scopul scaderii puterii absorbite de circuit.

Puterea pe poata a scazut la Pd = 1,,2 mW dar timpul de propagare a crescut la tp = 20,,33 ns.

Scaderea puterii s-a obtinut prin cresterea valorilor rezistorilor din schema.

Seria este iesita din uz si componentele sunt scose din fabricatie.

Seria TTL Schottky apare din necesitatea vitezei de propagare, ceea ce s-a obtinut pe seama cresterii vitezei de comutare a elementelor active de circuit din schema electrica.

In cazul circuitelor TTL cu tranzistori bipolari NPN acestia vor stationa in blocare sau in saturatie. Tranzistorul comuta din saturatie in blocare dupa evacuarea sarcinii stocate, sarcina care este o functie de zona de saturatie a tranzistorului ( mai mare pentru tranzistor in saturatie profunda).

Pentru ca tranzistorul sa nu se mai satureze, circuitul logic a fost implementat cu tranzistori Schottky.

Tranzistorul Schottky este format dintr-un tranzistor NPN care in paralel cu jonctiunea colector - baza are o dioda Schottky.

Dioda Schottky aflata in conductie are o cadere de tensiune

Vsh =0,3,,0,4 V ceea ce inseamna ca jonctiunea colector - baza a tranzistorului NPN nu mai poate fi polarizata direct (are nevoie de o tensiune in jurul valorii de 0,65 V), adica tranzistorul nu mai poate fi adus la saturatie.

Observatie: Reamintim ca un tranzistor este la saturatie daca ambele jonctiuni sunt polarizate direct.

Dioda Schottky are caracteristica statica a unei diode PN dar este realizata prin contactul dintre o semiconductoare si o zona metalica (din aluminiu).

In figura 5 este prezentat simbolul tranzistorului Schottky, iar in figura 6 este prezentata implementarea acestuia pe pastila de siliciu.

Fig. 4.6.

In figura 7 este prezentata schema electrica a portii logice fundamentala (SI-NU) a seriei Schottky standard.

Circuitul respecta topologia portii standard (din figura 3) dar cu inlocuirea

tranzistorilor NPN cu tranzistori Schottky,

rezistorului R3 cu un rezistor neliniar format din grupul ![]() ,

,

tranzistorului T4 cu un montaj Darlington, format cu T5,T4 si rezistorul R5 .

Rezistorul neliniar are o valoare mica la comutarea tranzistorului T3 din saturatie in blocare, asigurand evacuarea rapida a sarcinii stocate in baza acestuia si are o valoare mare cand T3 primeste comanda de comutare in conductie (astfel nu se consuma din curentul de comanda care se injecteaza in baza lui T3).

Timpul de propagare scade la tp = 3 ns pentru o putere consumata pe poarta Pd = 20 mW.

Pentru poarta standard a seriei Schottky avem urmatorii curenti asociati nivelelor logice:

IIH A

IIL = - 2 mA,

IOH A

IOL = 20 mA.

(fata de curentii portii TTL standard IIH A IIL = -1,6 mA,

IOH A IOL = 16 mA).

Seria Schottky de mica putere, notata cu 74LSxxx are ce mai larga arie de utilizari.

In figura 8 este prezentata schema electrica a portii SI-NU, din seria Schottky de mica putere.

Constatam ca circuitul SI nu este realizat cu tranzistor multiemitor, ci cu ajutorul diodelor DA, DB , a rezistorului R1 si cu un tranzistor T1 defazor.

Rezistorul R5 este conectat la iesire (si nu direct la masa) pentru a elimina o sursa de consum, cand iesirea este in starea "1" logic.

Puterea disipata pe o poarta este Pd = 2 mW, pentru un timp de transfer tp = 9,5 ns.

Curentii absorbiti de intrari sunt IIH A IIL = - 0,4 mA, iar tensiunile de la iesire sunt U0LMax = 0,5 V, U0Hmin = 2,7 V.

Seriile Schottky performante, notate 74ALSxxx si 74ASxxx folosesc tehnologii mai performante pentru realizarea circuitului logic, fara a modifica schema electrica. [21]

Pentru seria AS timpul de propagare este tp = 1,7 ns iar puterea disipata pentru poarta fundamentala este Pd = 8 mW.

Pentru seria ALS timpul de propagare este tp = 4 ns, iar puterea disipata pentru poarta fundamentala este Pd = 1,2 mW.

Curentii de intrare sunt IiLMax = 2 mA si IiHMax = 0,2 mA iar tensiunea de iesire are valorile U0LMax = 0,5 V, U0Hmim = 2,7 V.

Porti TTL cu colectorul in gol OC (open collector) sunt porti logice la care se elimina etajul de iesire realizat de tranzistorul T4 sau de T4 si T5.

La proiectarea schemelor logice cu circuite OC se impune conectarea iesirii circuitului logic la sursa de alimentare prin intermediul unui rezistor.

Cu ajutorul acestui tip de porti se realizeaza functia SI cablat, prin conectarea directa a mai multor iesiri. Iesirile se leaga impreuna si printr-o rezistenta de sarcina se conecteaza la sursa de alimentare.

Erau utile la conectarea mai multor echipamente pe aceeasi magistrala, dar asigurau timpi de propagare mari si stricau fronturile semnalelor.

Mai nou se prefera utilizarea portilor logice cu trei stari.

Portile logice TTL cu trei stari (tri states) au iesirea in starea "0" logic, in starea "1" logic sau in starea de inalta impedanta HZ (High Z). Pe langa intrarile de date circuitul are o intrare specifica E (Enable) care permite comutarea circuitului in starea de inalta impedanta.

O iesire aflata in starea HZ este flotanta, nefiind influentata de modificarea intrarilor si nu afecteaza in nici un fel functionarea circuitelor conectate in punctul respectiv (la iesirea respectiva).

In figura 9 este prezentata schema de principiu a unui inversor TTL cu trei stari.

Daca intrarea E este in "1" logic pe emitorul corespunzator al tranzistorului T1 se aplica un potential ridicat care blocheaza jonctiunea baza - emitor si totodata blocheaza dioda D2. Intrarea In va conditiona conductia sau blocarea tranzistorului T1 si circuitul va functionarea ca un inversor (la iesirea Y se obtine valoarea negata a intrarii In).

Intrarea E este in "0" logic determina conductia tranzistorului T1 si a diodei D2, care dioda in conductie va determina un potential mic pe baza tranzistorului T

Tranzistorul T4 fiind blocat circuitul nu va furniza decat un curent foarte mic (zero) prin borna Y, ceea ce inseamna ca iesirea circuitului nu va afecta functionarea circuitelor conectate la borna Y si spunem ca circuitul se afla in starea de inalta impedanta HZ.

In tabelul 1 avem starile logice ale iesirii in functie de starea celor doua intrari.

Tabelul 1.

|

In |

E |

Y |

|

x |

HZ |

Semnificatia literei "x" este "orice valoare logica". Adica oricare ar fi starea intrarii In, daca E este zero, circuitul va fi in starea HZ.

Nota: Exista circuite care implementeaza cea de a treia stare pentru intrari.

3. Circuite integrate ECL

Familia ECL (emitter-coupled logic) este implementata cu tranzistoare NPN bipolare care comuta un curent mai mic decat curentul de saturatie.

Cresterea vitezei de propagare se face constructiv prin utilizarea unui etaj diferential ca circuit de baza si prin micsorarea numarului de etaje ale circuitului logic.

In figura 10 este prezentat etajul diferential cu iesirea V0 si sursa de curent constant (realizata cu T4) .

Sursa de curent constant furnizeaza un curent prin divizorul din baza

![]() .

.

Potentialul bazei este

![]()

![]() .

.

Cu care avem potentialul de referinta

![]() .

.

Curentul si tensiunea pe R3 sunt

![]()

![]() ,

, ![]() .

.

Toate valorile au fost determinate avand drept referinta sursa negativa de tensiune VEE.

Daca drept referinta se ia masa (GND) valorile devin

![]()

Valorile se mentin cat timp T1 este blocat

![]() ,

,

adica avem

![]() .

.

Inseamna ca se va comuta curentul de pe un tranzistor pe altul atunci cand potentialul punctului A este mai mic (conduce T2 si iesirea V0 este la potentialul Vcc1 ) sau mai mare (conduce T1) decat potentialul de referinta.

In figura 11 este prezentata poarta NOR (SAU NEGAT) a familiei ECL cu doua intrari.

Se remarca faptul ca a doua intrare (B) a fost conectata in paralel cu prima (A) pentru ca oricare tranzistor (T1 sau T3) sa poata prelua curentul care circula prin rezistorul R3 .

Iesirea circuitului se face prin intermediul unui repetor realizat cu tranzistorul T5 .

Familia ECL se realizeaza in doua variante, anume seria 10 K si seria 100K.

Seria 100K respecta topologia din figura 11 dar in scopul compensarii variatiei cu temperatura a elementelor intre colectorii T1 si T2 s-au implementat doua diode antiparalel. Sursa de alimentare la seria 100K este -4,5 V.

Nivelele logice sunt V0L = -1,74 V, V0H = -0,9 V.

Caracteristica statica este prezentata in figura 12.

Exista variante ale seriei 100K de viteza mare numite 101xx (tP = 3,5 ns) si 102xx (tP = 2,5 ns).

Exista o varianta a seriei 100K de viteza mare numita ECL in Pico Seconds pentru care tP = 0,1,,0,5 ns cu nivelele logice V0L = -1,7 V, V0H = -0,8 V. De notat ca alimentarea poate fi pozitiva, adica VEE = 0V si VCC = +5V.

In tabelul 2 sunt prezentate principalele caracteristicile standard ale celor doua serii.

Tabelul 2.

|

Parametrul |

10K |

100K |

|

VEE [V] | ||

|

tP [ns] | ||

|

Pd [mW] |

Circuite integrate MOS

Un circuit MOS alimentat la o sursa de curent continuu cu valoarea VCC = 5V are nivele logice limita impuse:

VIHmin = 3,5 V pentru "1" logic,

VILmax = 1,5 V pentru "0" logic.

Producatorii garanteaza la iesirea portii

VOHmin = 4,95 V pentru valoarea minima de "1" logic;

VOLmax = 0,05 V pentru valoarea maxima de "0" logic,

ceea ce determina margini de zgomot

![]() pentru "1" logic,

pentru "1" logic,

![]() pentru "0"

logic .

pentru "0"

logic .

Nota: De

fapt producatorii de circuite MOS spun ca asigura nivele de

tensiune pentru "1" logic ![]() si pentru "0"

logic

si pentru "0"

logic ![]() , dar se poate conta pe 10% din valoarea sursei de

alimentare.

, dar se poate conta pe 10% din valoarea sursei de

alimentare.

Un circuit CMOS alimentat la o sursa de c.c. cu valoarea VCC = 10 V are nivelele limita impuse:

VIHmin = 7,0 V pentru "1" logic,

VILmax = 3,0 V pentru "0" logic.

Un circuit CMOS alimentat la o sursa de c.c. cu valoarea VCC = 15 V are nivelele limita impuse si anume:

VIHmin = 11,0 V pentru "1" logic,

VILmax = 4,0 V pentru "0" logic.

Marginile de zgomot sunt:

![]() ,

,

![]() ,

,

ca in figura 13.

Marginea de zgomot este deosebit de importanta in cazul in care semnalele logice sunt formate dintr-un semnal logic curat" peste care se suprapune o tensiune de zgomot. Valorile mari ale zgomotului pot duce semnalul in zona de incertitudine, eventual circuitele pot interpreta un semnal logic drept altul. Spre exemplu in figura 14 semnalul de intrare Vi este "1" logic la valoarea de 2,4 V, peste care

s-a suprapus un zgomot cu amplitudinea maxima de 0,9V.

Pe axa timpului, in figura 14, este marcata starea iesirii circuitului, care ar trebui sa fie "1" logic, dar datorita perturbatiei semnalul de intrare, se situeaza de doua ori in zona de incertitudine si iesirea are o valoare care nu poate fi precizata ("0" sau "1").

Portile integrate MOS se clasifica pe baza tehnologiei de realizare a tranzistorului unipolar in:

P-MOS, au in componenta tranzistori cu canal P

N-MOS, au in componenta tranzistori cu canal N

C-MOS (Complementary MOS), au in componenta atat tranzistori cu canal P cat si tranzistori cu canal N;

Bi-CMOS (Bipolar CMOS)

Portile PMOS si portile NMOS nu au fost standardizate ci numai intra in componenta unor circuite integrate care implementeaza diferite functii logice.

Tranzistorii MOS cu canal n, utilizati la realizarea portilor NMOS sau (CMOS) se prezinta in figura 15, unde avem a) MOS cu canal initial cu saracire si b) MOS cu canal indus cu imbogatire.

Sunt preferati tranzistorii cu canal indus (15b) deoarece polaritatea tensiunii de intrare VGS este aceeasi cu polaritatea tensiunii de la iesire VDS.

Caracteristica statica de iesire, din figura 16, permite evidentierea regimurilor de functionare ale tranzistorului:

zona de blocare, este caracterizata prin anularea curentului de

drena (![]() ). Regimul se stabileste pentru tensiuni de intrare mai

mici ca tensiunea de taiere (

). Regimul se stabileste pentru tensiuni de intrare mai

mici ca tensiunea de taiere (![]() ).

).

zona de saturatie, este zona in care

curentul de drena (![]() )

)

este comandat de valoarea tensiunii grila - sursa (de la intrare)

![]() ,

,

unde k este o

constanta specifica calitatii realizarii fizice a

tranzistorului. Regimul se obtine pentru (![]() si

si ![]() ).

).

zona rezistiva, in care tranzistorul se comporta ca o rezistenta

(rezistenta dintre Drena si Sursa) a

carei valoare este comandata de valoarea tensiunii aplicata

intre grila si sursa. Regimul se obtine pentru tensiuni mici de alimentare (![]() cu

cu ![]() ). Nu este folosit in cazul circuitelor logice, decat ca

zona de tranzitie.

). Nu este folosit in cazul circuitelor logice, decat ca

zona de tranzitie.

Din punctul de vedre al realizarii constructive ai tranzistorilor MOS ( cu canal p sau cu canal n) exista caracteristici comune si anume faptul ca :

zona drenei si zona sursei sunt realizate cu acelasi tip de

semiconductor (de tipul N la NMOS si P la PMOS), ceea ce face ca sa se inchida intre sursa si drena un curent de electroni in cazul NMOS si un curent de goluri in cazul PMOS;

zona drenei este separata de zona sursei prin substratul

realizat de alt tip decat cele doua zone (de tipul P la NMOS si N la PMOS);

grila este separata de substrat prin intermediul unei zone

izolatoare (un oxid);

Tehnologia de realizare a tranzistorilor MOS conduce la performante mai bune pentru NMOS, motiv pentru care PMOS se intalnesc numai la realizarea structurilor complementare de tipul CMOS.

De regula circuitul caracteristic al unei tehnologii este inversorul (circuitul care primind la intrare logic forteaza iesirea in logic si invers logic la intrare determina logic la iesire).

Inversorul in tehnologie NMOS

Cea mai simpla schema de inversor in tehnologie NMOS se obtine cu un tranzistor MOS cu canal indus in drena caruia se conecteaza un rezistor, ca in figura 17.

Fig. 4.17.

Modificand valoarea tensiunii de intrare Vi se modifica tensiunea VGS = Vi iar curentul de drena creste conform caracteristicii statice de transfer din figura 15b.

Tensiunea de iesire calculata cu relatia

![]() ,

,

determina caracteristica de transfer a inversorului

din figura 18.

Fig. 4.18.

Pentru tensiuni de intrare

corespunzatoare valorii logice ![]() curentul iD prin tranzistor si prin RD este zero (vezi figura 15b,

zona pentru

curentul iD prin tranzistor si prin RD este zero (vezi figura 15b,

zona pentru ![]() ) ceea ce face ca

tranzistorul sa fie blocat si tensiunea la iesire sa

ramana la potentialul sursei de alimentare

) ceea ce face ca

tranzistorul sa fie blocat si tensiunea la iesire sa

ramana la potentialul sursei de alimentare ![]() , adica face ca iesirea sa fie logic.

, adica face ca iesirea sa fie logic.

Pentru tensiuni ![]() curentul iD creste dupa o

functie patratica cu tensiunea de intrare, motiv pentru care

tensiunea de iesire scade

curentul iD creste dupa o

functie patratica cu tensiunea de intrare, motiv pentru care

tensiunea de iesire scade ![]() , pana la V0L.

, pana la V0L.

La iesirea inversorului se va cupla intrarea unui alt circuit logic (de tipul MOS) care intrare reprezinta o sarcina capacitiva CS pentru inversor (de valoarea capacitatii de intrare a circuitului logic).

Comutarea intrarii inversorului din in logic (tranzistorul comuta din blocare in conductie ) determina descarcarea capacitatii CS prin tranzistor. Circuitul de descarcare este prezentat in figura 19a).

Iesirea inversorului comuta din in logic.

a)

b) Fig. 4.19.

Tensiunea de iesire se determina pe baza ecuatiilor circuitului (19a)

![]() ,

,

![]() ,

, ![]() ,

, ![]() ,

,

adica a ecuatiei diferentiale a circuitului:

![]() .

.

Forma de unda la descarcarea condensatorului este prezentata in figura 20 pe intervalul (0,Tu ).

Circuitul de incarcare a capacitatii CS , prin RD de la sursa de alimentare catre VDD in intervalul in care tranzistorul este blocat, este prezentat in figura 19b). Variatia tensiunii de iesire a inversorului este conform variatiei tensiunii de pe condensator

![]() ,

,

cu forma de unda prezentata in figura 20 pe intervalul (Tu, T).

Viteza de comutare depinde de constanta de timp de

incarcare a condensatorului ![]() . Condensatorul ajunge repede la valoarea finala

daca rezistorul RD are

valori mici.

. Condensatorul ajunge repede la valoarea finala

daca rezistorul RD are

valori mici.

O rezistenta RD de valoare mica determina un potential ridicat al iesirii aflata in logic (nerecomandat).

Pentru a realiza cele doua conditii contradictorii se inlocuieste RD cu o sarcina activa.(tranzistorul TS ) din figura 21.

Sarcina activa este un tranzistor cu MOS cu canal

initial cu saracire la care grila este conectata la

sursa. Se contata ca avem un curent nenul prin tranzistor chiar

la ![]() (vezi caracteristica statica din figura 15a).

(vezi caracteristica statica din figura 15a).

Tranzistorul TS se comporta ca o rezistenta avand doua valori distincte si anume o valoare mica atunci cand tranzistorul T este in conductie (tensiune de intrare Vi corespunzatoare valorii "1" logic) si o valoare foarte mare la blocarea tranzistorului T.

Sarcina activa va imbunatati fronturile impulsurilor de la iesirea inversorului.

La comutarea iesirii din "0" in "1" logic

tranzistorul T va comuta din zona

activa in blocare. Tranzistorul TS

fiind in conductie va prezenta o rezistenta RS de valoare mica, rezistenta prin care

se va incarca (rapid) capacitatea

de intrare Cin a

circuitului logic cuplat la iesirea inversorului. Rezistenta fiind

mica, contanta de timp ![]() va fi mica

si viteza de crestere a tensiunii de iesire va fi mare (timpul

de stabilire a regimului permanent este

va fi mica

si viteza de crestere a tensiunii de iesire va fi mare (timpul

de stabilire a regimului permanent este ![]() ).

).

Inversorul in tehnologie CMOS

Inversorul CMOS are in componenta doi tranzistori complementari unul cu canal n (Tn ) si celalalt cu canal p (Tp ), conectati ca in figura 22. [29]

Caracteristicile statice de transfer pentru tranzistorii Tn si Tp sunt prezentate in figura 23.

Fig. 4.23.

Conform caracteristicilor statice constatam ca

in domeniul ![]() niciun tranzistor nu

este in conductie. Tehnologic cele doua tensiuni de prag sunt egale

(si de semn contrar)

niciun tranzistor nu

este in conductie. Tehnologic cele doua tensiuni de prag sunt egale

(si de semn contrar) ![]() .

.

In cazul seriei normale 4000 tensiunea de prag este VT = 1,5 V (in 1972 cand s-a lansat seria) apoi progresele tehnologice au scazut valoarea tensiunii de prag la VT = 1,0 V.

Nota: In cadrul figurii 23, pe langa caracteristicile statice ale tranzistorilor MOS, sunt prezente simbolurile tranzistorilor intr-o varianta simplificata (varianta similara tranzistorilor cu jonctiuni).

Schema inversorului din figura 22 este prezentata a) cu reprezentarea normala a tranzistorilor si b) cu reprezentarea simplificata a tranzistorilor MOS, reprezentare care va fi folosita in continuare.

Tensiunea VGSp este ceea ce ramane din tensiunea de alimentare dupa ce s-a scazut tensiunea Vi aplicata la intrarea inversorului, diferenta luata cu semnul minus.

Daca Vi = 0 tranzistorul Tn este blocat iar VGSp = - VDD iar tranzistorul Tp este in conductie. Iesirea este in "1" logic si Tp furnizeaza curent circuitului conectat la iesirea inversorului.

Daca Vi > VT tranzistorul Tn este in conductie iar VGSp are valori mai mici decat VT ceea ce face ca Tp sa se blocheze.

Se constata ca cei doi tranzistori conduc pe rand curentul electric de conductie.

De fapt caracteristica statica a inversorului, pe langa cele doua zone stabile a si b (prezentate mai sus) in care un tranzistor este blocat iar celalalt in conductie, are in compunere si zona de tranzitie c , ca in figura 2

Vi Fig. 4.24.

Zona de tranzitie corespunde, la cresterea tensiunii de intrare, comutarii tranzistorului Tn din blocare in conductie si comutarii tranzistorului Tp din conductie in blocare.

Seria normala 4000 pentru circuite logice CMOS, la tensiuni de alimentare VDD = 3,,15 V (fara a depasi 18 V), are nivelele logice:

la iesire V0Hmin =VDD - 0,5 V, V0Lmax = 0,05 V,

la intrare VIHmin = 0,7 VDD , VILmax = 0,3 VDD,

Deoarece tranzistorii au tensiuni de prag VT = 1,5, . ,1,0 V tensiunea

de alimentare nu poate fi scazuta sub 2 V (![]() ).

).

Marginea de zgomot este aceeasi :

ML =VILmax- V0Lmax = 0,3 VDD,

MH =V0Hmin - VIHmin = 0,3 VDD.

Timpul de propagare si puterea disipata in regim static depinde de materialul portii:

tp =

60 ns , ![]() , pentru poarta de Al,

, pentru poarta de Al,

tp =

40 ns, ![]() , pentru poarta de

Si.

, pentru poarta de

Si.

Timpul de propagare limiteaza frecventa de operare a circuitului la aproximativ 10 MHz (pentru tp = 100 ns).

Curentii de intrare au valori foarte mici si aume

![]() ,

,

iar valoarea maxima a curentului de iesire este

![]() .

.

Factorul de bransament (n) reprezinta numarul

maxim de porti care pot fi cuplate la iesirea unei porti logice.

Este limitat de regimul dinamic al circuitului la n = 50 si nu de valoarea curentului absorbit de intrari (![]() ).

).

Seria rapida (High speed - CMOS) 74HC si 74HCT

Circuitele din seria rapida asigura timpi de

propagare de tp = 9 ns la VDD

= 5 V (fata de seria

normala la care ![]() ) la o putere disipata de

) la o putere disipata de ![]() .

.

Cele doua marcaje (HC , HCT) din seria rapida CMOS difera prin valoarea tensiunii de alimentare. Pentru HC VDD =2,,6 V si pentru seria HCT VDD =4,5,,5,5 V. In plus seria HC nu poate fi comandata de circuite TTL (dar poate comanda sarcini TTL) pe cand seria HCT poate fi comandata de circuite TTL si poate comanda sarcini TTL (spunem ca este TTL compatibila).

Curentul de iesire maxim este:

I = 4 mA la HC,

I = 6 mA la HCT.

Exista serii realizate in tehnologie CMOS dar la care intrarea nu respecta standardul nivelelor logice de mai sus. Astfel exista serii CMOS cu intrari TTL numite 74FCT (Fast - CMOS), 74ACT 74AHCT (Advanced - High speed - CMOS) s.a.

Seria rapida (Advanced - CMOS) 74AHC, 74AHCT , 74ACT

Circuitele AHC folosesc o sursa de alimentare VDD= 2,0,,5,5 V.

Circuitele AHCT folosesc o sursa de alimentare VDD= 4,5,,5,5 V. Nivelele logice la VDD = 4,5 V sunt:

la iesire V0Hmin =VDD - 0,1 V, V0Lmax = 0,1 V,

la intrare VIHmin = 2,0 V , VILmax = 0,8 V,

marginea de zgomot MH = 2,4 V , ML = 0,7 V .

Iesirea in curent a circuitului este de I0max = 8 mA, putand comanda numai doua porti logice TTL (dar poate comanda foarte multe porti logice MOS, spre exemplu mai mult de 50 porti).

Timpul de propagare este tP = 3,7 ns, ceea ce permite circuitului sa functioneze pana la frecvente de 170 MHz.

De fapt seria rapida (Advanced) a fost gandita in scopul inlocuirii seriei rapide in conditiile utilizarii unor surse de alimentare de tensiune continua redusa (VDD= 3,3 V) pentru cresterea performantelor in regim dinamic si in regim static.[15]

Pentru VDD= 3,3 V iesirea in curent a circuitului este de I0max = 4 mA.

Tensiunile de prag ale tranzistorilor au fost

scazute la ![]() pentru seria AHC

si la

pentru seria AHC

si la ![]() pentru seria AHCT.

pentru seria AHCT.

Circuitele ACT

sunt caracterizate prin tP = 5 ns, la ![]() , ceea ce permite circuitului sa functioneze

pana la frecvente de 160 MHz.

Iesirea in curent a circuitului are valori mari, de pana la I0max = 24 mA.

, ceea ce permite circuitului sa functioneze

pana la frecvente de 160 MHz.

Iesirea in curent a circuitului are valori mari, de pana la I0max = 24 mA.

S-au realizat serii cu tensiune de alimentare redusa" LV (Low

Voltage) in scopul utilizarii in scheme electronice de comanda

alimentate la tensiuni mai joase de 5 V (tensiuni

de alimentare standardizate ![]() ,

, ![]() ,

, ![]() ), de regula

pentru aparate portabile a caror sursa de energie este un acumulator.

), de regula

pentru aparate portabile a caror sursa de energie este un acumulator.

Aparitia seriilor cu tensiuni de alimentare reduse

are o justificare tehnologica in sensul ca scaderea ariei pe

care sunt implementati tranzistorii conduce la scaderea

fiabilitatii circuitului logic alimentat la tensiuni mari. Astfel un

CI realizat in tehnologia ![]() nu va mai

functiona stabil la 5 V ci numai

la o tensiune de alimentare de 3,3 V,

iar unul realizat in tehnologia

nu va mai

functiona stabil la 5 V ci numai

la o tensiune de alimentare de 3,3 V,

iar unul realizat in tehnologia ![]() va trebui alimentat la

2,5 V.

va trebui alimentat la

2,5 V.

In aceasta categorie se incadreaza circuitele 74LV (Low Voltage), 74LVC, 74ALVC (Advanced Low-Voltage CMOS), 74AVC (Advanced Very-low-voltage CMOS), 74AUC (Advanced Ultra low voltage CMOS).

In tabelul 3 sunt prezentate principalele caracteristici ale circuitelor din seria cu tensiune de alimentare redusa.

Tabelul 3.

|

Circuitul |

74LV |

74LVC |

74ALVC |

74AVC |

74AUC |

|

Domeniul VDD [V] |

|

|

|

| |

|

tP [ns] | |||||

|

I0max [mA] | |||||

|

tP si I0max pentru VDD |

3.3 V |

3.3 V |

3.3 V |

1.8 V/ 2.5 V |

1.8 V |

Scaderea tensiunii de alimentare modifica valorile tensiunilor asociate nivelelor logice.

Spre exemplu in cazul circuitelor din seria 74ALVC,

pentru o tensiune de alimentare de VDD = 3,3 V , valoarea maxima

de "0" logic este ![]() iar valoarea

minima asociata starii "1" logic este

iar valoarea

minima asociata starii "1" logic este ![]() . Timpul de propagare a semnalului de la intrare la

iesire este de

. Timpul de propagare a semnalului de la intrare la

iesire este de ![]() .

.

Seriile 74LCX

si 74VCX difera prin

valorile permise ale tensiunilor de alimentare, prima are ![]() iar a doua

iar a doua ![]() .

.

5. Circuite integrate BiCMOS

Tehnologia BiCMOS implementeaza circuite si porti logice capabile sa furnizeze curenti mai mari sarcinii (decat circuitele realizate in tehnologie MOS).

Etajele de intrare, care prelucreaza semnalele in scopul realizarii functiei logice a circuitului, sunt in tehnologie MOS iar etajele de iesire sunt realizate in tehnologia bipolara (tranzistorii bipolari pot sa furnizeze curenti mai mari decat tranzistorii MOS).

Inversorul in tehnologie BiCMOS

In figura 25 este prezentata schema de principiu a unui inversor in tehnologie BiCMOS. [29,30]

Functia de inversor este implementata prin intermediul

tranzistorului Tn de tipul MOS cu canal n. Grupul de tranzistori T1

si T2

constituie un montaj Darlington care asigura amplificarea in curent (de ![]() ori) a curentului

furnizat bazei tranzistorului T1

de rezistorul R (conectat la sursa de alimentare).

ori) a curentului

furnizat bazei tranzistorului T1

de rezistorul R (conectat la sursa de alimentare).

Daca tensiunea aplicata la intrare Vi este mare ("1" logic) tranzistorul Tn este in conductie determinand o cadere de tensiune pe rezistorul R (conectat la sursa tranzistorului) suficient de mare pentru a aduce in zona de conductie tranzistorul T3 . Tensiunea de pe iesirea inversorului V0 este tensiunea colector - emitor a tranzistorului T3 , de valoare mica, ceea ce corespunde nivelului "0" logic.

Daca tensiunea Vi

aplicata la intrarea inversorului este mica ("0" logic) tranzistorul Tn este blocat. Prin rezistorul R (conectat la sursa de alimentare VDD ) in baza

tranzistorului T1 se injecteaza un curent care comanda

tranzistorul T2 .

Tensiunea V0 la

iesirea inversorului este dependenta de curentul I0 absorbit de sarcina ![]() .

.

O alta schema de principiu pentru un inversor BiCMOS foloseste doi tranzistori MOS, ca in figura 26.

Fig. 4.26.

Daca Vi este mare ("1" logic) tranzistorul Tn este in conductie determinand o cadere de tensiune pe rezistorul R1 suficienta pentru a aduce in zona de conductie tranzistorul T1, ceea ce face ca iesirea V0 sa fie in "0" logic. Curentul de sarcina I0L se va inchide prin tranzistorul T1 catre masa. Tranzistorul Tp este blocat de tensiunea de intrare si T2 est blocat de Tp.

Daca Vi este mica ("0" logic) tranzistorul Tp este in conductie determinand o cadere de tensiune pe rezistorul R2 suficienta pentru a aduce in zona de conductie tranzistorul T2, ceea ce face ca iesirea V0 sa fie in "1" logic. Curentul de sarcina I0H se va inchide prin tranzistorul T2 , sursa de alimentare VDD si sarcina.

Rezistorii permit evacuarea sarcinii din bazele tranzistorilor bipolari determinand o crestere a vitezei de comutare (din conductie in blocare).

Din clasa circuitelor logice realizate in tehnologia BiCMOS enumeram: 74ABT (Advanced BiCMOS Technology) , 74BCT (Fast CMOS Technology) ,74BCT (BiCMOS Technology), 74LVT (Low-Voltage BiCMOS Technology), 74ALVT (Advanced Low-Voltage BiCMOS Technology), MB (Multibyte) si 74ALB (Advanced Low-voltage BiCMOS) s.a.

In tabelul 4 sunt prezentate principalele caracteristici ale circuitelor din seria BiCMOS, pentru cateva familii.

Tabelul

|

Circuitul |

74ABT |

74BCT |

74LVT |

74ALVT |

74ALB |

|

Domeniul VDD [V] | |||||

|

tP [ns] | |||||

|

I0H/I0L [mA] | |||||

|

tP si I0max pentru VDD = |

3.3 V |

5 V |

3,3 V |

2.5 V |

3,3 V |

In tehnologie BiCMOS s-au implementat si circuite

cu tensiune de alimentare redusa". Astfel seria 74ALB (Advanced Low Voltage BiCMOS ) este realizata care pentru tensiuni de

alimentare de ![]() , are timpi de

propagare de

, are timpi de

propagare de ![]() si

furnizeaza la iesire (pentru oricare din starile logice) un

curent de 25 mA.

si

furnizeaza la iesire (pentru oricare din starile logice) un

curent de 25 mA.

De notat faptul ca circuitele integrate, din familiile mai sus enuntate, pe langa functiile logice corespunzatoare tipului de poarta mai au implementate si alte functii ( spre exemplu functia "Bus Hold", functia "Power up Tristate" sau functia "Pull up").

Copyright © 2025 - Toate drepturile rezervate