| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

TEORIE:

PROBLEME:

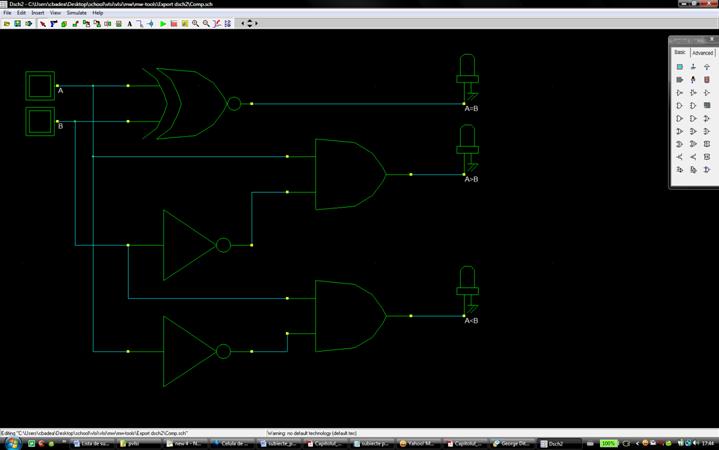

2002: Sa se implementeze o unitate UAL cu PLA conform

schemei:

Se cer:

- schema la nivel de porti & tranzistoare

- programarea PLA

- sincronizarea

2003: un sumator pe 1 bit cu transport care vine de la un circuit de memorare

2004, 2006: Sa se proiecteze o unitate aritmetica logica cu PLA. UAL executa urmatoarele operatii:

-suma xi+yi+ci

- xi.yi

- xi+yi

- x xor y

Se cere: tabela de executie, schema la nivel de tranzistoare.

2006: Sa se proiecteze o unitate

aritmetica logica cu PLA

Cerinte:

1. schema bloc (cap 11, figura cu 16 casute), schema de comanda

2. descrieti fiecare bloc in parte

3. operatiile de adunare, scadere, suma % 2, suma logica, produs logic (tabelul

de pe la sf cap 11)

R:

Pe durata tranzitiei nivelurilor logice de la 0 → 1 sau de la 1 → 0 exista momente in care cele doua tranzistoare conduc simultan, formand o cale pentru curent, de la VDD la masa, ceea ce da nastere unui varf de curent. Puterea disipata in tranzitia la comutatie poate fi evaluata cu ajutorul figurii de mai jos. Cazul cel mai defavorabil presupune ca circuitul opereaza la frecventa maxima/perioada minima (tf + tr). Se va presupune ca curentul maxim Imax curge conform traiectorie de tranzitie la comutatie de mai jos:

Presupunand:

![]()

Rezulta:

![]()

Limita superioara a energiei disipate pe durata unui ciclu devine:

Puterea disipata nu va disparea, daca creste perioada. In cazul in care timpii de crestere si cadere cresc, puterea disipata poate varia ca VDD. Circuitele care au tendinta de a consuma putere mare la comutare pot fi esantionate.

R:

XOR-ul pasiv - este o versiune a XOR-ului care se caracterizeaza printr-o arie ocupata mai mica (utilizeaza doar 6 tranzistoare), si prin folosirea portilor de transmisie. Se poate observa inversorul de pe intrarea A, structura care seamna cu un inversor pe intrarea B si poarta de transmisie in centrul circuitului.

Analiza celor patru cazuri posibile pentru semnalele logice de la intrare:

. A=0, B=0. Aceasta face ca punctul 1 sa aibe valoarea logica 0 si punctul 2 - valoarea 1, ceea ce va face ca poarta de transmisie sa fie in conductie. Prin aceasta se creaza o cale de la B la VOUT, prin poarta de transmisie. Intrucat B este la 0 sau la masa, VOUT =0

. A=0, B=1. Din nou punctele 1 si 2 au valorile 0 si respectiv 1. Poarta de transmisie conduce ceea ce face ca intrarea 1, de la B, sa se propage catre VOUT. Astfel, VOUT = 1.

. A=1, B=0. Punctele 1 si 2 au valorile 1 si respectiv 0. Poarta de transmisie este blocata, iar inversorul corespunzator intrarii B va fi operational. Deoarece B=0 si A=1, iesirea VOUT va avea valoarea 1.

. A=1, B=1. Acest caz este similar cu cel de mai sus, cu mentiunea ca inversorul corespunzator intrarii B va face ca VOUT = 0.

R:

Reprezentarea abstracta a lantului de transport:

R:

Interfata Literal:

R:

R:

Exemplu de microprogramare a inmultirii Z ←X xY, pe 16 biti:

R:

Incarcarea sarcinilor capacitive mari. Adesea este necesara incarcarea unor sarcini capacitive mari cum sunt liniile lungi, ploturile de I/E si sarcinile capacitive conectate la terminelele circuitelor. Se reaminteste ca valoarea capacitatii unei porti poate fi de ordinula a 0.01 pF , in timp ce sarcina capacitiva din afara circuitului integrat paote avea zeci de pF . Incercarea de a comanda o asemenea sarcina capacitiva cu un inversor elementar ar necesita intervale de timp de ordinul secundelor. O solutie ar consta in conectarea in cascada a unor inversoare din ce in ce mai puternice, capabile sa conduca curenti din ce in ce mai mari, ca in figura de mai jos.

Intarzierea pentru un etaj inversor dat este proportionala cu sarcina capacitiva vazuta de acel inversor si invers proportionala cu β etajului. Intarzierea totala este:

![]()

intrucat atat β, cat si sarcina capacitiva vazuta de fiecare etaj se scaleaza cu α. Deoarece,

![]()

N poate fi extras si introdus in τN, pentru a obtine

![]()

Aceasta expresie ia valoarea minima atunci cand α = e, ceea ce implica utilizarea unor ln(CL/CG) etaje succesive, adica 6-7 etaje, pentru cazul de mai sus.

R:

Circuitul de I/E conectat la un plot bidirectional TS:

14.

15.

13.

Copyright © 2025 - Toate drepturile rezervate