| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

Circuite integrate

1 Generalitati

Circuitele integrate reprezinta o clasa aparte de circuite electronice de uz general sau specializate ale caror componente active si pasive sunt realizate prin diverse procedee tehnologice intr-un volum dat de material semiconductor numit cip.

Principalele avantaje ale circuitelor integrate care determina o dezvoltare explosiva a acestora, sunt:

miniaturizarea exprimata prin reducerea cu trei - patru ordine de marime a dimensiunilor fata de aceleasi circuite realizate cu componente discrete;

cresterea fiabilitatii in special prin reducerea numarului de interconectari;

pret de cost redus datorita tehnologiilor ce permit realizarea simultana pe aceeasi placheta de semiconductori a unui numar mare de circuite integrate identice.

Circuitele integrate prezinta insa si o serie de limitari fata de circuitele cu componente discrete:

restrictii privind realizarea in tehnologie integrata a rezistentelor si capacitatilor de valori mari;

excluderea practic totala a realizarii in tehnologie integrala a inductantelor; aceste doua restrictii severe impun conceperea schemelor circuitelor integrate astfel incat sa cuprinda un numar mare de tranzistoare si cat mai putin elemente pasive;

limitarea puterii semnalelor ce pot fi prelucrate, datorita nivelului redus al puterii disipate admise a fiecarei componente, mai ales in cazul circuitelor cu densitati de integrare mari.

In prezent exista un numar mare de tipuri de circuite integrate ce se pot clasifica conform mai multor criterii, cele mai folosite fiind: dupa natura semnalelor prelucrate (Fig. 1a) si dupa tehnologia de realizare (Fig. 1 b).

a)

b)

Fig.1

Circuite integrate analogice prelucreaza semnalele cu variatie continua in timp si functie de relatia de legatura intre semnalul de iesire si semnalul de intrare pot fi liniare sau neliniare.

Datorita caracterului neliniar al dispozitivelor active din compunere (tranzistoare) circuitele din prima categorie sunt suficient de liniare pe domenii de functionare limitate. Cele mai raspandite tipuri de circuite integrate liniare sunt:amplificatoarele,stabilizatoarele,circuite de tip PL.L (circuite calare de faza) etc.

Categoria circuitelor integrate neliniare este reprezentata de multiplicatoare, circuitele de logaritmare,circuite pentru calculul functiilor trigonometrice,circuite pentru calculul valorii metrice patratice, etc.

Circuitele numerice sau logice prelucreaza semnale binare care pot lua doar doua valori corespunzatoare starilor de blocare sau conductie ale unui tranzistor si care pot reprezenta numerele 1 sau 0.

Din punct de vedere tehnologic circuitele integrate pot fi realizate sub forma monolitica (obtinute integral pe aceiasi placuta de material semiconductor) sau sub forma hibrida.

Tehnologia bipolara se bazeaza pe utilizarea tranzistoarelor bipolare planar - epitexiale obtinute printr-o succesiune de etape de fotomascare, difuziune si crestere epitaxiala aplicate unei placute de material semiconductor. Machetele de siliciu de tip pp de exemplu se obtin dintr-un monocristal masiv cu diametrul de 8 - 10 cm prin taierea in rondele cu grosimi de 250 - 300 µm si polizarea pe o fata a acestora.

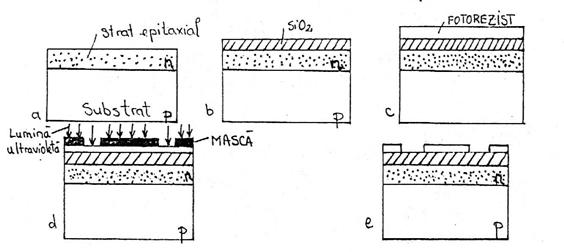

Cresterea epitaxiala consta in formarea pe placheta de siliciu numita substrat a unui strat de siliciu avand concentratie de impuritati diferita de cel a substratului (Fig. 2a). Cresterea acestui strat de grosime de 1 - 20µm se realizeaza prin plasarea plachetei intr-o atmosfera de tetradorura de siliciu (SiCl4) la temperatura ridicata. In urma reactiei chimice ce are loc in aceste conditii rezulta siliciu de tip n care se depune pe suprafata plachetei. Placheta se plaseaza in continuare intr-un mediu oxidant la temperatura inalta pe suprafata acesteia formandu-se un strat de bioxid de siliciu (SiO2) cu grosimea de 0,2 - 1µm care este impermeabil la difuzia impuritatilor (Fig.2b). Urmatoarea etapa consta in acoperirea plachetei cu un strat subtire material flexibil denumit fotorezist (Fig.2c).

Prin expunerea la o anumita lungime de unda (de regula spectrul ultraviolet ) fotorezistorul devine solubil la anumiti solventi in care fotorezistorul neexpus nu e solubil. Expunerea se face prin intermediul unei masti de dimensiunile plachetei, opaca cu exceptia zonelor unde urmeaza sa aiba loc difuzia impuritatilor (Fig. 2d).

Difuzia in stare solida a impuritatilor in siliciu consta in deplasarea la temperaturi inalte a atomilor de impuritati de la suprafata plachetei in volumul acesteia. Adancimea de difuziune este controlabila si poate fi de la 0,1 - 20µm. Dupa indepartarea fotorezistorului din ariile in care acesta a devenit solubil (Fig. 1e), placheta se dispune intr-un mediu corosiv (amestec de fluorura de amoniu si acid florhidric), bioxidul de siliciu fiind indepartat de pe ariile selectate prin masca.

Fig. 2

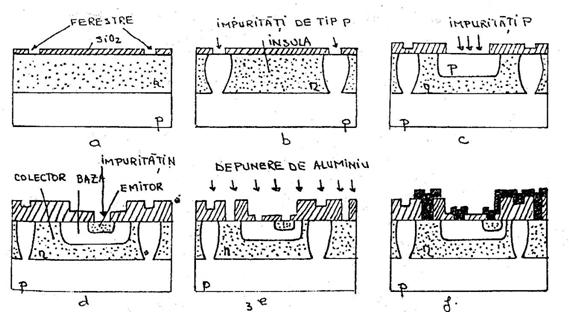

Dupa corodare ariile de fotorezist corespunzatoarelor zonelor opace ale mastii sunt indepartate chimic si placheta ramane cu asa numitele "ferestre" deschise in oxid in locurile dorite (Fig. 3 a).

In Fig.3 sunt redate simplificat restul etapelor de parcurs pentru realizarea unui circuit integrat bipolar, luand in considere doar zona de implementare a uni tranzistor npn.

Difuzia cu impuritati de tip p reprezentata in Fig. 3 b este destinata pentru izolarea unor "insule" de siliciu de tip n in al caror volum se realizeaza tranzistoarele (insulele delimiteaza chiar colectoarele acestora) sau difuziune adanca ce trebuie sa penetreze stratul epitaxial, aceasta necesita o durata de cateva ore.

In etapa urmatoare se creste un nou strat de oxid folosind o noua masca se realizeaza difuzia de baza tot cu impuritati de tip p (Fig. 3 c) dar cu o adancime mult mai mica de la 1 la 3µm. Prin aceasta difuziune se formeaza si o mare parte din rezistoarele circuitului.

Dupa cresterea altui strat de oxid si o noua mascare se formeaza prin difuziune cu impuritati de tip n emitoarele tranzistoarelor (Fig.3 d) adancimea de difuziune fiind in acest caz 0,5 la 2,5µm.

Urmatoarea etapa de mascare sete destinata sa deschida ferestre de contact in oxid in zonele de emitor, baza, colector ale tranzistoarelor precum si pentru terminalele elementelor pasive de circuit (Fig.3 e).

Intreaga placheta este acoperita apoi cu un strat subtire (aproximativ 1µm) de aluminiu care conecteaza practic in scurtcircuit toate elementele din circuit. Definirea traseelor de metalizare se realizeaza printr-o ultima etapa de mascare neprecedata de aceasta data si de o crestere a stratului de oxid.

Aluminiul este corodat in zonele in care fotorezistorul a devenit solubil prin expunere (in Fig.3 f s-a propus interconectarea emitorului tranzistorului central cu colectorul tranzistorului din dreapta acestuia).

Fig.3

In fiecare din etapele tehnologiei planar - epitexiale prezentate mai sus mastile joaca un rol important. Acestea se proiecteaza pornind de la schema electrica a circuitului ce urmeaza a fi realizat. Fiecarui element de circuit activ sau pasiv i se aloca o arie pe care se realizeaza initial insula izolata si apoi structurile propriu - zise. Fiecare etapa a procesului tehnologic se realizeaza folosind o masca corespunzatoare existand in acest sens masti pentru difuzii de izolare de baza si respectiv de emitor si masti de interconectare. Intr-o prima faza aceste masti se realizeaza la scara mare (de exemplu 500 :1) pe un material plastic special numit rubilit format dintr-o folie transparenta suprapusa peste o folie opaca. Desenul se realizeaza cu ajutorul unui aparat comandat de calculator numit coordinatograf, prin taierea si indepartarea foliei opace din zonele ce urmeaza a fi supuse difuziei. Pe o masca se gasesc alaturate atatea imagini identice cate circuite vor fi realizate pe placheta de siliciu.

Mastile sunt micsorate fotografic succesiv pana ajung la dimensiunile reale ale plachetei. Aceste masti de mici dimensiuni folosite efectiv in procesul tehnologic se numesc copii de lucru.

Masca de interconectare permite realizarea la marginea fiecarui circuit a unor arii metalice mai mari numite poduri folosite pentru conectarea exterioara. La sfarsitul etapei de corodare a peliculei de aluminiu circuitul integrat este realizat si urmeaza incapsularea sa.

Datorita ariei reduse ocupate de circuitul integrat (aproximativ 5 mm2)este posibila realizarea simultana a sutelor de circuite integrate identice pe o singura placheta. Urmeaza testarea pe placheta a fiecarui circuit integrat efectuata cu ajutorul calculatorului prin conectarea schemei de testare la podurile fiecarui circuit. Daca un circuit nu corespunde parametrilor impusi acesta se marcheaza cu o picatura de cerneala. In final placheta se separa in placute numite cipuri, corespunzatoare fiecarui circuit in parte. Aceste cipuri se monteaza pe o grila metalica ce incorporeaza contactele exterioare (pinii) circuitului si se fac legaturile cu fire subtiri de aur de la podurile cipului la pini. Urmeaza incapsularea si testarea finala a circuitelor integrate astfel obtine.

Tehnologia unipolara se bazeaza pe utilizarea tranzistoarelor MOS sau JFET si se realizeaza printr-un proces asemanator celei bipolare la care se adauga pentru tranzistoarele MOS de exemplu o etapa suplimentara de mascare destinata cresterii stratului izolator de SiO2 ce separa contactul grilei de canal.

Pentru realizarea circuitelor integrate analogice se foloseste pe scara larga tehnologia bipolara si intr-o masura mult mai mica cea unipolara datorita in special unei pante jos mai mici fata de cea a tranzistoarelor bipolare. In prezent se realizeaza circuite integrate analogice de tip BIFET si care utilizeaza tranzistoare bipolare si tranzistoare cu efect de camp cu jonctiune, posibil de realizat pe acelasi cip in cadrul aceluiasi proces tehnologic folosind astfel avantajele ambelor tipuri de tranzistoare. Situatia este oarecum diferita in domeniu circuitelor integrate numerice,unde productia e impartita aproximativ egal,intre tehnologia bipolara care ofera viteza mare si cea unipolara care permite o densitate de integrare mai mare si consum de putere mult mai mic.

Circuitele integrate hibride sunt circuite la care rezistoarele,conductoarele si unele condensatoare sunt realizate fie prin tehnologia straturilor groase,fie prin tehnologia straturilor subtiri,iar dispozitivele active (tranzistoare,circuite integrate) sau pasive neintegrabile (condensatoare sau rezistente de valori mari, inductante) se ataseaza fara capsula printr-un proces tehnologic separat.

Straturile groase sunt materiale conducatoare,dielectrice sau rezistive cu grosimi mai mari de 5 mm,care se obtin prin ardere controlata a unor paste depuse pe un substrat ceramic in conFiguratia dorita. Depunerea se face prin intermediul unor site fine ale carui ochiuri sunt astupate selectiv cu emulsie printr-un procedeu fotografic in regiunile in care pasta nu trebuie dispusa pe substrat.

Straturile subtiri au grosimi sub 5mm si se obtin prin depunerea selectiva in vid pe un substrat de ceramica sau sticla prin intermediul unor masti asemanatoare celor folosite in tehnologia bipolara.

In continuare elementele active de circuit se ataseaza din exterior prin termocompresie sau lipire ultra sonica, dupa care se separa circuitele individuale prin zgariere si spargere controlata a substratului.

In final cipurile obtinute prin separare se incapsuleaza de regula prin acoperire cu rasini expoxidice si se testeaza. In general tehnologia hibrida se foloseste pentru realizarea circuitelor analogice asigurand, cu pretul unor dimensiuni mai mari fata de circuitele monolitice,performante superioare acestora :

disipare termica superioara,deci puteri mai mari ;

precizie mare datorita posibilitatilor de ajustare functionala a valorilor elementelor pasive de circuit prin indepartarea controlata a unei parti din straturile depuse cu ajutorul unui fascicol de laser ;

frecvente de lucru mari de ordinul megahertzilor prin folosirea componentelor speciale de microunde.

Aceste performante superioare se obtin folosind tehnologia straturilor subtiri la un pret de cost mai ridicat datorita complexitatii procesului tehnologic,pe cand tehnologia straturilor groase asigura performante mai reduse sau preturi avantajoase.

2. Amplificatoare operationale

Unul dintre cele mai folosite tipuri de circuite integrate liniare este amplificatorul operational. Amplificatorul operational e un circuit cu intrare diferentiala (simetrica) si iesire asimetrica, avand castig mare in tensiune si care se foloseste de obicei in configuratii cu reactie.

Denumirea de " operatiuni " provine de la faptul ca initial s-a folosit intr-o realizare analogic al a unor operatii matematice ca adunarea, scaderea, integrarea, derivarea, etc.

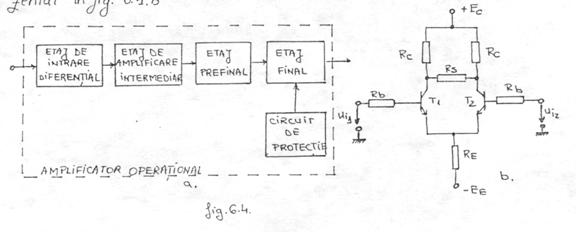

Structura tipica a unui circuit operational e redata in Fig. 4 a. Desi nu sunt toate reprezentate in figura 4 a un amplificator operational legat cuprinde in principiu urmatoarele circuite:

- etajul de intrare: este un etaj diferential destinat sa asigure o impedanta de intrare mare, o amplificare in tensiune moderata si eventual o limitare a semnalului de intrare;

- etajele de amplificare intermediare: asigura o amplificare mare in tensiune; la fel ca si etajul de intrare functioneaza liniar in regim de semnal mic ;

- etajul prefinal si etajul final asigura puterea specificata in sarcina precum si o impedanta de iesire cat mai mica; spre deosebire de etajele anterioare acestea lucreaza in regim de semnal mare;

- circuitele de deplasare a nivelului de curent continuu, destinate sa asigure compatibilitatea intre nivelul de iesire al unui etaj si cel de la intrarea etajului urmator, sunt impuse de cuplajul direct intre etaje utilizat datorita imposibilitati realizari de condensatoare de cuplaj de valori mari in tehnologie integrata ;

- surse de curent realizate cu tranzistoare si folosite fie pentru polarizarea unor etaje, fie ca sarcini active (de impedanta mare) ;

- circuite de protectie termica sau la suprasarcina care actioneaza asupra etajului final.

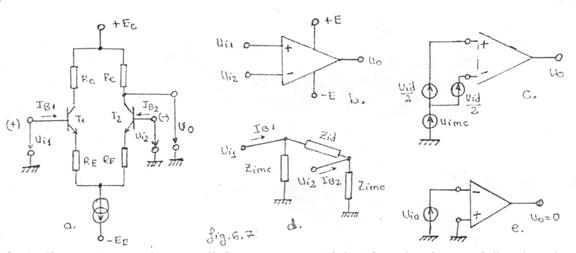

Etajul diferential este cel mai utilizat subcircuit din circuitele integrate analogice. Schema clasica a unui etaj de amplificare diferential este reprezentat in Fig. 4.b

Aceasta schema prezinta o intrare diferentiala intre bazele celor doua tranzistoare iar rezistenta de sarcina e conectata intre cei doi colectori, desi iesirea se face tot diferential. Pentru un etaj perfect simetric variatiile tensiunilor bipolare de alimentare, ale temperaturii si ale semnalelor comune aplicate pe cele doua intrari modifica in mod identic tensiunile Uc1 ,Uc2 din colectorii lui T1 si T2 si deci nu afecteaza tensiunea de iesire diferentiala URs=Uc1-Uc2. Pentru ca etajul diferential sa lucreze liniar si pentru valori mari ale partilor de semnal comune celor doua intrari se impune ca rezistenta comuna de emitator RE sa aiba valori mari. Acest deziderat se poate realiza inlocuind rezistenta RE cu o sursa de curent dupa cum s-a aratat in Fig. 5a.

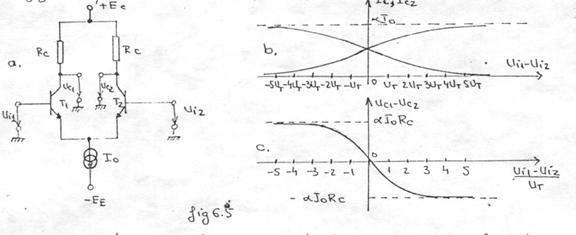

Folosind schema din Fig. 5 a se poate determina caracteristica statica de transfer a etajului diferential.

Notand cu I0 curentul debitat de sursa, considerand rezistenta echivalenta interna de valoare infinita si neglijand curentii reziduali din colector rezulta:

I0 = IE1 + IE2 IC1 a + IC2/a (IC1+IC2) /a (1)

unde s-a considerat ca tranzistoarele T1 si T2 sunt identice si deci au acelasi factor de amplificare in curent a a a

Curentii de colector depind de tensiunile baza - emitator ale tranzistoarelor T1 si T2 conform relatiilor aproximative :

IC1 IS eUbe1/Ur ; IC2 IS eUbe2/Ut (2)

unde Ut=kT/q este tensiunea termica avand la temperatura de 300 K valoarea de aproximativ 25 mV iar curentii de saturatie ai celor doi tranzistori s-au considerat a fi identici IS1=IS2=IS.

Inlocuind (2) in (1) se obtine:

I0 = IS /a ( eUbe1/Ut + eUbe2/Ut )

de unde dand factor comun fortat pe eUbe1/Ut si respective eUbe2/Ut rezulta :

I0 = IC1/a (1+e(Ube2-Ube1)/Ut ); I0 = IC2 /a (1+e(Ube1 - Ube2)/Ut ) (3)

Din legea a doua a lui Kirchhoff scrisa pe bucla masa - baza T1 - emitator T1 - emitator T2 - baza T2 - masa se obtine :

Ube1 - Ube2 = UI1 - UI2

Folosind egalitatea de mai sus in ( 3 ) se deduc expresiile curentilor de colector ai celor doua tranzistoare :

;

; (4)

(4)

Caracteristicile de transfer tensiune-curent (4) sunt reprezentate grafic in Fig. 5b Tensiunile de colector ale tranzistoarelor T1 si T2 sunt date de relatiile :

UC1 = EC - IC1 RC; UC2 = EC - IC2 RC (5)

Tinand seama de (4) din expresiile de mai sus se obtine tensiunea de iesire diferentiala :

UC1-UC2=aIo RCth![]() (6)

(6)

Caracteristica de transfer tensiune-tensiune (6) este reprezentata grafic in Fig. 5.c pentru tensiunea de intrare normala cu UT .

Asa cum se observa din Fig. 5.c caracteristica statica de transfer in tensiune a etajului diferential e liniara atunci cand tensiunea de intrare varf la varf este cel mult 2UT 50mV. Pentru o tensiune diferentiala de intrare nula , tensiune diferentiala de iesire este tot nula ceea ce permite cuplarea directa in cascada a etajelor diferentiale. Pentru tensiuni de intrare varf la varf mai mari decat 4UT 100mV , asa cum se observa din Fig.5.c, curentii de colector devin independenti de intrare si intre +EC si -EE curentul trece practic printr-un singur tranzistor.

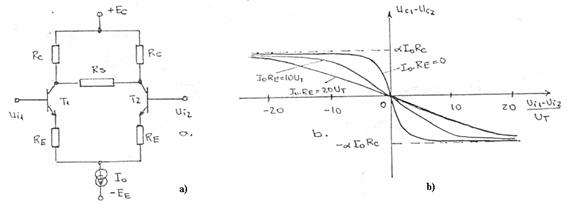

Extinderea domeniului tensiunilor pentru care etajul se comporta liniar se realizeaza prin introducerea unor rezistente numite de degenerare in emitatoarele celor doua tranzistoare (Fig. a).

Fig. 6

Asa cum indica caracteristicile de transfer din Fig. 6 b, extremele domeniului tensiunilor de intrare pentru care etajul se comporta liniar devin aproximativ Io RE , in schimb se reduce amplificarea in tensiune a etajului. In cazul in care sarcina nu se concentreaza intre colectoarele tranzistoarelor T1 si T2 ci intre unul dintre colectoare si masa (Fig.7.a) se obtine un etaj cu intrare diferentiala si iesire asimetrica. Intrarea corespunzatoare bazei lui T1 se numeste neinversoare ( semnalul de iesire e in faza cu semnalul aplicat pe aceasta intrare ). Reprezentarea simbolica a unui amplificator operational este cea din Fig. 7.b unde cu E s-a notat tensiunea bipolara de alimentare iar cu Uo tensiunea de iesire.

Pentru a caracteriza functionarea dinamica a amplificatoarelor operationale este util sa se defineasca doua categorii de semnale : de mod comun si de mod diferential.

Tensiunea de intrare in mod diferential este :

Uid = Ui1 - Ui2 (7)

Iar tensiunea de intrare in mod comun este data de relatia :

Uimc = ![]() (8)

(8)

In cazul unei tensiuni de intrare pur diferentiale, tensiunile la cele doua intrari sunt egale ca modul si opuse ca faza Ui1 = - Ui2 = Uid/2 iar in cazul unei tensiuni de intrare de mod comun pur tensiunile la cele doua intrari sunt egale si in modul si in faza Ui1 = Ui2 = Uimc.

In general tensiunea de intrare au o componenta diferentiala si una de mod comun a caror expresie rezulta din (7) si (8) astfel :

Ui1 = ![]() ; Ui2 = -

; Ui2 = -![]() (9)

(9)

Conform (9) in Fig. 7.c. este reprezentat amplificatorul operational cu semnele de intrare in componentele de mod diferential si componenta de mod comun.

Performantele amplificatoarelor operationale sunt apreciate in cataloage printr-o serie de parametri dintre care cei mai importanti sunt definiti in continuare .

Amplificarea diferentiala in bucla deschisa (fara reactie) este definite ca variatia tensiunilor de iesire raportata la variatia tensiunilor de intrare pur diferentiale:

A=![]() ; Uid=0 (10)

; Uid=0 (10)

Valoarea tipica a amplificarii diferentiale pentru un amplificator operational integrat este 104

Amplificarea de mod comun in bucla deschisa este raportul dintre variatia semnalului de iesire si variatia semnalului de intrare in mod comun pur:

Amc=![]() ;Uid=0 (11)

;Uid=0 (11)

Factorul de rejectie de mod comun CMMR (Common Mode Rejection Ratio) se defineste ca fiind raportul dintre amplificarea diferentiala in bucla descrisa si amplificarea de mod comun :

CMMR=![]() ; CMMR= 20log

; CMMR= 20log![]() [dB] (12)

[dB] (12)

Factorul de rejectie de mod comun are valori tipice cuprinse intre 70 si 80 dB. Relatiile (10) si (11) permit exprimarea tensiunii de iesire functie de componentele diferentiale si respectiv de mod comun ale tensiunii de intrare :

U0 = AUid

+ Amc Uimc = A(Ui1-Ui2)

+ Amc![]()

Curentul de polarizare la intrare este valoarea medie a celor doi curenti de intrare IB1 si IB2 (Fig.7.a) atunci cand tensiunea de iesire este nula :

IB=![]() ;U0=0 (13)

;U0=0 (13)

Valoarea tipica a curentul de polarizare este cuprinsa intre 10 si 100 mA.

Impedanta de intrare diferentiala Zid este raportul dintre tensiunea de intrare pur diferentiala si curentul diferential de intrare :

Zid=![]() ;Uim=0 (14)

;Uim=0 (14)

Deoarece la frecventele de lucru capacitatea de intrare in mod diferential este neglijabila, in cataloage se indica rezistenta de intrare cu valori tipice de sute de KW la zeci de MW

Impedanta de intrare de mod comun Zinc este definita ca fiind raportul dintre variatia tensiunii de intrare si variatia curentului de intrare, masurata pe fiecare intrare/separat fata de masa, cu conditia ca cealalta intrare sa fie conectata la masa din punct de vedere alternativ.

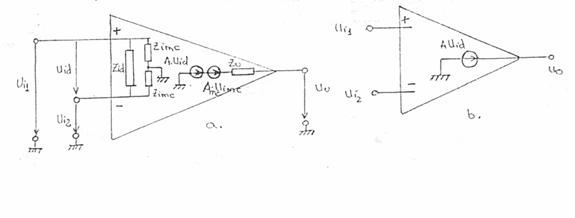

Schema echivalenta a impedantei de intrare din punct de vedere al semnalului, pentru un amplificator operational este redata in Fig.7.d

Datorita neimperecherii perfecte a componentelor din etajele amplificatoarelor operationale tensiunea la iesirea acestora este diferita de zero atunci cand ambele intrari sunt scurtcircuitate la masa. Tensiunea de decalaj ( offset )la intrare Ui0 reprezinta tensiunea ce trebuie aplicata pe una din intrari cand cealalta intrare este conectata la masa pentru a aduce tensiunea de iesire la 0 ( Fig. 7.e ). Valoarea tipica a tensiunii de decalaj la intrare e cuprinsa intre 0,5 si 10 mV. Impedanta de iesire Z0este raportul dintre variatia tensiunii de iesire cu valori tipice intre 10 si 1000 W

Viteza de variatie a semnalului de iesire SR ( slow rate ), reprezinta variatia tensiunii de iesire a unui amplificator operational in bucla inchisa raportata la durata in care s-a produs, atunci cand la intrare se aplica un semnal treapta unitate. In cataloage viteza de variatie a semnalului de iesire se indica pentru o valoare specificata a amplificarii in tensiune cu reactie si are valori tipice intre 0,1 si 1000 V/ms.

Banda in bucla deschisa , determinata prin frecventa maxima a sa, fa , se defineste ca fiind de gama de frecventa in interiorul careia amplificarea se reduce cu 3dB fata de amplificarea maxima , sau altfel spus amplificarea nu scade sub 0,707 din amplificarea la joasa frecventa.

Frecventa de taiere fT este frecventa la care amplificarea in bucla deschisa devine unitara ( DdB ).

Schema echivalenta simplificata a amplificatorului operational, in care se tine seama de o parte din parametrii definiti anterior, este reprezentata in Fig.8.a.

Amplificatorul operational ideal a carui schema echivalenta este reprezentata in Fig.8.b este caracterizat de urmatorii parametrii: amplificarea in bucla deschisa foarte mare, rezistenta de intrare infinita, rezistenta de iesire nula, tensiunea de decalaj la intrare nula si banda in bucla deschisa infinita.

Fig. 8

Aplicatii ale amplificatoarelor operationale

In practica amplificatoarele operationale se folosesc in circuite cu reactie, care permit prelucrarea semnalelor de intrare dupa o anumita relatie matematica. Pentru simplificare , deducerea reactiei intre semnalul de iesire si cel de intrare pentru circuitele elementare cu amplificatoare operationale, se face considerand ca acestea din urma sunt ideale, deci admit o schema echivalenta cu cea din Fig.8.b.

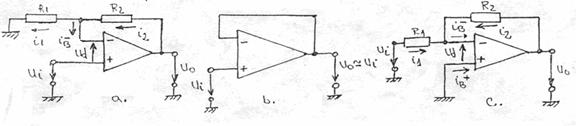

Amplificatorul operational in montaj de amplificator neinversor este reprezentat in Fig.9.a.

Tensiunea la iesirea amplificatorului operational este :

u0 = A Ud

unde pentru simplificare in notatia folosita pentru tensiunea diferentiala de intrare s-a omis indicele i.

Aplicand teorema a doua a lui Kirchhoff pe ochiul de intrare rezulta:

Ud = Ui - UR1

Deoarece rezistenta de intrare diferentiala Rid este foarte mare, curentul la intrarea inversoare iB 0 si deci i1 = i2. Aplicand teorema a doua a lui Kirchhoff pe ochiul de iesire se obtine :

![]() i1 =

i1 = ![]()

si deci : UR1 = ![]()

In final rezulta :

U0 = A ( Ui - ![]()

Explicitand raportul U0/Ui din relatia de mai sus se obtine amplificarea cu reactie :

AR= (15)

(15)

Comparand ( 15 ) cu relatia ( 2.69 ) ce exprima amplificarea unui amplificator cu reactie se obtine factorul de reactie :

b = ![]()

corespunzator divizorului rezistiv format din R1 si R2 .

Deoarece amplificarea in bucla deschisa A este foarte mare din (15) se poate exprima amplificarea amplificatorului neinversor prin :

AR 1+![]() (16)

(16)

Din (16) rezulta ca pentru amplificatorul neinversor semnalul de iesire este in faza cu semnalul de intrare iar amplificarea depinde exclusiv de circuitul de reactie format din R1 si R2 .

Un caz particular de amplificator neinversor este repetorul de tensiune ( Fig.9.b) caracterizat printr-o reactie negativa totala (R2=0 si R1=F). Pentru aceste valori ale lui R1 si R2 din (16) rezulta AR 1 si U0 Ui deci tensiunea de iesire o repeta pe cea de intrare.

Fig. 9

Amplificatorul operational in montaj de amplificator inversor este reprezentat in Fig.9.c. Aplicand teorema a doua a lui Kirchhoff pe ochiurile de intrare si respective de iesire rezulta :

Ui=i1R1-Ud;U0=i2R2-Ud .

Dar Ud = U0/A si pentru A foarte mare Ud 0 si din relatiile de mai sus se obtine:

![]() ;

;![]() ; (17)

; (17)

Deoarece curentul la intrarea inversoare este neglijabil :

I1 +i2 = iB

Inlocuind (17) in relatia de mai sus si explicitand raportul u0/ui rezulta :

![]() (18)

(18)

Din (18) rezulta ca semnalul de iesire al amplificatorului inversor este in antifaza cu semnalul de intrare iar amplificarea este data de raportul rezistentelor din circuitul de reactie.

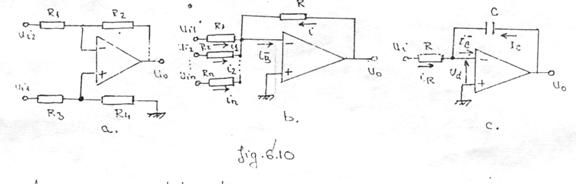

In Fig. 10 a. este reprezentata schema unui amplificator cu intrare diferentiala realizat cu amplificator operational.Aplicand principiul superpozitiei si folosind (16) si (18) rezulta :

(19)

(19)

Deoarece curentul iB+ la intrarea neinversoare este neglijabil, R3 si R4 formeaza un divizor de tensiune ideal deci :

![]()

Inlocuind relatia de mai sus in (19) se obtine :

![]()

Daca in relatia de mai sus se egaleaza coeficientii lui Ui1 si Ui2 rezulta R2/R1=R4/R3 si in acest caz :

![]() (20)

(20)

O aplicatie interesanta a amplificatorului operational o constituie sumatorul cu coeficienti ponderati (Fig. 10.b).

Aplicand teorema intai a lui Kirchhoff pentru nodul de la intrarea inversoare rezulta :

I1 + i2 + . + in + I = iB

Generalizand (17) se poate scrie :

![]() ;

; ![]() . . ..

. . .. ![]() ,

, ![]()

si in final se obtine :

(21)

(21)

Daca in (21), R1 = R2 = . = Rn = R , tensiunea de iesire este chiar suma cu semn schimbat a tensiunilor de intrare :

U0 = - (ui1 + ui2 + . + uin )

Iar daca R1 = R2 = . = Rn = nR circuitul sumator determina valoarea medie cu semn schimbat a tensiunilor de intrare :

![]()

In Fig. 10 c este reprezentat un circuit de integrare cu amplificator operational.

Asa cum s-a aratat anterior :

![]()

si deoarece U0 = Uc +Ud Uc se poate scrie :

![]() (22)

(22)

rezulta :

![]()

In final se obtine relatia dintre tensiunea de iesire si cea de intrare :

![]() (23)

(23)

Amplificatorul operational in montaj de circuit de derivare este reprezentat in Fig. 11.a. Curentii prin rezistenta si respective condensator sunt:

![]() ;

; ![]()

si tinand seama de (22) se obtine :

![]()

de unde in final rezulta relatia dintre tensiunea de iesire si tensiunea de intrare :

![]() (24)

(24)

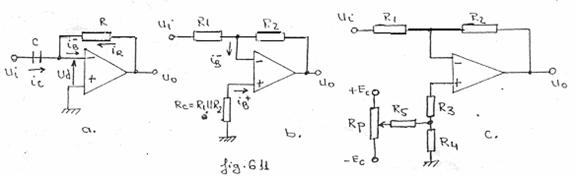

Diferenta iB+-iB- a curentilor de intrare ( de polarizare ) ai amplificatorului inversor din Fig.9.c. determina aparitia la iesire a unei tensiuni de decalaj ce se suprapune peste aceea datorata asimetriilor interne. Deoarece curentul de intrare al bornei inversoare parcurge rezistentele R1 si R2 influenta curentilor de polarizare se poate minimiza prin conectarea unei rezistente de colectie Rc=R1/R2 asa cum se indica in Fig.11.b.

O posibilitate de a compensa simultan pentru un amplificator inversor atat influenta curentilor de polarizare cat si tensiunea de decalaj la intrare(Fig.7.e) este data de schema din Fig.11.

Influenta curentilor

de polarizare se minimizeaza prin alegerea rezistentelor R![]() si R

si R![]() astfel incit :

astfel incit :

Compensarea tensiunii de

decalaj la intrare u![]() se face de la o sursa externa de compensare E

se face de la o sursa externa de compensare E![]() prin intermediul pontentiometrului. Rezistenta R

prin intermediul pontentiometrului. Rezistenta R![]() se alege astfel incit sa indeplineasca conditia :

se alege astfel incit sa indeplineasca conditia :

R5>>R3+R4

pentru ca i![]() sa simta spre masa doar rezistenta

data de (25). Valoarea rezistentei potentiometrului Rp se alege

astfel incat curentul ce o strabate sa fie cu un ordin de marime

mai mare decat curentul de polarizare i

sa simta spre masa doar rezistenta

data de (25). Valoarea rezistentei potentiometrului Rp se alege

astfel incat curentul ce o strabate sa fie cu un ordin de marime

mai mare decat curentul de polarizare i![]() al intrarii neinversoare.

al intrarii neinversoare.

4. Comparatoare si stabilizatoare

Comparatoarele sunt circuite care semnalizeaza prin marimea de iesire daca una dintre marimile de intrare este mai mare sau mai mica decat marimea cealalta de intrare, considerata de referinta. Marimea de iesire poate lua deci doar doua valori care pot fi puse in corespondenta cu nivelele logice 1L si 0L proprii circuitelor integrate numerice.

Din punct de vedere constructiv si functional comparatoarele se aseamana cu amplificatoarele operationale astfel incat in aplicatiile nepretentioase un amplificator operational poate fi folosit drept comparator si reciproc. Totusi in comparatie cu amplificatoarele operationale, comparatoarele prezinta unele particularitati:

- nivelul marimilor de iesire (curent sau tensiune) este compatibil cu circuitele logice pe care le comanda;

- functionarea in bucla deschisa (fara reactie): lipsa reactiei asigura pentru comparatoare o banda larga si deci o caracteristica de transfer mai abrupta fata de amplificatoarele operationale;

- posibilitatea autorizarii functionarii (inhibarii semnalului de iesire) printr-o comanda exterioara (strobe).

Schema simbolica a unui comparator este asemanatoare cu cea a unui amplificator operational si se prezinta in Fig.12.a. Performantele comparatoarelor se apreciaza in cataloage printr-o serie de parametrii dintre care cei mai importanti sunt definiti in continuare.

Rezolutia UR reprezinta tensiunea de intrare diferentiala minima necesara pentru a determina o decizie logica la iesire. Rezulta ca acest parametru se defineste functie de caracteristica de transfer a familiei de circuite logice comandate de iesirea comparatorului. Pentru un circuit TTL aceasta caracteristica de transfer este reprezentata in Fig.12.b. valoarea tensiunii dispuse la mijlocul intervalului dintre nivelul logic 0L se numeste tensiune de prag UP.

Pentru familia TTL tensiunea de prag este de 1,4V. Este logic ca atunci cand tensiunea diferentiala la intrarea comparatorului este nula iesirea sa fie egala cu tensiunea de prag. Relatia de definitie a rezolutiei este deci:

UR=![]() (26)

(26)

unde A este amplificarea in bucla deschisa a comparatorului.

a)

b)

Tensiunea de decalaj UID este tensiunea care trebuie aplicata la intrare pentru ca iesirea sa fie egala cu tensiunea de prag a circuitului logic comandat. In Fig.12 c cu linie punctata se reprezinta caracteristica de transfer a unui comparator real a carui tensiune de iesire este UP pentru tensiunea diferentiala de intrare egala cu -UID si nu pentru -Uid=0. Tensiunea maxima de intrare in mod diferential UidM este valoarea maxima a tensiunii diferentiale care nu distruge circuitul de intrare al comparatorului.

Timpul de raspuns tR este intervalul de timp scurs intre aplicarea unui semnal treapta de tensiune la intrare si momentul in care tensiunea de iesire atinge valoarea de prag a circuitului logic comandat.

Doua dintre comparatoarele integrate larg folosite sunt LM339 (βM339) si μA711 (CLB2711), in paranteze fiind notate codurile producatorilor interni. Circuitul βM339 contine patru comparatoare independente (Fig.13.a) proiectate special pentru a avea o rezolutie TTL foarte buna (UR=50μV) dar un timp de raspuns relativ mare (tr=1,3μs).

Alimentarea se face de la o singura

sursa de tensiune intre 2 si 36V sau de la doua surse simetrice

in gama de ![]() 1 la

1 la ![]() 18V iar tensiunea de decalaj UID=5mV. O

aplicatie tipica pentru care se foloseste un singur comparator

din circuitul βM339 este ilustrata in Fig.13.b. Aceasta schema

permite compararea unui semnal de intrare valabil in timp cu o tensiune de

referinta fixa, obtinuta printr-un divizor chiar de la

tensiunea de alimentare (Fig.13.c.).

18V iar tensiunea de decalaj UID=5mV. O

aplicatie tipica pentru care se foloseste un singur comparator

din circuitul βM339 este ilustrata in Fig.13.b. Aceasta schema

permite compararea unui semnal de intrare valabil in timp cu o tensiune de

referinta fixa, obtinuta printr-un divizor chiar de la

tensiunea de alimentare (Fig.13.c.).

Tensiunea de iesire a comparatorului este data de relatia:

![]()

UOM daca Ui < Uref

U0

= cu ![]()

Uom daca Ui > Uref

Adica asa cum rezulta din caracteristica de transfer din Fig.(12), iesirea este maxima UOM cand tensiunea de intrare diferentiala Uid=Uref-Ui este pozitiva si minima UOm cand Uid este negativa.

Circuitul CLB 2711 contine doua comparatoare Fig.14.a. proiectate in vederea minimizarii timpului de raspuns (tr=40ns0 cu pretul reducerii rezolutiei TTL (UR=2mV).

Alimentarea se face de la doua surse

asimetrice +12V si -6V; tensiunea diferentiala de intrare

maxima UidM=![]() 5V iar tensiunea de decalaj este UID=3,5mV. Cele

doua comparatoare sunt conectate prin intermediul a doua porti

ce realizeaza functia logica SI, la o poarta SAU a

carei iesire reprezinta iesirea comparatorului dublu CLB

2711.

5V iar tensiunea de decalaj este UID=3,5mV. Cele

doua comparatoare sunt conectate prin intermediul a doua porti

ce realizeaza functia logica SI, la o poarta SAU a

carei iesire reprezinta iesirea comparatorului dublu CLB

2711.

Intrarile de esantionare (strobare) 1 si 2 actioneaza asupra circuitului astfel:

- daca ambele intrari de esantionare sunt in 0L (practic la masa), iesirea circuitului este in 0L;

- daca o singura intrare de esantionare este in 1L (practic Uesantionare>3V); iesirea circuitului coincide cu iesirea comparatorului corespunzator;

- daca ambele intrari de esantionare sunt in 1L iesirea circuitului poate fi 1L sau 0L functie de semnalele de intrare ui1 si ui2 raportate la marimile de referinta Uref1 si Uref2 ale celor doua comparatoare.

O aplicatie tipica a circuitului CLB 2711 este comparatorul cu fereastra (Fig.14.b.) denumit si discriminator de interval si care semnalizeaza prin tensiunea de iesire Uom daca tensiunea de intrare se gaseste intre doua valori pre4stabilite UrefM si Urefm (Fig.14.c).

a)

b)

c)

Fig.13

a)

b)

b)

c)

Fig.14

O alta categorie de circuite integrate liniare larg folosite in practica este cea a stabilizatoarelor electronice. In Fig.15.a. se indica schema bloc a stabilizatorului de tensiune integrat ROB 723 ce contine:

- etajul de formare a tensiunii de referinta de 7,15V format dintr-o dioda Zenner, o sursa de curent constant de polarizare a diodei Zenner si amplificatorul de referinta; tensiunea de referinta e disponibila utilizatorului si poate fi micsorata cu ajutorul unui divizor rezistiv exterior;

- amplificatorul de eroare cu intrare diferentiala si iesire asimetrica cu amplificare in bucla deschisa de 60dB;

- tranzistor regulator seria TS avand un curent maxim de 150mA; in colectorul sau se aplica tensiunea de alimentare, iar din emitor se culege tensiunea stabilizata. Dioda Zenner din emitorul lui TS furnizeaza la terminalul UZ un nivel de tensiune translatat cu 6,2V fata de tensiunea de iesire U0;

- tranzistorul de protectie TP; acesta se deschide atunci cand curentul de iesire al stabilizatorului ce strabate rezistenta conectata extern intre bornele CL (curent limit) si CS (curent sense), depaseste o valoare prestabilita; deschiderea lui TP determina scaderea curentului in baza lui TS si deci limitarea curentului sau de colector; intre terminalul COMP din colectorul lui TP si intrarea inversoare a amplificatorului de eroare se conecteaza un condensator exterior cu valoarea tipica de 100pF pentru compensare in frecventa.

Principalele caracteristici electrice ale stabilizatorului ROB 723 sunt urmatoarele:

- tensiunea de alimentare maxima intre +E si -E este 40V;

- domeniul tensiunii de iesire este de la 2 la 37V;

- stabilizarea in sarcina este 0,1%U0;

- tensiunea de referinta Uref=7,15V;

- curentul de iesire fara tranzistor serie extern 150mA; pentru curenti de iesire mai mari se poate conecta un tranzistor serie extern de putere comandat de obicei prin intermediul terminalului UZ (Fig.15.a.).

O schema tipica de aplicatie a

circuitului ROB 723 (Fig.15.b.) este cea de stabilizator de tensiune

pozitiva scazuta (U0=2![]() 7V).

7V).

a)

b)

Fig.15

Asa cum se observa din Fig.15.b., tensiunea de referinta Uref=7,15V se aplica la intrarea neinversoare a amplificatorului de eroare prin intermediul divizorului format din R1 si R2. tensiunea de iesire a stabilizatorului va fi in acest caz:

U0=![]()

Rezistenta de scurtcircuit RSC se conecteaza intre baza si emitorul tranzistorului de protectie TP si se determina din relatia:

IOM=![]()

unde IOM este curentul maxim admis la iesire, iar UBE=0,6V este tensiunea de deschidere a tranzistorului de protectie.

Rezistenta dintre emitorul lui TP si intrarea inversoare a amplificatorului de eroare se alege de valoare R3=R1llR2 pentru a reduce influenta curentilor de polarizare (Fig.11.b).

5. Circuite logice bipolare

Un loc aparte in cadrul circuitelor logice realizate in tehnologie bipolara il ocupa familia circuitelor TTL (Tranzistor-Tranzistor-Logic; logica tranzistor-tranzistor).

Poarta fundamentala cu ajutorul careia se poate genera orice functie logica este in aceasta familie poarta SI-NU, poarta fiind deci un circuit care implementeaza o anumita functie logica.

Definitorii pentru fiecare familie de circuite logice sunt nivelele logice adoptate pentru 0L si 1L si tipul de logica (pozitiva sau negativa) adoptate.

Familia TTL foloseste logica pozitiva iar nivelele logice sunt ilustrate in Fig.1a., indicii folositi avand urmatoarea semnificatie: I (imput-intrare), 0 (output-iesire), L (low-jos, corespunde lui 0L in logica pozitiva), H (high-inalt, corespunde lui 1L in logica pozitiva).

Pentru circuitul de comanda se indica tensiunile de iesire maxima garantata in stare jos UOLmax si respectiv minima garantata in stare sus UOHmin iar pentru circuitul comandat tensiunile de intrare maxima permisa in stare jos UILmax si respectiv minima permisa in stare sus UIHmin. Tensiunea de alimentare nominala a circuitelor TTL este UCC=5V. Se asigura deci compatibilitatea intre circuite in sensul ca o tensiune de iesire a portii de comanda este recunoscuta cu o margine de zgomot de 0,4V de poarta comandata. In Fig.1b. sunt reprezentate simbolul si respectiv tabelul de adevar al portii SI-NU iar in Fig.1c. se reda schema bloc si conFiguratia terminalelor circuitului TTL tip CDB 400 ce contine patru porti SI-NU cu doua intrari.

a)

|

A |

B |

A*B |

A*B |

b)

c)

Fig.16

In Figura 17 a. este reprezentata schema electrica a portii TTL SI-NU cu doua intrari, iar in Fig.17.b. caracteristica de transfer a acesteia, precum si un tabel ce indica starea in care se afla cele patru tranzistoare din compunerea portii in diverse puncte ale caracteristicii.

a)

|

T1 |

T2 |

T3 |

T4 |

|

|

AB |

s |

b |

b |

s |

|

BC |

s |

c |

b-c |

c |

|

CD |

c |

c |

c |

c-b |

|

DE |

ci |

c |

s |

b |

b)

FIGURA 17

Schema portii TTL cuprinde urmatoarele elemente de circuit active:

- tranzistorul multiemitor T1, care realizeaza practic functia SI;

- tranzistorul de comanda T2;

- tranzistoarele T3 si T4 comandate in contratimp de T2;

- diodele D1 si D2 de limitare a salturilor negative ce apar datorita reflexiilor de neadaptare pe liniile de transmisie;

- dioda D3 destinata sa impiedice intrarea in conductie a lui T4 cand T3 este saturat.

Pentru a arata ca circuitul din Fig.17.a. implementeaza functia SI-NU se analizeaza functionarea acesteia in doua situatii: ambele intrari au un potential de 2V (valoarea minima admisibila la intrare pentru 1L), cand iesirea trebuie sa fie 0L (potentialul maxim de 0,4V) si respectiv cel putin una din intrari are un potential de 0,8V (valoarea maxima admisa la intrare pentru 0L), cand iesirea trebuie sa fie in 1L (potential minim 2V). Cand ambele intrari A si B sunt la 2V (1L) functionarea este urmatoarea:

- tranzistorul T1 se gaseste in conductie inversa; de la UCC=5V prin R1 se asigura in baza lui T1 o tensiune de 2V si deci ambele jonctiuni emitor-baza ale lui T1 sunt polarizate invers; de la UCC prin R2 se asigura in colectorul lui T1 o tensiune de 1,4V si deci jonctiunea baza-colector a lui T1 este polarizata direct; ambele intrari ale circuitului absorb un curent IIH de la iesirile circuitelor de comanda;

- tranzistorul T2 conduce datorita curentului injectat in baza sa de T1 , asigurand prin curentul de emitor o tensiune de 0,7V pe R4 si o tensiune redusa in colector;

- tranzistorul T3 este in conductie datorita potentialului de 0,7V din baza sa; tensiunea lui in colector este maxim 0,4V (0L); iesirea circuitului absoarbe un curent IOL de la intrarea circuitului comandat;

- tranzistorul T4 e blocat deoarece tensiunea din colectorul lui T2 nu este suficienta pentru a deschide si jonctiunea baza-emitor a lui T2 si dioda D3.

Functionarea portii este aceeasi si atunci cand ambele intrari A si B sunt in gol (neconectate). In acest caz jonctiunea E-B a lui T1 este blocata in schimb jonctiunea B-C e deschisa si curentul injectat in baza lui T2 il deschide pe acesta. O intrare in gol se comporta deci ca si cand ar fi conectata la nivelul 1L.

Daca cel putin una din intrari, de exemplu A din Fig.17.a. este la 0,8V (0L) functionarea este urmatoarea:

- tranzistorul T1 intra in conductie directa; jonctiunea emitor-baza a lui T1 este polarizata direct cu 0,8V in emitor si 2,1V in baza; dupa intrarea in conductie a lui T1 potentialul in baza va scade la 0,9V datorita caderii de tensiune pe jonctiunea emitor-baza aflata in conductie;

- tranzistorul T2 se blocheaza deoarece tensiunea in colectorul lui T1 scade la 0,4V;

- tranzistorul T3 se blocheaza deoarece curentul de emitor a lui T2 este neglijabil si caderea de tensiune pe R4 este practic nula; tensiunea lui in colector este de cel putin 2,4V (1L);

- tranzistorul T4 conduce deoarece potentialul de 4,7V din colectorul lui T2 deschide atat jonctiunea baza-emitor a lui T4 cat si dioda D3; iesirea circuitului debiteaza un curent IOH egal cu curentul de emitor al lui T4 in stare de conductie.

Caracteristica de transfer din Fig.17 b. este obtinuta in conditiile in care una din intrarile portii este in 1L, iar la a doua intrare se aplica o tensiune crescatoare de la 0V. Pentru Ui<0,6V (portiunea AB a caracteristicii) starea celor patru tranzistoare din schema e indicata de linia AB a tabelului si anume T1 si T4 in saturatie iar T2 si T3 blocate, tensiunea de iesire fiind mare. Cand 0,6<ui<1,2V (portiunea BC a caracteristicii) T2 incepe sa conduca, T4 iese din saturatie dar ramane in conductie iar T3 incepe sa iasa din blocare, ceea ce determina scaderea lenta a tensiunii U0 la iesirea portii. Pentru 1,2<ui<2V (portiunea CD a caracteristicii de transfer) T1 si T2 se mentin in conductie, T4 trece din conductie in blocare iar T3 aflat in stare de conductie puternica determina o scadere abrupta a tensiunii de iesire. Pentru ui>2V ambele intrari sunt in 1L, T4 se blocheaza iar T3 aflat in saturatie impune o tensiune de iesire constanta la nivel mic (portiunea DE a caracteristicii). Performantele circuitelor logice sunt apreciate printr-o serie de parametrii dintre care cei mai importanti se prezinta in continuare.

Un parametru ce caracterizeaza imunitatea la perturbatii a circuitului logic este marginea de zgomot, definita prin diferenta dintre valorile tensiunilor admise la intrare si tensiunile garantate la iesire pentru cele doua stari logice. Asa cum rezulta din Fig.16 a. marginile de zgomot ale circuitelor TTL sunt:

MZL=UILmax-UOLmax=0,8-0,4=0,4V

MZH=UIhmin-UOHmin=2-2,4=-0,4V (27)

In concluzie pentru circuitele TTL marginea de zgomot in curent continuu este de 0,4V pentru ambele nivele logice.

Consumul de curent al unei porti la intrare se numeste unitate de sarcina. Pentru poarta TTL SI-NU curentul de intrare maxim debitat in starea jos, corespunzator conductiei directe a lui T1 din Fig.17.a. este IIL=1,6mA, iar curantul de intrare maxim absorbit in stare sus cu T1 in conductie inversa este IIhmax = 40 μA. Stabilirea unor reguli de interconectare a circuitelor logice impune cunoasterea curentilor de iesire minimi ai portii TTL pentru cele doua nivele logice si anume curentul IOlmin=0,8mA debitat in stare sus de tranzistorul T4.

Capacitatea maxima de incarcare a iesirii (FAN-OUT), reprezinta numarul N maxim de intrari care pot fi comandate simultan de iesirea unei porti. Tinand seama de valorile curentilor de iesire si de intrare prezentate anterior se obtine:

NL=![]() ; NH=

; NH=![]()

Nivelul 0L fiind limitativ rezulta ca fan-out-ul garantat al familiei TTL este 10. Performantele dinamice ale circuitelor logice sunt apreciate prin intermediul timpilor de comutare si propagare definiti in Fig.18 a. Prin convectie, timpii de tranzitie (comutare) din starea jos in starea sus (timpul de crestere) si respectiv din starea sus in starea jos (timpul de cadere) se definesc intre 0,1 si 0,9 din amplitudinea maxima UM si pentru familia TTL au valori tipice tTLH=8ns si tTHL=5ns. Timpii de propagare se definesc ca fiind intervalul dintre nivelele de 1,5V ale semnalului de intrare si de iesire. Pentru poarta TTL valoarea tipica a timpului de propagare la tranzitia sus-jos a semnalului de iesire este tpHL=8ns, iar pentru tranzitia jos-sus la iesire valoarea tipica este tpLH=18ns. Timpul de propagare al semnalului prin poarta este un indicator sintetic al vitezei de comutare a acesteia si se defineste prin relatia:

tp=![]()

Pentru familia TTL timpul de propagare are valoarea tipica tp=10ns. Cresterea sarcinii capacitive a portii duce la marirea timpului de propagare. Un alt parametru important al unei familii logice este puterea consumata pe poarta.

Initial se determina pentru circuitul CDB 400 din Fig.16 c. curentul consumat de la sursa UCC de intregul circuit atunci cand cele patru porti sunt in 0L si anume ICCL=12mA si respectiv in 1L si anume ICCH=4mA. Consumul de curent mai mare cu iesirea in 0L fata de cazul cand aceasta este in 1L; se datoreaza in principal conductiei in primul caz si blocarii in al doilea caz al tranzistorului T2 dinFig.17.a. Consumul circuitului de defineste atunci cand la intrare se aplica impulsuri dreptunghiulare cu factor de umplere de 50%. Rezulta deci consumul de curent ICC=(ICCH+ICCL)/2=8mA si la UCC=5V se obtine puterea disipata de circuitul CDB 400 egala cu 40mW.

Rezulta deci pentru familia TTL o putere disipata pe poarta de 10mW. In catalog pentru familia TTL comerciala se mai specifica valorile extreme permise pentru tensiunea de alimentare si anume 4,75 si 5,25V si gama temperaturilor de lucru cuprinsa intre 0 si 700C.

Pentru obtinerea unor timpi de propagare mai buni si a unei imunitati la zgomote crescute se recomanda ca intrarile portilor TTL neutilizate sa se conecteze la o tensiune pozitiva corespunzatoare nivelului 1L. O modalitate de realizare practica a acestei recomandari o constituie conectarea intrarilor nefolosite la UCC printr-o rezistenta de 1kΩ. La fiecare rezistor pot fi conectate 25 de intrari nefolosite.

Doua sau mai multe porti SI-NU standard nu pot avea iesirile conectate in paralel. Daca se considera doua porti cu iesirile in paralel functionarea este corecta daca ambele iesire sunt in 0L sau in 1L, in schimb daca una din iesiri este in 1L iar cealalta in 0L este practic pus la masa tranzistorul T3 al celeilalte porti. Aceasta determina ambalarea termica a celor doua tranzistoare, deoarece curentul este eliminat doar de rezistenta R3 de valoare mica (130Ω).

O solutie posibila este eliminarea din schema portii TTL (Fig.17 a.) a tranzistorului T4, diodei D3 si rezistentei R3 obtinandu-se astfel asa numita poarta cu colectorul in gol. In acest caz tranzistorul T3 nu mai are nici o sarcina interna si devine posibila conectarea colectorului tranzistoarelor de tip T3 din mai multe porti la o rezistenta de sarcina comuna RS legata la UCC (Fig.1b.). Conectarea in paralel a N porti cu colectorul in gol realizeaza functia logica si a iesirilor celor N porti fara a folosi nici o alta poarta logica. Intr-adevar, potentialul punctului comun al iesirilor portilor corespunde nivelului 1L doar atunci cand toate iesirile sunt in 1L; este suficient ca iesirea unei singure porti sa fie in 0L pentru ca tranzistorul T3 alo acesteia sa scurtcircuiteze la masa punctul comun al iesirilor si potentialul acestuia sa corespunda nivelului 0L. Functia logica obtinuta prin conectarea portilor cu colector in gol se numeste si cablat.

Pentru aplicatiile ce impun timpi de comutare foarte redusi s-a realizat seria TTL cu diode Schottky. La seria TTL standard timpul de propagare este de aproximativ 10ns datorita faptului ca tranzistorul comuta intre blocare si saturare asa cum se observa si in tabelul din Fig.17.b. Pentru a reduce timpii de comutare trebuie evitata intrarea in saturatie. O solutie posibila este folosirea unei diode Schottky (contact metal-semiconductor) intre colector si baza tranzistorului (Fig.18.c.). Se obtine astfel un tranzistor Schottky iar prin reactia negativa dintre iesire si intrare astfel introdusa se evita intrarea in saturatie a tranzistorului. Seria TTL cu diode Schottky permite obtinerea unui timp de propagare pe poarta de 3ns cu pretul cresterii puterii consumate pe poarta la 220mW. Pentru a permite conectarea iesirilor mai multor porti in paralel la o magistrala comuna de date s-a introdus seria TTL cu 3 stari. Circuitul de iesire in contratimp (T3 si T4) al unei porti TTL poate fi in 0L (T3 conduce si T4 e blocat) sau in 1L (T3 e blocat si T4 conduce). Circuitul TTL cu 3 stari permite blocarea simultana a tranzistoarelor T3 si T4 si realizarea unei stari de impedanta mare folosind un terminal de autorizare a functionarii (enable).

In Fig.18.d. sunt reprezentate doua simboluri pentru poarta SI-NU cu trei stari precum si tabelele de adevar corespunzatoare.

b) c) d)

|

E |

A |

B |

C |

|

X |

X |

Zmare |

FIGURA 18

Diferenta dintre cele doua reprezentari ale portii Si-NU cu trei stari este aceea ca in prima dintre ele simbolul inversorului (implementeaza functia logica NU) este complet. Din tabelul de adevar rezulta ca atunci cand terminalul de autorizare este in 0L functionare este similara celei a portii SI-NU standard, iar atunci cand acesta trece in 1L indiferent de intrarile A si B iesirea trece in stare de impedanta mare. Iesirile in doua sau mai multe porti logice cu trei stari se pot conecta in paralel cu conditia ca o singura intrare de autorizare sa fie in 0L la un moment dat.

Pentru aplicatii ce necesita o viteza de comutare foarte mare s-a realizat o familie de circuite logice bipolare numita ECL (Emitor Coupled Logic - logica cu cuplaj in emitor). Poarta de baza a acestei familii este poarta (SAU)-(SAU-NU) a carei schema electrica e reprezentata in Fig.19.a.

Scheme portii ECL cuprinde urmatoarele structuri:

un amplificator diferential ( cu cuplaj

in emitor); la intrarea corespunzatoare lui T2 se aplica o

tensiune de referinta UR iar cealalta intrare este

dubla T1 si T![]() si realizeaza practic functia SAU;

si realizeaza practic functia SAU;

sursa de tensiune de referinta UR=-1,175V formata din T3, D1, D2 si R1, R2, R3;

repetoarele pe emitor T4 si T5 se folosesc ca etaje de iesire datorita impedantelor mici de iesire si curentilor de iesire mari.

Poarta se alimenteaza de la o singura sursa negativa -UEE=-5,2V. Nivelurile logice tipice pentru familia ECL sunt UH=-0,75V si UL=-1,55V. Pentru simplificare se considera initial ca etajul diferential de intrare este format doar din T1 si T2. Asa cum se observa din Fig.5.b.

Daca la intrarea A se aplica tensiunea UA =UH =-0,75V>UR =-1,175 atunci T2 este practic blocat si tot curentul de emitor trece prin T1 iar daca UA =-1,55V<UR=-1,175V atunci T1 este blocat si tot curentul de emitor trece practic prin T2.

Prin urmare comutarea semnalului de intrare din 1L in 0L sau invers determina comutarea unui curent fix de la T1 la T2 si invers . Deoarece T1 si T2 nu lucreaza in saturatie ,timpii de comutatie se reduc considerabil . In Fig. 19b se reprezinta simbolul si respectiv tabelul de adevar al portii ECL .

Tranzistorul T2 poate conduce doar daca ambele tranzistoare T1 si T1 legate in paralel sunt blocate adica daca la ambele intrari A si B se aplica 0L . In aceasta situatie tensiunea in colectorul lui T2 este de -0,8V iar in emitorul lui T5 datorita caderii de tensiune pe jonctiunea baza - emitor a acestuia se obtine tensiunea de -0,8-0,75=-1,55V corespunzatoare nivelului 0L. Este suficient ca la o singura intrare sa se aplice 1L ,pentru ca T2 sa se blocheze , tensiunea sa in colector sa fie practic nula si in emitorul lui T5 sa se obtina 0-0,75=-0,75V adica 1. Rezulta ca intr-adevar iesirea repetitorului pe emitor T5 realizeaza functia logica SAU . Familia ECL realizeaza timpi de propagare foarte mici de la 1 la 4ns ,dezavantajul fiind puterea consumata pe poarta mai mare (aproximativ 25mW ) .

Un avantaj in plus al acestei familii il constituie existenta iesirilor complementare la care se obtin simultan functiile logice SAU si SAU-NU .Acesta se traduce printr-o reducere a numarului de circuite necesare fata de cazul cand ar fi disponibila o singura iesire .

Pentru realizarea circuitelor bipolare cu densitate de integrare mare se foloseste familia II. L notata uneori si I2 L (Integrated Injection Logic - logica integrata de injectie ). Circuitul de baza al familiei , care permite implementarea simpla a tuturor functiilor logice este inversorul . In Fig.19 c este realizata schema electrica ,simbolul si tabelul de adevar al unui inversor cu doua iesiri . Acesta se compune dintr-o sursa de curent realizata cu tranzistorul pnp T2 si un tranzistor npn multicolector T1 care realizeaza practic functia logica NU .

Daca la intrarea A se aplica o tensiune Ul <20 mV (corespunzatoare lui 0 pentru Ucc =1,5V ) de la iesirea etajului anterior , curentul tranzistorului T2 este practic scurtcircuitat la masa de tranzistorul de iesire aflat in conductie al etajului anterior , T1 este blocat si tensiunea sa de colector UH = 0,4 -0,8 (la UCC =1,5V ) corespunde nivelului 1.

Daca la intrare se aplica 1L ( tranzistorul de iesire al etajului anterior este blocat ) curentul general de T2 e injectat in baza lui T1 care se deschide si tensiunea lui de colector corespunde nivelului 0. Deoarece circuitul elementar se compune din doua tranzistoare fara nici o rezistenta , aria ocupata de acesta este foarte mica si familia I IL permite realizarea unei densitati de integrare comparabile sau superioare circuitelor MOS . Timpul de propagare depinde practic invers proportional de curentul injectat in baza lui T .Pentru un curent de injectie de 50 m A rezulta tP=32ns iar valoarea limita obtinuta pentru curenti de injectie mai mari de m200 A este 200ns . Acest timp de propagare relativ mare constituie principalul dezavantaj al familiei II L .

6 Circuite logice MOS

Circuitele logice integrate obtinute prin tehnologia MOS reprezinta o alternativa avantajoasa pentru aplicatiile ce nu necesita viteza mare si pentru care consumul de putere redus este imperios necesar .

Circuitele logice MOS se deosebesc in mod substantial de cele realizate cu tranzistoare de tip ' metal - oxid - semiconductor'.

In Fig. 20. este prezentata structura simplificata a unui tranzistor MOS cu canal n . Acesta consta din doua regiuni de tip n realizate prin difuzie intr-un substrat de siliciu de tip p . In functionare regiunea n pe care se aplica potentialul mai pozitiv se numeste drena iar cealalta regiune n se numeste canal . Grila ,numita uneori si poarta este o pelicula metalica (aluminiu ) dispusa intre drena si sursa si separata de canal printr-un strat izolator de SO de unde si denumirea de structura metal - oxid - semiconductor .Conductia prin canal este controlata de potentialul aplicat pe poarta .

Daca potentialul grila - sursa este negativ ( UGS<0),la suprafata substratului intre sursa si drena se acumuleaza purtatori majoritari q iar electronii sant indepartati. Daca se aplica in acest caz o diferenta de potential intre drena si sursa cu plusul pe drena nu se va inchide nici un curent intre acesti doi electrozi. Daca potentialul grila-sursa devine pozitiv dar mai mic decat valoarea U numita de prag. O<UGS<U, golurile majoritare din substrat aflate intre sursa si drena sant respinse si regiunea ramane golita de purtatori de sarcina (curentul drena - sursa ramane nul).Daca potentialul grila-sursa depaseste tensiunea de prag UGS>U, in regiune sunt atrasi purtatori de tip n (electroni) si intre drena si sursa se inchide un curent I care creste la cresterea tensiuni U . Rezulta ca intre cele doua insule de tip n a aparut un canal cu conductie tot de tip n (tipul de conductie s-a inversat in canal). Caracteristica de transfer IDS =f a unui tranzistor MOS cu canal n este reprezentata in Fig.20.

Valoarea tensiuni de prag UT este data de parametri de proces tehnologic .Tranzistorul MOS cu canal q are o structura similara si se obtine prin interschimbarea zonelor de tip q si n. Comportarea tranzistorului MOS cu canal q este de asemeni similara celei a tranzistorului MOS cu canal n inversandu-se polaritatile tensiunilor si sensurile curentilor. In Fig. 20.b sunt reprezentate simbolurile grafice si modul de polarizare pentru tranzistoarele MOS cu canal n si respectiv q .

Evolutia tehnologica a circuitelor MOS a urmat calea: circuite PMOS(realizate cu tranzistoare MOS cu canal q), circuite NMOS(realizate cu tranzistoare MOS cu canal n) si circuite CMOS(complementary - symetry MOR realizate cu tranzistoare MOS cu canal q si MOS cu canal n).

Indiferent de tehnologia folosita,circuitele MOS pot fi statice sau dinamice. Circuitele MOS statice se caracterizeaza prin faptul ca informatia logica se transmite la iesire in mod neconditionat. Circuitele MOS dinamice realizeaza functia logica si o transmit la iesire doar la momente determinate de un semnal f de tact. Acest mod de functionare determina o miscare a puteri consumate si o oarecare crestere a vitezei de lucru. Deoarece in prezent este cea mai raspandita, in continuare se va analiza mai pe larg familia de circuite logice CMOS.

Seria CMOS 4000care se fabrica in tara are tensiunea de alimentare intre 3 si 18V iar tensiunea de prag este 1,5V.

La fel ca si pentru familia TTL ,datorita variatiilor produse de tolerantele componentelor si de zgomot, nici pentru familia CMOS nu este posibila reprezentarea valorilor logice 0L si 1L prin doua nivele unice de tensiune. Domeniile de tensiune corespunzatoare valorilor logice sunt reprezentate grafic in Fig.21a pentru UDD =5V si se definesc prin relatiile:

UDHmin =UDD -0,05VV UDLmax =0,05V

UIHmin = 0,7UDD UILmax =0,3U

Conform( 27.) rezulta pentru circuitele CMOS o margine de zgomot de aproximativ 30% din UDD :

MZL =UILmax -UOLmax =0,3UDD -0,05 0,3UDD

MZH =UIHmin -UDHmin =0,7UDD -UDD +0,05 -0,3UDD

Pentru UDD = 5V se obtine o margine de zgomot de 1,5V fata de 0,4V pentru familia TTL . Imunitatea crescuta la zgomot este un alt avantaj important al familiei CMOS .Circuitul fundamental al familiei CMOS este inversorul a carui schema electrica este redata in Fig. 21.b.

In Fig. 21.c sunt prezentate simbolul si tabelul de adevar ale circuitului inversor . Inversorul se compune din doua tranzistoare MOS unul cu canal n si celalalt cu canal p . Conexiunea comuna a grilelor reprezinta intrarea iar conexiunea comuna a drenelor reprezinta iesirea inversorului . Cele doua tranzistoare functioneaza cu tensiuni de polaritate opusa : astfel o tensiune pozitiva la intrare mai mare de 1,5 V (practic UDD pentru 1L il va bloca pe T1 si il va deschide pe T2 ceea ce face ca iesirea sa fie comutata la o valoare scazuta (practic OV ) corespunzatoare nivelului 0L si invers o tensiune pozitiva sub 1,5V aplicata la intrare (practic OV pentru 0L ),il va deschide pe T1 si prin blocarea lui T2 va asigura la iesire o valoare ridicata de tensiune (practic UDD )corespunzatoare nivelului 0L. Rezulta ca in regim static intre u si masa nu exista o cale directa de curent (cand T1 conduce T2 e blocat si invers ) si deci puterea consumata de inversorul CMOS in regim static este practic nula .

Perechea complementara de tranzistoare care realizeaza functia logica NU(Fig. 21b)permite sa se obtina simplu orice alta functie logica. In Fig. 22a sunt reprezentate schema electrica, simbolul si tabelul de adevar al portii SAU-NU. Aceasta este formata din doua perechi de tranzistoare complementare, tranzistoarele MOS cu canal q T si T fiind legate in serie iar cele cu canal n T si T fiind legate in paralel.

Grilele tranzistoarelor T1 si T3 sunt legate impreuna si reprezinta intrarea A pentru poarta SAU-NU iar grilele lui T2 si T4 legate impreuna formeaza intrarea B a portii.

Pentru ca iesirea portii SAU-NU sa fie in 1L (U )trebuie ca atat T3 cat si T4 sa fie blocate deci ambele intrari A si B trebuie sa fie in OL (OY). In aceasta situatie T1 si T2 conduc si potentialul iesirii este practic UDD .Este suficient ca o singura intrare sa comute in 1L pentru ca tranzistorul MOS cu canal q corespunzator sa se blocheze si sa intrerupa calea de curent intre UDD si iesire iar tranzistorul MOS cu canal n corespunzator sa se deschida si potentialul iesirii sa scada practic la OV(OL ). InFig.22.b sunt reprezentate schema electrica, simbolul si tabelul de adevar al portii SI-NU. De data aceasta tranzistoarele MOS cu canal q sunt legate in paralel si cele cu canal n in serie. In acest caz iesirea este in O(OV) doar atunci cand ambele intrari A si B sunt in 1L: atunci T1 si T2sunt blocate si nu exista cale de curent intre UDD si iesire iar T3 si T4 sunt ambele in conductie si potentialul iesirii este practic OV(OL ).

Este suficient ca o singura intrare sa comute in OL pentru ca tranzistorul MOS cu canal q corespunzator sa intre in conductie iar cel cu canal n corespunzator sa se blocheze si potentialul iesirii sa devina practic UDD (1L).

In Fig.22.c sunt reprezentate schema electrica si simbolul unui circuit specific familiei CMOS si anume poarta de transmisie. Aceasta consta dintr-o pereche complementara de tranzistoare MOS conectate in paralel. Se comporta ca un comutator, variabila logica A fiind intrarea de control. Tensiunile de intrare trebuie sa fie pozitive in raport cu potentialul substratului tranzistorului MOS cu canal n (USS ), si negative in raport cu potentialul UDD al substratului tranzistorului cu canal q desi USS <UI <UDD . Cand A este1L (UDD )respectiv A in OL (USS ) poarta este

deschisa:tranzistorul T1 este deschis daca USS <UI <UDD -U iar T2 daca USS +UT <UI <UDD deci pentru USS +UT<UI <UDD -UT (UT =1,5V) sunt deschise ambele tranzistoare ; conectarea in paralel a tranzistoarelor complementare face ca excursia de tensiune la intrare sa nu fie limitata de tensiunea de prag UT ; rezistenta in stare deschisa a portii este de ordinul zecilor - sutelor de. Cand A este 0 respectiv A in 1 ambele tranzistoare sunt blocate si poarta este inchisa; intre intrare si iesire apare o rezistenta de ordinul sutelor de M .

Circuitele CMOS prezentate anterior contin un numar mic de tranzistoare si nici un element de circuit pasiv si de aceea aria de siliciu ocupata de ele este mica. Acest fapt determina un alt avantaj al tehnologiei CMOS si anume densitate mare de integrare.

Asa cum s-a aratat anterior, puterea consumata de o poarta CMOS in regim static este practic nula. In regim dinamic pentru un inversor de exemplu (Fig.21.b), pe durata comutari acestuia dintr-o stare logica in alta pentru un timp foarte scurt conduc ambele tranzistoare complementare. Puterea consumata de o poarta depinde deci de tensiunea de alimentare a acesteia si de frecventa si durata fronturilor impulsurilor aplicate la intrare. De exemplu pentru UDD =10V si pentru un semnal in impulsuri la intrare cu frecventa de 100WHz si fronturi de 20ns, puterea totala consumata de o poarta CMOS este de 50nW deci cu peste doua ordine de marime mai mica fata de poarta TTL.

Timpul de propagare al portii CMOS se calculeaza tot cu relatia (28), unde tpHL si tpLH sunt definiti in Fig. 18a. Timpul de propagare creste o data cu cresterea sarcinii capacitive a portii. De exemplu, o poarta CMOS alimentata la 10V si cu o sarcina capacitiva de 50 F are un timp de propagare de aproximativ 66ns, deci sensibil mai mare fata de poarta TTL.

Intrarea unui tranzistor MOS este practic un condensator (contactul metalic al grilei si substratul semiconductor formeaza armaturile iar SI O2 este dielectricul), de aceea curentul absorbit la intrare de o poarta CMOS este practic nul. La prima vedere s-ar putea spune ca incarcarea la iesire a unei porti este practic nula si deci fan-out-ul este nelimitat. Fiecare intrare CMOS conectata la o iesire CMOS reprezinta o sarcina capacitiva de aproximativ5pF care creste corespunzator timpului de propagare a semnalului. De aceea principala limitare a capacitatii de incarcare a iesirii o constituie frecventa de lucru a aplicatiei concrete. Pentru aplicatii necritice din acest punct de vedere se poate considera ca circuitele CMOS au un fan-out egal cu 50.

Pentru a reduce influenta zgomotului si pentru a nu inrautati timpul de propagare intrarile portilor SI-NU se conecteaza la UDD iar cele ale portilor SAU-NU la USS prin rezistente avand valori intre 10kr si 100kr .

Copyright © 2025 - Toate drepturile rezervate