| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

CIRCUITE BASCULANTE BISTABILE

S Q S

Master

R Q R

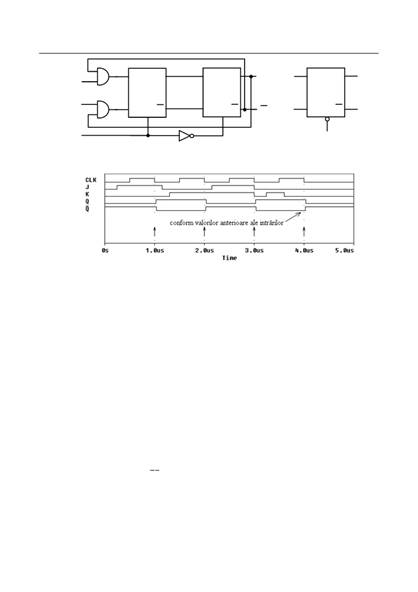

Fig. Structura si simbolul logic pentru bistabilul JK master-slave

Forme de unda in functionarea bistabilului JK master-slave

Singura deficienta pe care o mai are o astfel de structura se datoreaza tranzitiilor nedeterminate, neafectate de principiul master-slave. Pentru o functionare corecta se impune ca intrarile in master sa nu se modifice pe durata in care semnalul CLK este in 1 logic. In figura 6.19 se poate vedea o functionare in conformitate cu tabelul tranzitiilor, dar modificarea intrarilor pe durata de 1 logic a semnalului CLK ar putea produce o comutare care corespunde valorilor anterioare ale intrarilor J si K.

Principiul declansarii pe front

Restrictia de a nu

modifica intrarile pe durata palierului de 1 logic al ceasului este

eliminata de structura cu declansare pe front. De fapt si

structura master-slave comuta pe

front, dar structura de care ne ocupam acum comuta ca urmare a

tranzitiei pozitive a

ceasului, notat aici tot cu CLK. Vom studia in continuare bistabilul SR cu

declansare pe

front si vom vedea care au fost etapele succesive care au dus la

realizarea acestei structuri.

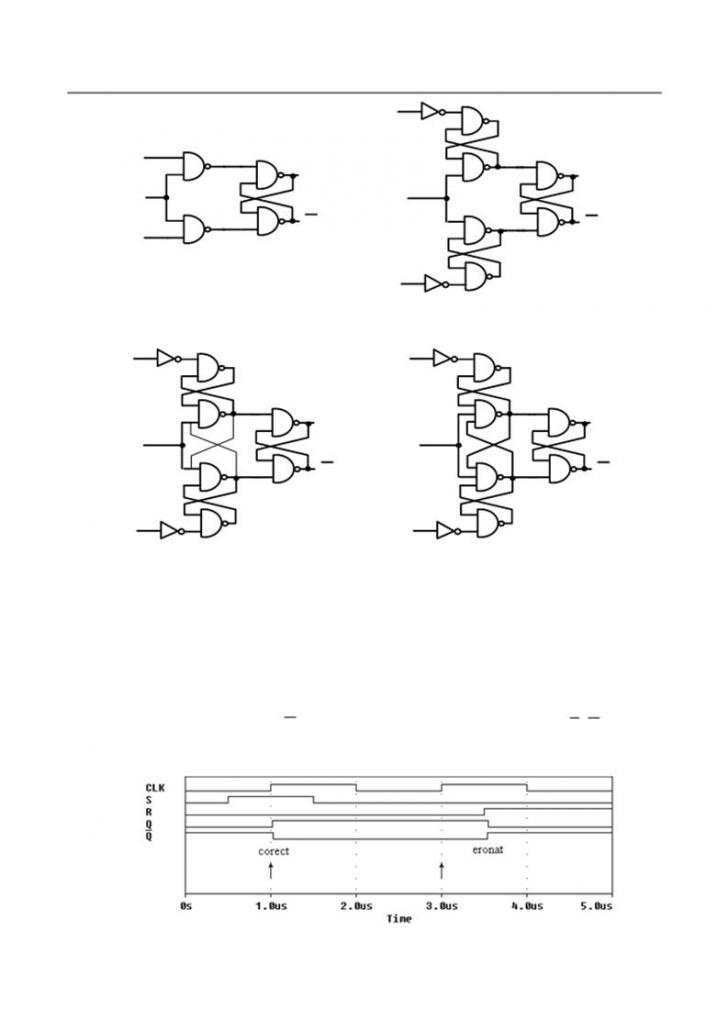

S-a pornit de la structura latch-ului SR cu ceas si s-au inlocuit portile logice de pe primul nivel cu cate un latch SR, in scopul memorarii intrarilor. Aceasta transformare este reprezentata in figura 6.20. Inversoarele au fost introduse pentru a pastra nivelul logic pe care sunt active semnalele de intrare S si R.

Urmatoarea etapa

are in vedere eliminarea posibilitatii de aparitie a

combinatiei

interzise pe intrarile latch-ului SR de

la iesire. Reactiile introduse cu linii punctate in figura

6.21 rezolva problema, numai ca apare alta, si anume scurtcircuitarea iesirilor portilor logice conectate la intrarea CLK. Din acest motiv, portile respective se inlocuiesc cu porti SI-NU care au trei intrari.

Principiul declansarii pe front

S

S

Q Q

CL CLK

Q Q

R

R

Fig. 6.20 Memorarea intrarilor in latch-ul SR cu ceas

S S

Q Q

CLK CLK

Q Q

R R

Fig. 6.21 Evitarea combinatiei 00 pe intrarile latch-ului SR de la iesire

Circuitul rezultat mai are doua mici deficiente. Pe de o parte, daca S = R = 0 si una din intrari se modifica pe palierul de 1 logic al ceasului, se va produce o comutare chiar in acel moment si nu pe frontul crescator al ceasului. Pe de alta parte, combinatia interzisa pe intrari S = R = 1 se mentine si in acest caz. Daca prima deficienta poate fi inlaturata, cea de-a doua nu, fiind o proprietate intrinseca a bistabilului SR.

Deficienta semnalata mai sus este pusa in evidenta pe formele de unda din figura

6.22. Eliminarea ei se face prin introducerea unor reactii suplimentare in circuit: astfel intrarea S se inlocuieste prin S+ R Q⋅, iar intrarea R se inlocuieste prin R+ S ⋅Q . Schema logica rezultata este prezentata in figura 6.23.

Fig. 6.22 O deficienta a structurii din figura 6.21

CIRCUITE BASCULANTE BISTABILE

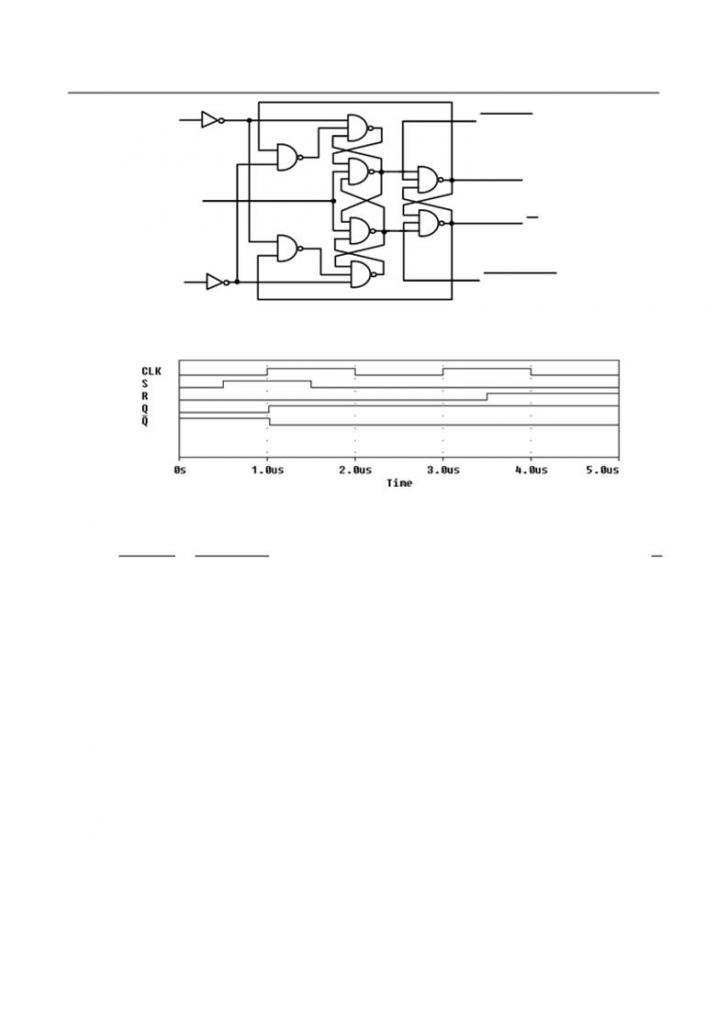

S PRESET

Q

CLK

Q

R PRECLEAR

Fig. 6.23 Structura bistabilului SR cu declansare pe front

Fig. 6.24 Functionarea bistabilului SR cu declansare pe front

Putem observa ca schema finala a bistabilului SR contine si doua intrari asincrone, numite PRESET si PRECLEAR. Prin activarea lor pe 0 logic, ele pozitioneaza iesirile Q si Q in 10, respectiv 01, fara nici o legatura cu semnalul de ceas. Formele de unda din figura 6.24 demonstreaza ca deficienta semnalata a fost inlaturata, si circuitul comuta numai pe frontul crescator al semnalului CLK.

Metastabilitate

Starea metastabila este un nivel logic intermediar, cuprins intre 0 si 1 logic, care poate apare la iesirile unui circuit bistabil, atunci cand nu se respecta durata minima a timpilor de setup si de hold. Acesti timpi minimi sunt definiti pe desenul formelor de unda din figura 6.25.

Timpul de setup reprezinta timpul scurs din momentul in care s-a modificat intrarea D si pana la aparitia frontului activ al semnalului CLK, iar timpul de hold este timpul scurs de la aparitia frontului activ al semnalului CLK si pana la noua modificare a intrarii de date. Daca intrarea de date D este stabila in aceasta fereastra de timp, atunci iesirea Q comuta in conformitate cu tabelul tranzitiilor dupa un timp notat cu tpd. Daca este instabila, atunci este probabil ca dupa timpul tpd sa intre in starea metastabila, care dureaza tr

Teoretic, durata starii metastabile ar putea fi infinita, dar practic, probabilitatea de

mentinere a ei scade exponential cu timpul. Parametrul tr se mai numeste timp de rezolutie a metastabilitatii si nu ar trebui sa depaseasca o perioada a semnalului de ceas.

ATTENTION!

TRIAL LIMITATION - ONLY 3 SELECTED PAGES MAY BE CONVERTED PER CONVERSION.

PURCHASING A LICENSE REMOVES THIS LIMITATION. TO DO SO, PLEASE CLICK ON THE FOLLOWING LINK:

Copyright © 2025 - Toate drepturile rezervate