| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Interfata Ethernet pentru standard

1 Controlerul Ethernet EDLC

Descriere

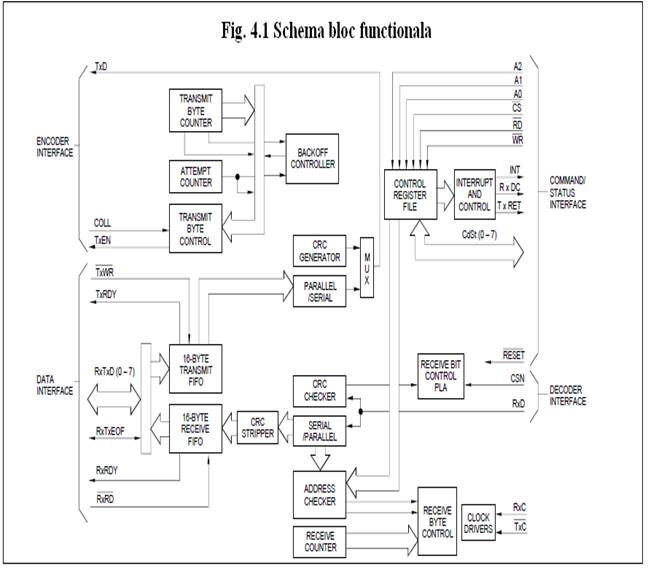

EDLC este destinat sa suporte DLL-urile specificate de Ethernet pentru retelele locale(LAN). Interfata sistemului este optimizata pentru a usura conexiunile cu controlerele DMA(Direct memory access=acces direct la memorie), specifice pentru operatii de viteze foarte mari. 80C03 are interfata directa cu 8023A si convertorul de coduri Manchester(MCCTM ) pentru a completa functiile permanente ale statiilor Ethernet. Protocolul folosit este Carrrier Sense(detectarea purtatoare=existenta semnalului in cablu), acces multiplu cu detectarea coliziunii(CSMA/CD : Carrier Sense Multiple Acces/Collision Detection). Cipul EDLC 80C03 este creat pentru a simplifica dezvoltarea comunicatiilor Ethernet ale sistemelor computerizate. Ofera o solutie economica pentru a construi un nod Ethernet, oferind comunicatii de viteza mare 10MB/s si fiind capabil sa 'vada' aplicatiile din terminale, statii de lucru, computere personale, sisteme mici de afaceri; are o interfata de sistem universala compatibila cu aproape orice microprocesor, microcalculator, oferind posibilitatea operatorului de a regla,pentru orice aplicatie, balanta pret/performante. Sectiunile cipului EDLC de transmitere si de receptie sunt independente si pot opera simultan.

80C03 este compatibil cu SEEQ 8003 si are caracteristici suplimentare de programare.

Caracteristici

Filtru multicast pe 64 biti ;

Transmiterea numarului de coliziuni ;

Numararea tuturor coliziunilor ;

Raportarea statutului in care se afla purtatorul si SQE in timpul transmisiei ;

Nu transmite CRC(cyclic redundancy check ) sau preambul ;

Primeste CRC, modul de receptare adrese grup, modul de receptare rapida dezactivat si modul Full Duplex.

Mod de functionare

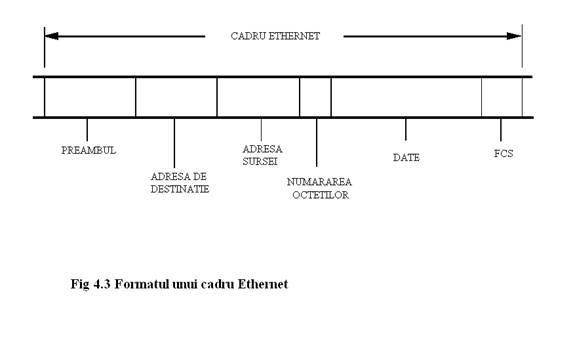

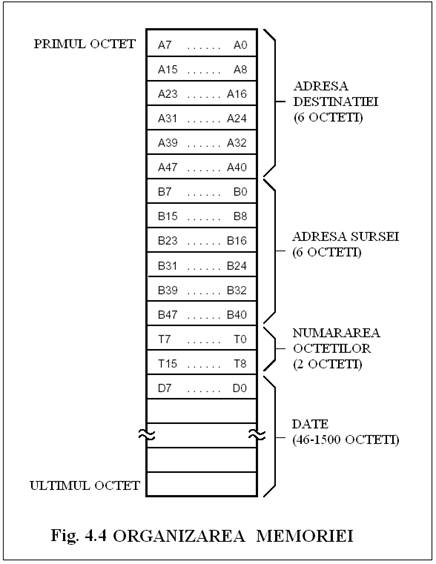

La o retea de comunicare Ethernet, informatia este transmisa si receptata pe pachete de date sau cadre. Un cadru Ethernet contine doua campuri de adresa, un camp pentru numararea bitilor, un camp pentru informatie si o secventa de verificare (FCS). Fiecare camp are un format specific, exact cum este descris in Fig. 3. Un cadru Ethernet are o lungime minima de 64 octeti si o lungime maxima de 1518 octeti.

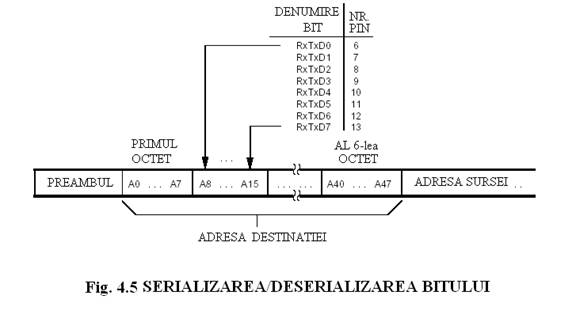

Preambulul este un camp de 64 biti, format din 62 biti alternanti de '1' si '0', urmati la sfarsit de '11', care este un indicator de sfarsit.

Adresa destinatiei este un camp de 6 octeti care contin adresa statiei, o adresa brodcast, sau o adresa multicast, spre care este directionat acest bloc.

Adresa sursei este un camp de 6 octeti care contine adresa specifica statiei de unde provine informatia.

Campul de numarare a bitilor este alcatuit din 2 biti care ne ofera informatii despre numarul de biti de date valide din Data Field, care poate fi intre 46 si 1500. Acest camp nu este detectat de DLL si este trecut prin cipul EDLC pentru a fi coordonat de Layer-ul clientului.

Campul datelor este alcatuit din 46-1500 octeti de informatii care sunt complet transparente, in sensul ca nu se poate ivi nici o secventa arbitrara de octeti.

Secventa de verificare (Frame check sequence: FCS) este o secventa ciclica de verificare de 32 biti , calculata ca o functie a campului adresa de destinatie, a campului adresa sursa, a tipului campului si a informatiei campului. FCS este adaugat fiecarui camp transmis si folosit la receptie pentru a determina daca este valid campul receptionat.

Transmitting(transmitere)

Transmiterea are loc cu ajutorul : Preambulului, patru campuri de informatii, si FCS-ului(care este calculat in timp real de cipul EDLC si este adaugat automat la sfarsitul datelor transmise serial). Cipul EDLC incadreaza acest camp intr-un cadru Ethernet prin inserarea unui preambul prioritar si adauga un CRC dupa campul informatiei. Acesta poate fi programat pentru a exclude inglobarea preambulului si/sau FCS-ului din transmiterea datelor. In acest caz, se presupune ca cele doua sunt furnizate ca parti ale informatiilor inscrise pe cip.

Initierea/Amanarea transmisiei

Codul Ethernet initiaza o transmisie stocand intregul continut al informatiei pentru a fi transmis intr-un buffer extern al memoriei, dupa care transmite octetii initiali ai cadrului la bufer-ul EDLC de transmisie. Transferurile buffer-ului catre FIFO sunt coordonate prin interfetele TxWR si TxRDY , ca in Fig. 5.

Transmisia informatiilor in retea va avea loc daca reteaua nu a fost ocupata un timp minim de amanare de 9.6 µs si nu a fost satisfacuta nici o cerinta de retransmisie. Cand incepe transmisia, cipul EDLC activeaza linia de transmisie disponibila (TxEN), concomitent cu transmisia primului bit din preambul pe care il mentine activat pe durata transmisiei.

Coliziunea

Cand au loc transmisiile concomitente de la doua sau mai multe noduri Ethernet (coliziune), cipul EDLC opreste transmisia octetilor de date in buffer-ul de transmisie si transmite un model Jam care consta in 55555555 hex. La sfarsitul transmisiei Jam, cipul EDLC emite un semnal TxRET catre CPU si incepe perioada de asteptare pentru retransmitere.

Pentru reinitierea transmisiei, octetii initiali din campul informatiei trebuie reincarcati in buffer-ul EDLC de transmisie. TxRET este folosit pentru a indica managerului de buffer nevoia de reinitializare.

Programarea

retransmisiei este determinata de un proces aleator controlat numit

Truncated Binary Exponential Backoff (Algoritm ce se ocupa de

controversele in utilizarea retelei). Cipul EDLC

asteapta un interval aleator intre 0 si ![]() sloturi de timp (51.2µs pe slot de timp

) inainte de a incerca retransmisia, unde 'k' este numarul curent

al incercarii de retransmisie (nu depaseste 10).

sloturi de timp (51.2µs pe slot de timp

) inainte de a incerca retransmisia, unde 'k' este numarul curent

al incercarii de retransmisie (nu depaseste 10).

* slot de timp = de doua ori timpul necesar unui puls electronic

Cand se executa 16 incercari consecutive de transmisie si toate s-au sfarsit din cauza coliziunii, Controlul de transmisie EDLC acorda un bit de eroare si intrerupe CPU daca este activat.

Sfarsitul transmisiei

Transmisia se incheie in urmatoarele conditii :

Normal : cadrul a fost transmis cu succes, fara controverse. Incarcarea ultimului octet de date in buffer-ul de transmisie este semnalata cipului EDLC prin activarea semnalului RxTxEOF.

Coliziune : se incearca transmisia de doua sau mai multe noduri Ethernet. Secventa Jam se transmite, bitul de stare a coliziunii este activat, Collision Counter (numararea coliziunilor) este actualizat, se genereaza semnalul TxRET si incepe intervalul de retransmitere.

Underflow (se refera la situatia in care se incearca citirea unui buffer gol) : data ce trebuie transmisa nu este gata in momentul transmisiei. Odata inceputa transmisia, cipul EDLC trebuie sa transmita, in medie, un octet la fiecare 800 ns. Daca aceasta conditie este indeplinita, se incheie transmisia, rezultand un semnal TxRET si se fixeaza bitul de stare al 'Transmit- Underflow'.

16 Incercari de transmisie : daca are loc o coliziune, pentru a 16-a incercare consecutiva, se fixeaza bitul de stare pentru aceasta si pentru coliziune, se genereaza semnalul TxRET, si se incepe intervalul de retransmitere. Contorul ce retine numarul de coliziuni este modulo 16 si deci, se trece la cea de-a 17-a coliziune. Bitii 11-15 din registrul contorului coliziunilor (modul 80C03) indica numarul de incercari pentru reinitializarea coliziunii.

Receptie

Cipul EDLC monitorizeaza continuu reteaua. Cand se receptioneaza activitate in CSN, linia devine activa, cipul EDLC se sincronizeaza, dupa care verifica campul adresei de destinatie. Depinzand de modul de potrivire al adresei specificate, cipul EDLC fie recunoaste campul ca fiind adresat lui insusi intr-un mod general sau specific, fie anuleaza receptia campului. 80C30 permite, de asemenea, sa numere toate coliziunile pe care le gaseste in retea.

Procesul preambul

Cipul EDLC recunoaste activitate in reteaua Ethernet prin CSN. Preambulul are o lungime normala de 64 biti (8 octeti). Preambulul consta intr-o secventa de 62 biti alternanti de '0' si '1', iar la sfarsit bitii '11' si un camp de informatie. Pentru a se ivi bucla locala a decodorului, cipul EDLC, asteapta 16 biti pana sa caute secventa '11' care indica sfarsitul preambulului. Daca cipul EDLC primeste in preambul '00' inainte de a primi '11', inseamna ca a avut loc o eroare. Secventa nu este receptionata iar cipul EDLC incepe monitorizarea retelei pentru a descoperi o noua activitate.

Potrivirea adresei

Adresele Ethernet sunt alcatuite dintr-un camp de 6 octeti. Primul bit din adresa ne arata daca este o adresa de statie(Station Address) sau o adresa Multicast/Broadcast (modul de adresare multicast este modul prin care o informatie este adresata unui grup de destinatii in acelasi timp, folosind cea mai eficienta stategie/broadcast= a transmite,a difuza).

|

Primul Bit |

Adrese |

|

Adresa Statiei(Fizica) |

|

|

Adresa Multicast/Broadcast(Logica) |

Potrivirea adreselor se face astfel:

Adresa statiei: toti octetii adreselor de destinatie trebuie sa corespunda cu octetii gasiti in registrul de adrese a statiei(Station Address Register). Daca modul adreselor grup(Group Address) este activat, ultimii 4 biti din adresa statiei sunt mascati in timpul potrivirii adreselor.

Dupa ce se calculeaza FCS-ul primilor 6 octeti din adresa campului, 80C03 foloseste bitii de la 0 la 5 ca un registru de adrese multi-cast. Bit-ul 0 al FCS-ului este in punctul in care intra data receptionata in circuitul FCS-ului. Daca bit-ul corespunzator din registrul de adrese multi-cast este '1', atunci 80C03 va primi secventa, altfel o va anula. Adresarea catre registrul de adrese Multicast se face folosind bitii de la 0 la 2, pentru a determina care octet este selectat si bitii de la 3 la 5, pentru a determina care bit este selectat, ca in TABEL 6.

TABEL 6

|

Bitii FCS 1 2 |

Selectia octetului |

|

0 0 0 1 1 0 1 1 1 1 |

Octetul 0 Octetul 1 Octetul 2 Octetul 3 Octetul 7 |

|

Bitii FCS 5 6 |

Selectia bitului |

|

0 0 0 1 1 0 1 1 1 1 |

Bit 0 Bit 1 Bit 2 Bit 3 Bit 7 |

Adrese Multicast: daca primul bit al adresei care soseste este 1 si cipul EDLC este programat sa accepte adresele Multicast, fara a folosi filtrarea Hash, secventa este acceptata. 80C03 poate fi si el programat pentru a folosi filtrul Hash, pentru a determina acceptarea adreselor Multicast.

Adresele Broadcast: cei sase octeti ai destinatiilor de adrese sosite trebuie sa fie toti FF hex. Daca cipul EDLC este programat sa accepte adrese Broadcast sau Multicast, secventa va fi primita.

Daca secventa sosita este adresata special cipului EDLC (adresa destinatiei coincide cu registrul statiei de adrese), sau apartine unui grup de interes general (adrese Broadcast/Multicast ), cipul EDLC va trece secventa din Preambul si FCS in buffer-ul CPU, indicand orice conditii de eroare la sfarsitul cadrului. Daca, totusi, adresa nu se potriveste, indata ce greseala este recunoscuta, cipul EDLC va termina receptia si va emite un RxDC.

Daca cipul EDLC poate sa fie programat prin bitii Match Mode (mod de potrivire) ai Registrului de Primire Comanda (Receive Command Register) acesta :

Terminarea Receptiei

Receptia se termina atunci cand este indeplinita una din urmatoarele conditii:

Carrier Sense este inactiv: indica faptul ca traficul pe cablul de Ethernet nu mai este prezent;

Supraaglomerare (Overflow): din anumite motive, nodul principal nu poate goli buffer-ul de receptie la fel de rapid cum este umplut, ivindu-se o eroare ca in cazul in care datele se pierd. In medie, buffer-ul de receptie trebuie sa fie verificat la fiecare 800 ns, pentru a evita aceasta conditie;

Conditiile receptionarii secventelor (Frame Reception Conditions): la sfarsitul receptiei, cipul EDLC va determina starea secventei primite si o va incarca corespunzator in Registrul Starilor de Receptie(Receive Status Register). O intrerupere se va isca daca sunt prezente conditiile specificate in Registrul Comenzilor de Receptie(Receive Command Register). Cipul EDLC poate semnala urmatoarele conditii la sfarsitul receptiei secventei:

Supraaglomerare: buffer-ul de receptie intern al EDLC se supraaglomereaza;

Eroare de driblare (Dribble Error): Carrier Sense nu s-a dezactivat la receptia datei;

Eroarea CRC (Cyclic Redundancy Check = verificarea ciclica a redundantei): al 32-lea bit CRC transmis cu secventa nu se potriveste cu cel calculat la receptie;

Secventa scurta: o secventa continand mai putin de 64 de octeti de informatie a fost receptionata(inclusiv FCS);

Secventa buna: o secventa care este receptionata si nu prezinta o eroare CRC, Secventa scurta sau conditia de supraaglomerare.

Interfata sistemului

Cipul EDLC al interfetei de sistem este alcatuit din doua circuite care conecteaza CPU cu alte echipamente intr-un computer(Bus), si din semnale de control. Informatiile sunt citite si scrise cu ajutorul bitilor de Receptie/Transmisie ai Bus-ului de date RxTxD (0-7). Aceste transferuri sunt controlate de semnalele TxRDY si TxWR, pentru transmiterea datelor si de RxRDY si RxRD, pentru receptionarea lor. Toate comenzile si adresele statiilor sunt scrise, si toate starile citite separat (Command/Status Bus CdSt (0-7)). Aceste transferuri sunt controlate prin semnale CS, RD, WR si A0-A2. Registrele de comanda si de stare ale cipului EDLC pot fi accesate oricand. Totusi, este recomandata scrierea in registrul de comanda numai pe durata pauzelor dintre secvente.

Cu exceptia celor doi biti Match Mode din Receive Command Register, toti bitii din cele doua registre de comanda sunt biti activi intrerupti temporar. Schimbarea acestor biti in timpul secventei de transmisie nu afecteaza integritatea secventei.

Citirea registrului de stari poate sa aiba loc oricand pe durata transmisiei sau receptiei.

TABELUL 7 Registru Intern de Adrese(modul 8003)

|

REGISTRUL DE ADRESE |

DESCRIEREA REGISTRULUI |

||||

|

A2 |

A1 |

A0 |

Citire |

Scriere |

|

|

Adresa Statie 0 |

|||||

|

Adresa Statie 1 |

|||||

|

Adresa Statie 2 |

|||||

|

Adresa Statie 3 |

|||||

|

Adresa Statie 4 |

|||||

|

Adresa Statie 5 |

|||||

|

starea Rx |

Comanda Rx |

||||

|

starea Tx |

|

||||

Registrele de Stare (Status Register) sunt registre care nu pot fi decat citite; registrele de Comanda si de Adrese ale Statiilor nu pot fi decat scrise. Accesul la aceste registre se face prin interfata CPU: semnale de control CS, RD, WR si Comanda/Starea Bus-ului de date CdSt (0-7).

Registrul Adreselor de Statii(Station Address Register)este format din 6 octeti. Continutul poate fi scris in orice ordine, cu bitul '0' al octet-ului '0' corespunzator primului bit primit(indica tipul adresei: fizica sau logica). Bitul 7 al adresei statiei octetului 5 este comparat cu ultimul bit al adresei destinatiei primite. Adresa Statiei ar trebui sa fie programata prioritar pentru a activa receptorul.

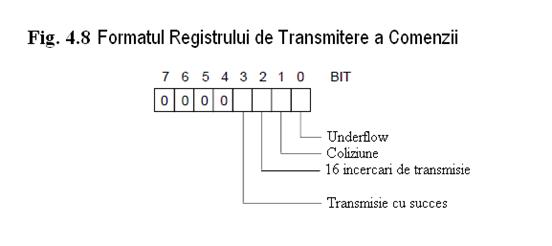

Registrul de Transmitere a Comenzilor (Transmit Command Register)- acest registru este cel care asigura controlul conditiilor capabile sa genereze intreruperi in transmitere(Fig. 8). Fiecare din cei patru biti, cei mai putin semnificativi, din registru, pot fi stabiliti sau stersi individual. Atunci cand sunt stabiliti, indeplinirea conditiei de asociere va cauza o intrerupere.

Cele patru conditii specifice care pot cauza o intrerupere sunt:

Underflow (incercare de a citi un buffer gol);

Coliziunea ;

16 Coliziuni;

Transmiterea cu succes.

Semnalul INT intrerupt va fi stabilit cand se iveste una sau mai multe dintre conditiile specifice de terminare a transmisiei si bitul de comanda asociat a fost stabilit; el va fi sters cand va fi citit Registrul de Transmitere a Starilor.

Toti bitii din Registrul de Transmitere a Comenzilor sunt goliti la resetarea cipului.

80C03 asigura noi caracteristici care sunt activate daca valoarea '1' corespunde bitilor 7, 6, 5, 4 in registrul de transmitere a comenzilor. Daca acesti patru biti sunt intotdeauna '0', atunci 80C03 va fi pe deplin compatibil cu 8003 EDLC.

Bitii 6 si 5 sunt folositi pentru a adresa noi registri in 80C03, impreuna cu pinii A2, A1, A0, RD, WR, CS.

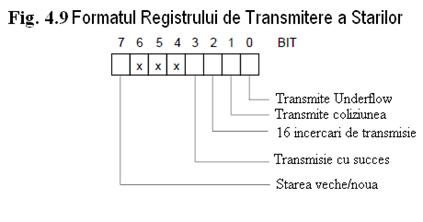

Registrul de Transmitere a Starilor(Fig. 9)- acesta este incarcat la sfarsitul fiecarei incercari de transmitere/retransmitere a unei secvente. El asigura raportarea starilor de transmitere normala/eronata pentru fiecare transmisie.

Bit-ul de stare vechi/nou (old/new status) este stabilit de fiecare data cand este citit Registrul Starilor de Transmitere si este rescris de fiecare data cand este incarcata o noua stare in Registrul de Transmitere a Starilor. In momentul in care cipul este resetat, bit-ul Old/New este stabilit, iar toti ceilalti sunt stersi.

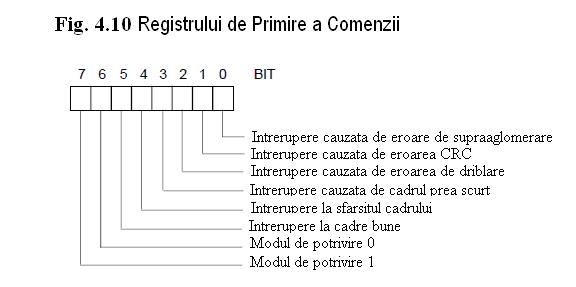

Registrul de Primire a Comenzii(Fig. 10)- are doua functii principale:

specifica adresa Match Mode;

specifica secventele de interes(acele secvente a caror stare trebuie sa fie salvata pentru verificare, chiar cu riscul de a pierde anumite parti din acestea)

Cand sunt stabiliti, bitii de la 0 la 5 ne specifica intreruperea si secventa de interes(Interrupt and Frame of Interest). Bit-ul 4 (End of Frame=sfarsit de cadru) specifica orice tip de secventa, mai putin overflow-ul.

TABELUL 11

|

Modul de Potrivire 1 |

Modul de potrivire 0 |

Functii |

|

|

Dezactivarea receptiei |

|||

|

Acceptarea tuturor cadrelor |

|||

|

Receptia statiei sau cadrelor broadcast |

|||

|

Receptia statiei sau cadrelor broadcast/multicast |

Match mode(modul de potrivire): modificarea bitilor Match Mode receptionati poate modifica starea de operare a cip-ului si poate sa obtina rezultate neasteptate(TABELUL 11).

Intrerupt Enable and Frame-of-interest activarea intreruperii si secventa de interes): cand se stabilesc, bitii de la 0 la 5 ne specifica natura intreruperii si conditia corespunzatoare de receptie a secventei; de asemenea, ne mai informeaza ca tipurile de secvente corespunzatoare sunt Secventele de Interes folosite de Registrul Starilor Receptionate pentru a controla incarcarea datelor.

Receive Status Register(Registrul Starilor Receptionate)- acesta reflecta, in mod normal, starea fiecarei secvente primite (cand s-a receptionat secventa sau receptia acesteia s-a terminat din cauza unei conditii de eroare). Registrul contine vechii/noii biti de stare care sunt stabiliti cand se citeste Registrul Starilor Receptionate sau cip-ul este resetat si sunt stersi doar atunci cand starile sunt incarcate pentru o Secventa de Interes. Toti ceilalti biti sunt stersi la resetarea cip-ului.

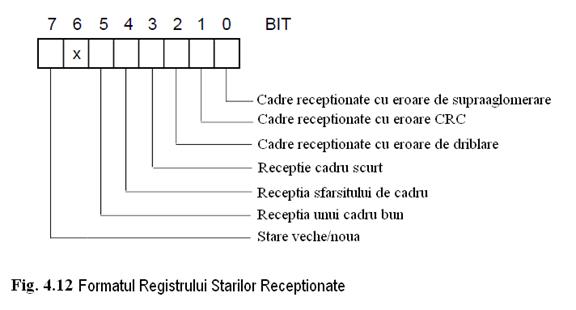

Formatul Registrului Starilor Receptionate(Fig. 12)

Bit-ul Nou/Vechi de stare scrie/protejeaza Registrul Starilor Receptionate cand acesta contine stari pe care Secventa de Interes nu le poate citi. Cand acest bit este '0', registrul este protejat la scriere. Bit-ul Nou/Vechi este sters de fiecare data cand starea unei noi Secvente de Interes este incarcata in registru si este stabilit dupa ce se citeste acesta stare(cand este zero indica o stare noua pentru Secventa de Interes).

Cu acesta exceptie cauzata de conditia de protejare la scriere, starea fiecarei secvente este intotdeauna incarcata in Registrul Starilor Receptionate la terminarea receptiei. Orice secventa receptionata cauzeaza o intrerupere care are loc daca bitul corespunzator de Intrerupere Activata este stabilit. Aceasta intrerupere este resetata la citirea registrului.

Aceste conditii realizeaza primirea si retinerea unui numar maxim de secvente bune.

Modul Multicast

Cand SEEQ 80C03 este programat sa receptioneze secvente multicast (modul de potrivire 3), dupa ce s-a calculat CRC din campul de adrese din secventa receptionata (primii 6 octeti ), se va indexa in filtrul de adrese multicast, depinzand de bitii 0-5 ai CRC-ului. Daca bitul corespunzator este '1', va receptiona secventa, altfel o va anula.

Bitul de stare SQE

Dupa transmiterea unei secvente, daca 80C03 nu receptioneaza o coliziune intr-o perioada de 0,4µs acest bit va fi stabilit. Odata stabilit, acesta va ramane asa pana va fi sters.

Registrele de numarare a coliziunilor(Collision Count Registers)- sunt doua Registre de numarare a coliziunilor de 16 biti, protejati la scriere, care sunt stersi la resetare: unul numara coliziunile la transmisie, iar celalalt numara toate coliziunile, in afara de cele din SQE_WINDOW(fereastra SQE). Transmitatorul numarului de coliziuni este format din 11 biti.

TxEN_no_carrier

Cand TxEN trece din 1 in 0, daca nu exista semnal in cablu, se stabileste acest bit(si va sta asa pana se sterge).

Modul Test(test mode)

Bitii 7 si 4 din registrul de control a comenzii sunt folositi doar pentru test. Pentru operatiuni normale acesti biti ar trebui sa fie '0'.

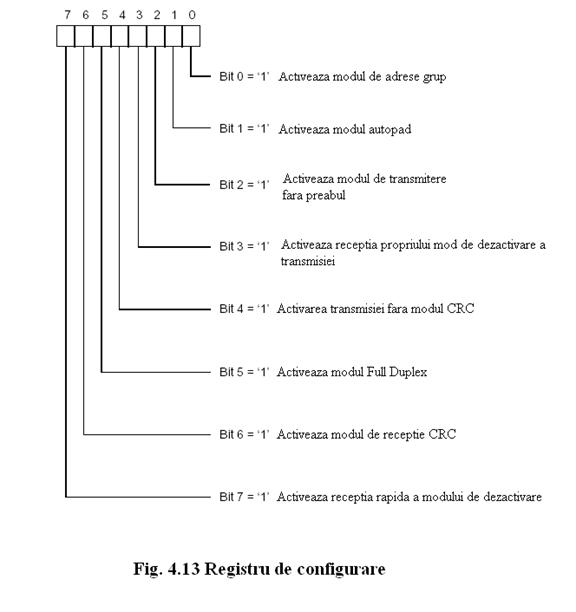

Registrul de Configurare Tx-Rx TX-Rx configuration Register)- este prezent doar in modul 80C03. Permite controlul caracteristicilor primite sau transmise. Toti bitii devin '0' la resetare.

Modul de Adresare a Grupului(Group Address Mode)

In acest mod, ultimii 4 biti din sirul de informatii receptionate serial pentru descrierea adresei sunt mascati (cand adresa de destinatie este comparata cu valoarea programata in registrul de adrese ale statiilor, pachetul de date nu va fi respins chiar daca ultimii 4 biti nu corespund ).

Transmiterea pachetelor in modul Autopad(Transmit Packet Autopad Mode): transmite pachetele cu mai putin de 60 octeti de date unui pachet standard IEEE 802.3 de lungime minima de 60 octeti, excluzand FCS. Parcurgerea se realizeaza cu octeti 00 hex.

Transmisia fara modul Preamble( Transmit No Preamble Mode) : previne adaugarea unui model de preambul la inceputul transmisiei datelor.

Receptia propriului mod de dezactivare a transmisiei(Rceive Own Transmit Disable Mode): previne 80C03 sa primeasca un pachet de date daca se mai transmite unul.

Transmisia fara modul CRC(Transmit No CRC Mode): previne transmitatorul sa anexeze date transmise cu un FCS.

Modul AutoDUPLEX(AutoDUPLEX Mode): in acest mod, transmitatorul va ignora existenta semnalului in cablu pana cand este gata sa transmita un pachet de date.

Receptia modului CRC(Receive CRC Mode): receptorul incarca cei 4 octeti ai FCS-ului in buffer-ul de receptie, impreuna cu informatiile care permit citirea valorilor din FCS.

Primirea rapida a modului de anulare (Fast Receive Discard Mode): semnalul de anulare receptionat(RxDC) apare dupa maximul de 400 ns dupa ce detectia semnalului in cablu scade.

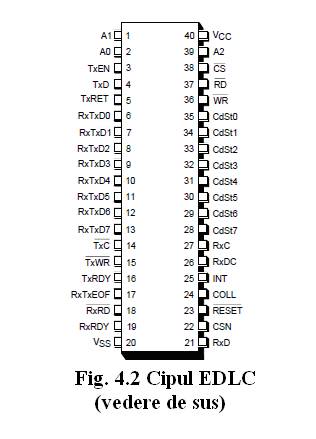

Descrierea pinilor

Cipul EDLC are patru grupuri de interfata a semnalelor:

Sursa de putere

Vcc=+5V

Vss este masa(nul);

Interfata de codare/decodare

TxC Transmit Clock(transmite ceasul): marime de intrare. Este folosit pentru sincronizarea datelor transmise de la cip la codor. Functioneaza continuu si este asincron cu RxC.

TxD Transmit Data(transmisia de informatii): marime de iesire. Datele seriale se transmit la codor.

TxEN Transmit Enable(activarea transmisiei): marime de iesire. Acest semnal este folosit pentru a activa codorul. Devine activ cand se transmite primul bit al preambulului si inactiv cand se transmite ultimul bit al secventei de date.

RxC Receive Data(primeste informatii): marime de intrare. Datele referitoare la timp sunt folosite pentru a sincroniza datele primite de ciplul EDLC de la decodor. Functioneaza continuu si este asincron cu TxC.

RxD Receive Data(receptia datelor): marime de intrare. Cip-ul EDLC receptioneaza serial informatiile de la decodor.

CSN Carrier Sense: marime de intrare. Indica cip-ului EDLC prezenta traficului in cablul coaxial. Devine activ cu primul bit receptionat al preambulului si inactiv dupa o perioada de 1 bit dupa ce ultimul bit al secventei este primit.

COLL Collision(coliziune): marime de intrare. Indica continutul transmisiei cablului Ethernet. Simplificata in timpul transmisiei, coliziunea este stabilita de un puls activ ridicat la intrare si resetata automat la sfarsitul transmisiei secventei JAM.

Interfata Buffer-ului de date

RxTxD(0-7) Receive/Transmit Data Bus(receptia/transmisia bus-ului de date): marime de intrare/iesire. Transmite octetul de date RxTxD de la/catre cipul EDLC buffer-ului de date de receptie/transmisie.

RxTxEOF Receive/Transmit End of Frame(Receptia/transmisia sfarsitului de secventa): marime de intrare/iesire. Indica ultimii octeti de informatie pe transmisia/receptia bus-ului de data.

RxRDY Receive Ready(receptia este gata): marime de iesire. Indica faptul ca cel putin un octet de date este disponibil in buffer-ul de receptie. Acest semnal va ramane activ atata timp cat un octet de date va ramane in buffer-ul de receptie. Cand aceasta conditie nu mai este indeplinita, RxRDY va trebui sa respecte marginile principale ale RxRD care indeparteaza ultimul octet de informatie din buffer-ul de receptie.

RxRD Receive Read Strobe(Primire Citire Semnal): marime de intrare. Activeaza transferul de date receptionate de la buffer-ul de receptie la RxTxD Bus. Datele sunt valide de la EDLC buffer-ul de receptie la pinii RxTxD in punctele crescatoare ale semnalului.

RxDC Receive Discard(receptia este respinsa): marime de iesire. Este activata cand se iveste una din urmatoarele conditii si bitul asociat de activare a intreruperii din Registrul de receptie a comenzii este resetat :

(1)Receive FIFO overflow(supraaglomerarea buffer-ul de receptie);

(2) CRC Error(eroare CRC);

(3) Short Frame Error(eroare de secventa prea mica);

(4) Receive frame adress nonmatch(nepotrivirea secventei de adresa receptionate);

(5) starea secventei anterioare s-a pierdut deoarece starea anterioara nu s-a citit.

RxDC nu se activeaza la erori atunci cand bitul de activare a intreruperii asociat este stabilit. In acest caz, EOF va fi generat imediat ce buffer-ul de receptie este citit. Aceasta permite receptia secventelor cu erori. RxDC actioneaza imediat pentru a sterge buffer-ul de receptie.

TxRDY Transmit Ready(transmiterea este pregatita): marime de iesire. Indica faptul ca buffer-ul de receptie are spatiu disponibil pentru cel putin un octet de informatii. Cand aceasta conditie nu mai este indeplinita, TxRDY va fi dezactivat luand in consideratie punctele crescatoare ale semnalului TxWR, care incarca buffer-ul de receptie. TxRDY este fortat sa devina inactiv in timpul resetarii si atunci cand TxRET este activ.

TxWR Transmit Write(transmite scrierea): marime de intrare. Sincrozizeaza transferul de date de la RxTxD bus la buffer-ul de receptie. Datele sunt scrise buffer-ul de receptie in punctele crescatoare ale semnalului.

TxRet Transmit Retransmit(transmite retransmite): marime de iesire. Este activat de fiecare data cand se iveste o transmisie slaba sau conditiile de coliziune.

Intrarea ADUPLX (PLLC Package Only=doar pachete PLLC): intrare folosita pentru a seta 80C03 in modul AutoDUPLEX. In acest mod transmitatorul nu va intarzia sa activeze semnalul de expediere.

Interfata de comanda/stare

CdSt(0-7) Command/Status Data Bus(comanda/starea bus-ului de data): marime de intrare/iesire. Aceste linii poarta comanda si starea la fel ca initializarea informatiei statiilor de adrese dintre cipul EDLC si CPU. Aceste linii au,de obicei, impedante ridicate pana cand se activeaza Cs si RD.

A0-A2 Address(adresele A0-A2): marimi de intrare. Sunt linii de adresa pentru a selecta registrele interne EDLC adecvate pentru citire/scriere.

CS Chip Select (Selectarea cipului): marime de intrare. Selectarea cipului trebuie sa fie activa odata cu RD sau Wr pentru a accesa cu succes registrul intern EDLC.

RD Read(Citire): marime de intrare. Activeaza citirea registrului intern EDLC odata cu CS.

WR Write(Scriere): marime de intrare. Activeaza scrierea registrului intern EDLC odata cu CS.

INT Interrupt(Intrerupere): marime de iesire. Activat prioritar unei varietati de conditii de transmitere si receptie; ramane activ pana cand este citit registrul de stare care contine motivul intreruperii.

Reset(Resetare): marime de intrare. Initializeaza controlul logic, sterge registrul de comanda, registrul de transmitere a starilor, bitii 0-5 ai registrului de receptie a starii, buffer-ul de receptie si transmisie, seteaza bitii de stare vechi/noi, activeaza RxDC si TxRET.

2 Convertorul de cod

Caracteristici

(10 = 10 Mbps; Base= Baseband; T = Twisted Pair)

(10 = 10 Mbps; Base= Baseband; 2 = 2x 100 meters)

Fig. 1.1Schema bloc functionala

Descriere

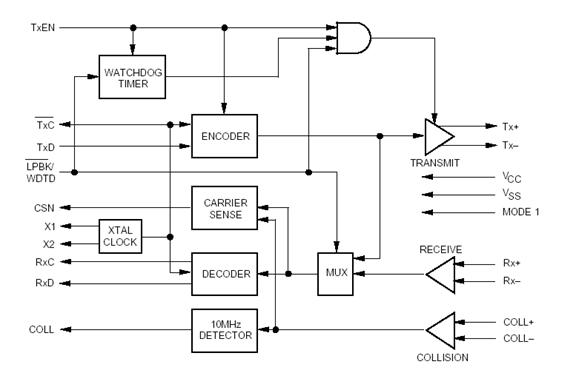

Cipul de codare Manchester SEEQ 8020 realizeaza atat codarea cat si decodarea functiilor straturilor fizice ale retelei locale Ethernet. Este compatibil cu orice standard ethernet definit de IEEE 802.3 si versiunea Ethernet Revision 1.

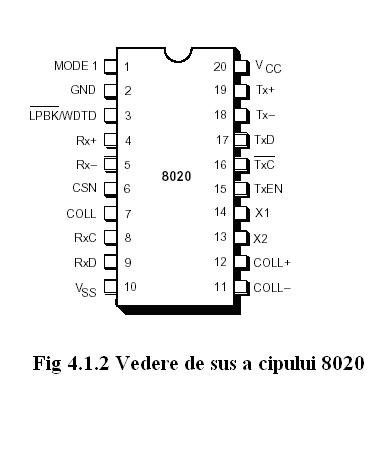

Configuratia pinilor

Modul de functionare

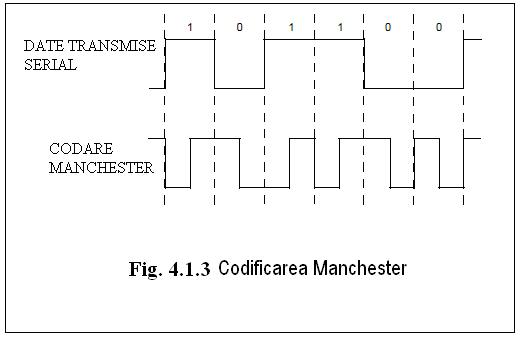

Este alcatuit din doua parti: transmisie si receptie. Transmitatorul foloseste codarea Manchester pentru a combina timpul si datele intr-un flux de serie. De asemenea, transmite diferential pana la 50 metri prin perechea de fire rasucite. Receiver-ul detecteaza prezenta datelor. 8020 MCC recupereaza datele codate si le decodeaza. Datele si ceasul sunt combinate pentru a fi posibila transmiterea lor printr-o singura pereche de fire rasucite si pentru a fi recuperate cu acuratete. Codarea Manchester are o caracteristica aparte de a tranzita la mijlocul fiecarei celule de bit, o pozitie pozitiva pentru bitul '1' si una negativa pentru '0'. Decodarea se face divizand semnalul codat cu ajutorul unui PLL.

Decodarea Manchester si driver-ul diferential de iesire

Codarea combina ceasul si informatiile pentru transmitator. In codarea Manchester,prima jumatate din celula bitului contine o completare a informatiei, iar cealalta jumatate contine adevarata informatie. Astfel, o tranzitie este intotdeauna garantata in mijlocul celulei de bit.

Codarea si transmiterea datelor incepe cu activatea TxEN; prima tranzitie este intotdeauna pozitiva pentru Tx(-) si negativa pentru Tx(+). In modul IEEE, la terminarea unei transmisii, TxEN devine inactiv si transmite in pereche apropiata spre zero. In modul Ethernet, la terminarea transmisiei, TxEn devine inactiv dar perechea transmisa ramane sus. Incetarea transmisiei poate avea loc la mijlocul celulei de bit daca ultimul bit este 1 si / sau la limita dintre biti daca ultimul este 0. Pentru a face economie de curent, Tx(+) si Tx(-) sunt aduse la 100 mV diferential, in 600 ns dupa ultima transmisie(modul IEEE). Curentul de intoarcere este garantat sa fie mai mic de 1V.

Timer-ul Watchdog

Poate fi activat sau dezactivat de catre semnalul LPBK/WDTD. Acesta incepe sa numere la inceputul tranmisiei. Daca TxEN devine inactiv inainte ca timpul sa expire, numaratoarea este incheiata, iar timer-ul este pregatit pentru urmatoarea transmisie. Daca timpul expira inainte de terminarea transmiterii datelor, transferul va fi incheiat. Acest lucru se face prin dezactivarea drivere-lor de iesire(voltajul diferential de iesire devine zero).

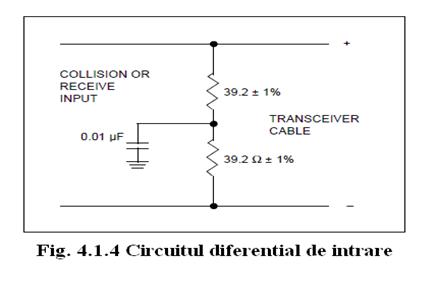

Circuitul Diferential de intrare (Rx+, Rx-, COLL+ si COOL-)

Ca si in Fig 1.4, diferentialele Rx+, Rx-, COLL+ si COOL- sunt la exterior terminate de o pereche de rezistente de 39,2Ω±1%, rezistente inseriate pentru a obtine o impedanta adecvata.

Condensatorul de 0,01µF este legat la masa pentru a avea o impedanta comuna a curentului alternativ pentru cablul receptorului.

Ambele circuite( collision si receptorul) de intrare asigura un sunet intre -140mV si -300mV(valoare maxima). Se pun filtre de sunet pentru cele 2 perechi de intrari pentru a nu obtine semnale false. Perechea de receptie, are o valoare intre 15-30ns, iar cea de colllision intre 10-18ns. Pragul curentului continuu si filtrele de sunet ajuta semnalele de receptie diferentiale mai mici de -140 mV cu o amplitudine apropiata de 15ns(10ns pentru perechea collision) sa fie intotdeauna respinse, iar semnalele mai mari de -300mV si cu amplitudine mai mare de 30ns(18 ns pentru perechea collision) sa fie mereu acceptate.

Decodorul Manchester si circuitul de recuperare a tactului

Filtru pentru date este realizat de circuitul de recuperare a datelor si a ceasului, folosind o tehnica in bucla de examinare a fazei. PLL are rolul de a simplifica datele care se transmit cu o modulatie asimetrica intre 8,25ns si -8.25ns sau, in cel mai rau caz, sa ataseze semnalului de inceput o modulatie asimetrica intre 8,25ns si -8.25ns pe 12 biti. Timpul lui RxC nu va fi niciodata mai mare de 40ns.

Circuitul collision(coliziune)

O coliziune pe cablu Ethernet este sesizata de tranceiver care genereaza un semnal de 10MHz±10% pentru a indica prezenta acesteia.

Bucla locala

In modul loopback(cu bucla locala), datele codate sunt trecute la PLL, nu la semnalele TX+/Tx-. Datele si ceasul recuperate sunt returnate la controlerul Ethernet. In timpul buclei locale, toate circuitele de transmitere/receptie, inclusiv filtrele pentru sunet, sunt testate, cu exceptia driver-ului diferential de iesire si circuitele de intrare ale receptorului care se dezactiveaza.

Descrierea pinilor

Semnalele cip-ului MCC sunt grupate pe urmatoarele categorii :

Sursa de putere

Vcc: +5V

Vss: nul.

X1 si X2 (intrare) : Clock Crystal(ceas din cristal) : oscilator din cristal de 20MHz.

Controlul interfetei

RxC Receive Clock (output) (semnalul de tact receptionat): acest semnal este timpul recuperat de la circuitul de decodare al fazei. Este schimbat cu TxC cand nu este prezenta nici o informatie de intrare din care sa rezulte un timp adevarat.

RxD Receive Data(output) (date de receptie) : semnalele de receptie sunt datele recuperate de la decodarea fazei.

CSN Carrier Sense Signal(output): indica controlerului daca este activitate pe cablul coaxial. Este sustinut cand se primeste informatie sau cand este prezent un semnal de coliziune. Nu mai este sustinut la sfarsitul cadrului sau la sfarsitul coliziunii.

TxC Transmitt Clock(output) (semnal de tact transmis) : este un semnal de 10Mhz, derivat din oscilatorul intern. Acest ceas este intotdeauna activ.

TxD Transmit Data(input) : este informatia de intrare seriala care trebuie transmisa.

TxEN Transmit Enable(input) (transmisie activa) : permite informatiilor sa fie transmise prin cablu. Este sincrona cu TxC. TxEN se activeaza odata cu primul bit de transmisie.

COLL Colllision (output) : indica controler-ului transmisiile a doua sau mai multor statii sau retele de cablu.

Interfata tranceiver-ului

Rx+ si Rx- perechea de receivere diferentiale la intrare (input) : transmite datele codate la 8020. Ultima transmisie este pozitiva pentru a indica sfarsitul cadrului.

COOL+ si COOL- perechea de coliziune diferentiala(input) : este un semnal diferential de 10Mhz±15% de la tranceiver, care indica coliziunea. Ultimul ciclu de transmisie este pozitiv. Acest semnal raspunde cu semnale in apropierea a 5Mhz-11,5MHz.

Tx+ si Tx- perechea de transmitere diferentiala la iesire (output) : transmite datele codate la tranceiver.

Copyright © 2025 - Toate drepturile rezervate