| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Tendinte in tehnologia calculatoarelor

"Legea" lui Moore

1 Tendinte de scalari tehnologice

Proiectarea memoriei ierarhice

UCP construit cu mai multe chip-uri.

Memoria semiconductoare foarte scumpa.

Seturi de instructiuni complexe (densitate de cod buna).

5K 500 K transistoare.

Pipelined UCP pe un singur chip.

Memoria realizabila pe chip

Comanda simpla, cablata.

Seturi de instructiuni simple.

Mici memorii cache pe chip

1 M 64M transistoare, 64b UCP-uri.

Comanda complexa pentru exploatarea paralelismului la nivel de instructiuni.

Pipeline-uri adanci.

Memorii cache pe mai multe nivele.

100 M - 5 B transistoare.

Fire lente, consum de putere, complexitatea proiectarii, intarzierea memoriei, Multiprocesoare si sisteme paralele

Suport si programare pentru paralelism?

<< Teze de doctorat . .>>

4, 8, 16, 32, 64 bit data., sau SIMD

Una dintre limitele adancimii pipeline-lui.

Multithreading temporal - denota modul de lucru care permite ca numai instructiuni dintr-un singur thread sa fie emise la un moment dat.

Multi-threading simultan (SMT) - procesorul superscalar poate emite instructiuni din thread-uri multiple in fiecare ciclu UCP.

Sumar

ASI - componente

Big-Endian, Little-Endian, Aliniere

Moduri de adresare: register, immediate, displacement, register indirect, indexed, direct sau absolut, memory indirect, autoincrement, autodecrement, scaled

Extensie cu semn, cu zero

Tipuri de operatii

Metode de evaluare si utilizare a conditiilor de salt: cod de conditie (registru de flag-uri), registru de conditie (registru de uz general), comparare si bifurcare (comparare si salt conditionat)

Codificare, Formate de instructiuni: lungime fixa, variabila, hibrida

Masini cu 0, 1, 2, 3 adrese, cod programe specifice, nr. adrese de memorie

Instructiune: faze de executie

Arhitecturi Von Neumann, Harvard

CISC vs. RISC

Limitele sistemului Uni-procesor: putere, ILP, performanta, proiectare

Multiprocesoare: taxonomia Flynn: SISD, MISD, SIMD, MIMD

Proiectare: nivele de abstractie: sistem, arhitectura, RTL, logic, electric

Proiectare de sus in jos, comportament, RTL, circuit

Performanta: Latime de banda, productivitate, Intarziere, timp de raspuns

CPU time, CPI, IPC

Legea lui Amdahl: Castig = 1 / [ ( 1- fx ) + fx/Sx ]

Constrangeri de Cost, Putere (dinamica, statica)

Legea lui Moore

Tendinte tehnologice si arhitectrale: CISC, comanda micro-programata; RISC, Pipeline, cache pe chip; ILP complex, pipeline adanc, speculatii, cache multi nivel; Multiprocesoare

Paralelisme: DLP, ILP, TLP, multi-threading, SMT

Digital components

CMOS transistor implementations of some basic logic gates: (a) nMOS transistor, (b) pMOS transistor, (c) inverter, (d) NAND gate, (e) NOR gate.

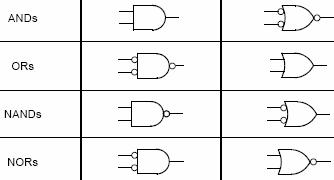

Basic logic gates

![]()

![]()

![]()

Positive - Negative logic Equivalent XOR gates

3-state buffers Tri-state Buffer

3-state buffer 3-state buffer

Parity generator Even parity notation

Combinational components.

Sequential components.

Encoders

A 2n-to-n binary encoder

Decoders

2:4 decoder implementation

Priority encoder Schematic Truth table

Multiplexers

2:1 multiplexer 2x2 crossbar - any input to any output

4:1 multiplexer implementations: (a) twolevel logic, (b) tristates, 8 bit 2:1 MUX

(c) hierarchical; (d) symbol

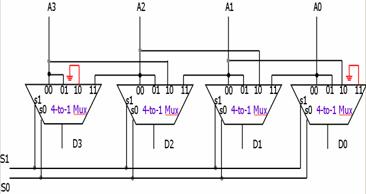

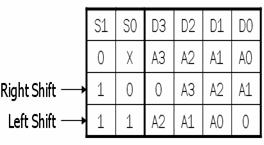

Shifter

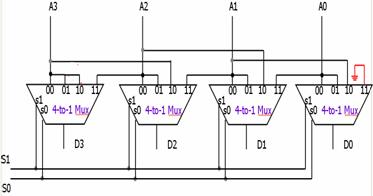

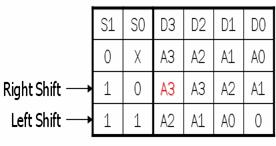

4-bit Logical Shifter using 4-to-1 Mux

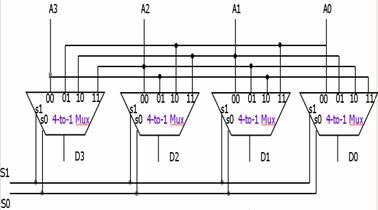

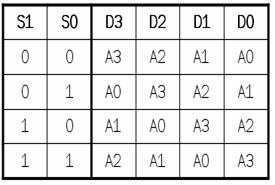

4-bit Arithmetic Shifter w/ 4-to-1 Mux

Rotator- right 0, 1, 2, 3

8-bit logical right shifter

8-bit right rotator

Logical shift; Arithmetical shift

Shift and rotate examples for A = a7a6a5a4a3a2a1a0 and B = 3.

Full Adder

Truth

table. Solutions; v1 v2 Ci+1

= xiyi + Ci(xi![]() yi) Si = xi

yi) Si = xi ![]() yi

yi ![]() Ci

Ci

ripple-carry adder. Two's Complement Subtractor

Zero, Sign, Overflow detection Saturating Adders -DSP

provide the most positive or the most negative value

Two's complement adder/subtractor with overflow detection. MUX input

n-bit ALU

Logic unit S1 S0

Arithmetic unit

Combinational Multiplier

Decimal Binary Implementation

Multiplication of binary numbers.

An array multiplier circuit.

adding 8 numbers using an adder tree. A registered multiplier circuit.

An array multiplier implemented using n-bit adders. Each n-bit adder adds a shifted version of A for a given row and the partial sum of the row above.

Copyright © 2025 - Toate drepturile rezervate