| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Porturilr I / O - Familia PIC 16F8x

Familia PIC 16F8x are doua porturi I/O:

PORTA cu 5 liniii I/O;

PORTB.cu 7 liniii I/O;

Fiecare pin I/O poate fi gestionat in mod individual. Orice pin poate fi configurat ca intrare sau ca iesire.

Unii pini sunt inzestrati cu mai multe functii alternative.

1 Portul I/O PORTA si registrul de configurare TRISA

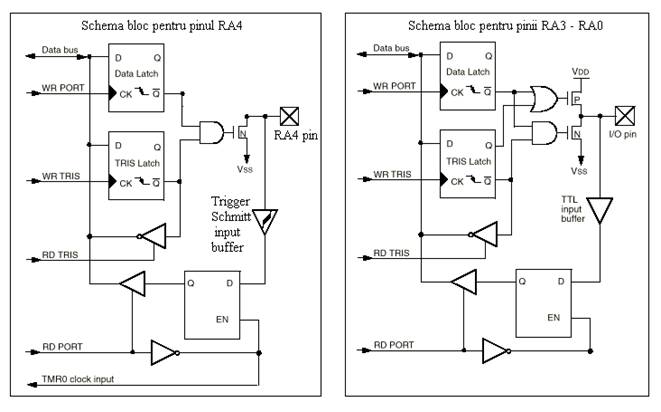

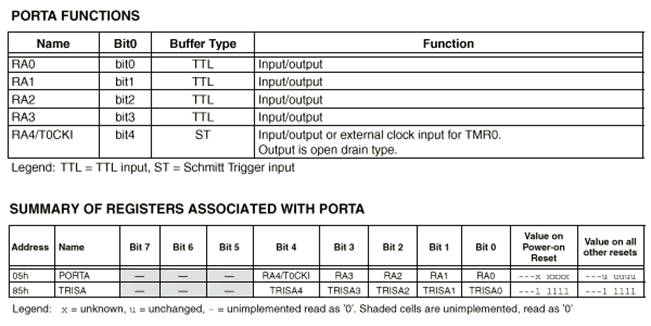

PORTA are 5 linii I/O: RA4, RA3, RA2, RA1, RA0.

RA4 este prevazut cu: buffer Trigger Schmitt pe intrare

open drain pe iesire.

RA3 - RA0 sunt prevazute cu: buffer TTL pe intrare;

CMOS driver pe iesire;

TRISA are 5 biti: TRISA4, TRISA3, TRISA2, TRISA1, TRISA0 ce corespund bitilor registrului PORTA. Cu ajutorul acestor biti se poate configura directionalitatea pinilor portului PORTA.

Astfel, avem:

TRISAy = 1 => pinul PORTAy este configurat ca intrare, adica driverul de pe iesire este fortat in Hz si se permite citirea nivelului logic direct de pe pinul corespunzator;

TRISAy = 0 => pinul PORTAy este configurat ca iesire, adica pe iesire se permite aplicarea continutului latch-ului de date corespunzator;

Observatie: Citirea portului PORTA consta in citirea starilor direct de pe pini. Inscrierea portului PORTA consta in inscrierea latch-ului de date corespunzator portului.

Observatie: Toate operatiile de inscriere sunt de tipul "read-modify-write".Deci o operatie de inscriere a portului PORTA se realizeaza parcurgindu-se urmatoarele etape:

sunt citite starile logice direct de pe pinii portului;

valoarea citita anterior este modificata;

valoarea obtinuta anterior este inscrisa in latch-ul de date al portului.

Observatie: Pinul RA4 este multiplexat cu intrarea pentru timer-ul TMR0.

Exemplu: Initializarea portului PORTA:

BCF STATUS, RP0 ; select. Bank0 pentru a se putea avea acces la PORTA

CLRF PORTA ; sterge latch-ul de date al portului PORTA

BSF STATUS, RP0 ; select. Bank1 pentru a se putea avea acces la TRISA

MOVLW 0x15 ; incarca constanta literala in W

MOVWF TRISA ; incarca in registrul de configurare valoarea 10101, ceea ce

; inseamna ca:

pinii RA4, RA2, RA0 sunt configurati ca intrari

; pinii RA3, RA1 sunt configurati ca iesiri

1 Portul I/O PORTB si registrul de configurare TRISB

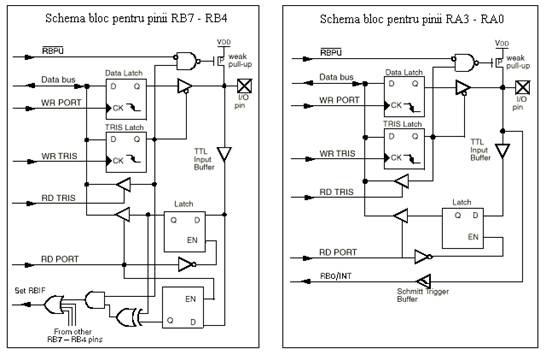

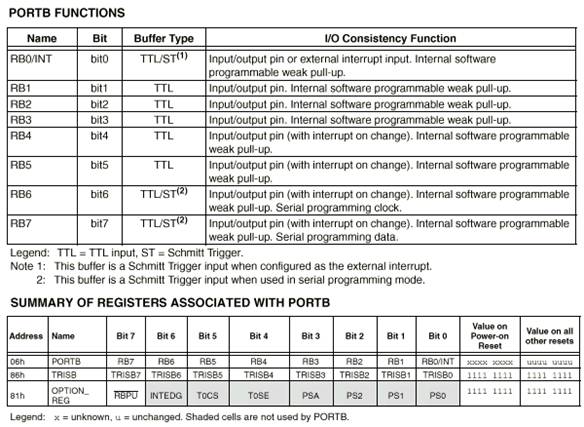

PORTB are 8 linii I/O: RB7, RB6, RB5, RB4, RB3, RB2, RB1, RB0.

RB7 -RB4 sunt prevazute cu: buffer TTL pe intrare;

weak pull-up intern pe intrare;

CMOS driver pe iesire;

posibilitatea de a genera o cerere de intrerupere la detectarea

schimbarii starii logice a semnalului de pe intrare;

RA3 - RA0 sunt prevazute cu: buffer TTL pe intrare;

weak pull-up intern pe intrare;

CMOS driver pe iesire;

Bitul RBPU ( bitul 7 ) din registrul OPTION_REG este singurul bit folosit pentru activarea / dezactivarea tuturor pull-up-urilor interne ale portului PORTB. Astfel, avem:

RBPU = 1 => toate pull-up-urile de pe pinii portului PORTB sunt inactivate;

RBPU = 0 => toate pull-up-urile de pe pinii de intrare ai portului PORTB sunt activate;

Observatie: Pentru a fi activat pull-up-ul intern corespunzator unui pin de pe portul PORTB trebuie indeplinite urmatoarele doua conditii:

bitul RPBU = 0

pinul respectiv este configurat ca intrare ( bitul coresp. din TRISB este "1" );

Observatie: Pull-up-ul unui pin al portului PORTB este automat dezactivat in momentul in care acesta este configurat ca iesire.

Observatie: La Power-on Reset toate pull-up-urilor interne ale portului PORTB sunt inactivate.

TRISB are 8 biti: TRIS8 TRISA0 ce corespund bitilor registrului PORTB. Cu ajutorul acestor biti se poate configura directionalitatea pinilor portului PORTB. Astfel, avem:

TRISBy = 1 => pinul PORTBy este configurat ca intrare, adica driverul de pe iesire este fortat in Hz si se permite citirea nivelului logic direct de pe pinul corespunzator;

TRISBy = 0 => pinul PORTBy este configurat ca iesire, adica pe iesire se permite aplicarea continutului latch-ului de date corespunzator;

Observatie: Citirea portului PORTB consta in citirea starilor direct de pe pini. Inscrierea portului PORTB consta in inscrierea latch-ului de date corespunzator portului.

Pinii RB7, RB6, RB5 si RB4 ai portului PORTB sunt inzestrati cu posibilitatea de a genera o cerere de intrerupere la detectarea schimbarii nivelului logic. Trebuie subliniat ca dintre pinii RB7 - RB4 numai cei configurati ca intrari pot cauza generarea unei cereri de intrerupere in momentul detectarii unei schimbari de nivel logic pe intrare.

Observatie: Acest mod de generare a unei intreruperi se explica astfel: starile logice curente ale pinilor configurati ca intrari sunt COMPARATE cu starile lor logice imediat anterioare care au fost retinute, pe parcursul ultimei citiri a portului PORTB, in latch-uri dedicate pentru aceasta.

Observatie: In figura de mai jos se prezinta schema bloc pentru unul dintre pinii RB7 - RB4 si se poate vedea cum este realizata compararea ( cu porti logice XOR ) pentru fiecare pin in parte si cum cele 4 iesiri ale portilor XOR sunt aplicate prin intermediul unor porti AND de validare pe intrarile unei porti OR a carei iesire controleaza starea logica a flag-ului RBIF din registrul INTCON.

Observatie: Daca cel putin unul dintre pinii RB7 -RB4 care este configurat ca intrare a suferit o

schimbare de nivel logic => RBIF = 1 => cerere de intrerupere.

Observatie: O cerere de intrerupere de acest tip poate reactiva intreg microcontrolerul daca acesta era in modul de functionare SLEEP.

Observatie: Programatorul poate reseta ( achita ) o cerere de intrerupere de acest tip la sfirsitul rutinei de deservire in urmatorul mod, care necesita 2 etape:

prin citirea ( sau inscrierea ) portului PORTB; aceasta operatie are ca rezultat anularea

nepotrivirii ( nu va exista nici o poarta XOR a carei iesire sa fie in '1' );

resetarea bitului RBIF din cadrul registrului INTCON;

Observatie: O conditie de nepotrivire poate sa dispara numai in 2 moduri:

extern: cind starile logice ale semnalelor externe ce se aplica pe pinii RB7 - RB4

( configurati ca intrari ) revin de la sine la starile ' de potrivire' ( apare nepotrivire doar pe unul din fronturi );

intern: cind se executa o operatie de citire asupra portului PORTB - moment in care starile logice curente ale semnalelor externe ce se aplica pe pinii RB7 - RB4 ( configurati ca intrari ) sunt retinute in latch-urile dedicate pentru aceasta si al caror continut este folosit in operatia de comparare ( apare nepotrivire pe ambele fronturi )

Observatie: Flag-ul RBIF din registrul INTCON nu poate fi resetat decit dupa ce conditia de nepotrivire dispare.

Observatie: Tinind cont de:

posibilitatea de generare a intreruperilor prin intermediul pinilor RB7 - RB4;

posibilitatea de activare / dezactivare prin soft a pull-up-urilor interne pentru pinii RB7 - RB4;

se poate realiza o interfatare facila cu un key-pad si face posibila detectia pe key-depression.

Observatie: Pentru a putea fi recunoscuta ( detectata ) o schimbare a nivelului logic de pe unul din pinii

RB7 - RB4, care este configurat ca intrare, trebuie ca durata impulsului sa fie de cel putin TCY ( 4 / fosc ).

Observatie: Folosirea portului PORTB ca sursa de intreruperi ( RB7 - RB4 ) este recomandata pentru operatra de tipul 'wake-up on key-depression' si se recomanda ca in acest caz portul PORTB sa nu mai fie folosit si la altceva.

Observatie: Este contraindicata folosirea polling-ului pentru portul PORTB cind acesta este folosit ca sursa de intreruperi.

Exemplu: Initializarea portului PORTB:

BCF STATUS, RP0 ; selectare Bank0

CLRF PORTB ; resetarea latch-ului de date de pe iesire

BSF STATUS, RP0 ; selectare Bank1

MOVLW 0xA5 ; incarca in W const. de init. pentru registrul de configurare TRISB

MOVWF TRISB ; incarca in TRISB constanta 1010 0101 ceea ce inseamna ca:

; RB7, RB5, RB2 si RB0 sunt configurate ca intrari;

; RB6, RB4, RB3 si RB1 sunt configurate ca iesiri;

3. Consideratii cu privire la programarea I/O

3.1. Porturi I / O bidirectionale

Orice instructiune de inscriere intr-un port echivaleaza cu:

o operatie de citire din portul respectiv;

modificarea valorii citite anterior;

o operatie de inscriere a valorii obtinute la etapa anterioara;

De exemplu pe parcursul executiei instructiunilor BCF si BSF mai intii se citeste valoarea din registru, aceasta este modificata si in final este reinscrisa in apoi in registru.

In general in cazul acestor tipuri de instructiuni trebuie avut grija cind sunt sunt folosite pentru portui care au definiti pini si de iesire si de intrare.

De exemplu daca se foloseste instructiunea BSF pentru modificarea bitului 5 din cadrul portului PORTB, atunci in prima faza se citsec toti cei 8 pini ai portului, se modifica doar bitul 5 si in final se reinscriu toti cei 8 biti.in latch-urile de date corespunzatoare. Daca un alt bit al portului PORTB, de exemplu bitul 0, este folosit ca bit cu functiuni bidirectionale si in primul moment este configurat ca intrare, nivelul logic prezent pe pinul corespunzator va fi citit si apoi va fi suprascris in latch-ul de date corespunzator, peste valoarea anterioara, lucru care nu deranjeaza cu nimic atita timp cit bitul 0 al portului PORTB ramine configurat ca intrare. Totusi, daca mai tirziu bitul 0 este configurat ca iesire, va apare o problema in sensul ca valoarea latch-ului de date de pe iesire nu poate fi cunoscuta.

Doua reguli trebuie cunoscute si intelese:

citirea unui port I/O se realizeaza numai prin citirea nivelelor logice direct de la pini;

inscrierea unei valori intr-un port I/.O se face in latch-ul de date de pe iesire;

Cind se utilizeaza instructiuni de tipul read-modify-write-( de exemplu BCF, BSF, . etc ) pentru un port, in prima faza se citeste valoarea intregului port ( se citesc nivelele logice direct de pe pinii portului ), apoi se realizeaza operatia dorita ( modificarea valorii citite de pe port ), dupa care, in final, valoarea modificata este reinscrisa inapoi in port ( in latch-ul de date corespunzator portului ).

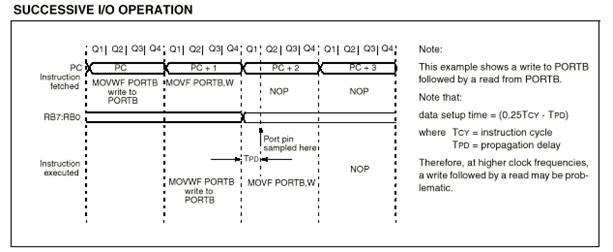

2. Operatii succesive pe portui I / O

Observatie: Operatiile de inscriere in porturile I / O au loc la sfirsitul ciclului instructiune.

Observatie: Operatiile de citire la la porturile I / O au loc la inceputul ciclului instructiune.

Tinind cont de aceste doua observatii importante, si tinind cont de viteza mare de lucru a dispozitivelor din familia PIC16F8x ( 10 MHz ), in special in cazul unei succesiuni de operatii de inscriere si citire asupra aceluiasi port I / O, se impune intercalarea de instructiuni NOP intre cele doua instructiuni I / O. Astfel, intre cele doua instructiuni se lasa un ragaz care sa permita stabilizarea nivelelor logice pe pinii portului.

Exemplu: Instructiuni de tipul "read-modify-write"

Se presupune ca portul PORTB are urmatoarele setari:

PORTB<7:4> intrari;

PORTB<3:0> iesiri;

pinii PORTB<7,6> au pull-up-uri externe si nu sunt conectati la alte ciruite externe;

PORT latch PORT pins

BCF STATUS, RP0 ??pp pppp 11pp pppp

MOVLW 0XC0 ??pp pppp 11pp pppp

IORWF PORTB, 1 11pp pppp 11pp pppp

BCF PORTB, 7 01pp pppp 11pp pppp

BCF PORTB, 6 10pp pppp 11pp pppp

BSF STATUS, RP0 10pp pppp 11pp pppp

BCF TRISB, 7 10pp pppp 11pp pppp

BCF TRISB, 6 10pp pppp 10pp pppp

In linia 3 se seteaza in "1" bitii 7 si 6 ai latch-ului de date de pe PORTB.

In linia 4 se reseteaza bitul 7 al latch-ului de date de pe PORTB.

In linia 5 se reseteaza bitul 6 al latch-ului de date de pe PORTB dar se observa ca bitul 7 al latch-

ului de date de pe PORTB revine inapoi in "1" ( fara a se dori aceasta ) datorita nivelului logic al pinului corespunzator care este tot timpul in "1".

In linia 6 se selecteaza Bank1.

In linia 7 este configurat ca iesire bitul 7 al portului PORTB si se observa ca nivelul logic al

pinului corespunzator este acelasi cu al bitului 7 din latch-ul de date, adica"1".

In linia 8 este configurat ca iesire bitul 6 al portului PORTB si se observa ca nivelul logic al

pinului corespunzator este acelasi cu al bitului 6 din latch-ul de date, adica "0".

Copyright © 2025 - Toate drepturile rezervate