| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Organizarea Memoriei - PIC16F8x

PIC16F8x are 2 tipuri diferite de memorie:

memoria program care poate fi de tipul Flash sau ROM;

memoria de date care este formata, la rindul sau, din 2 zone:

mem. de date de tipul SRAM ( volatila );

mem. de date de tipul EEPROM ( nevolatila );

Astfel, exista doua magistrale de memorie distincte: magistrala de memorie program ( 14 biti ) si magistrala de memorie de date ( 8 biti ). In plus, fiecare tip de memorie are propria magistrala de adrese, permitandu-se transferul. de date de la memoria program la memoria de date.

1) Memoria program poate fi de tipul Flash sau ROM, are dimensiunea de 512 sau 1024 de cuvinte cu lungimea de 14 biti si este destinata stocarii codului executabil.

2) Memoria de date de tipul SRAM este formata din:

File Registers - 36 sau 68 de octeti de memorie de uz general;

Special Function Registers ( SFR ) - 2 x 12 octeti rezervati; cu ajutorul lor se

poate controla functionarea nucleului si a perifericelor incorporate;

3) Memoria de date de tipul EEPROM are dimensiunea de 68 de octeti si este formata din locatii de memorie de uz general care pot fi accesate in vederea inscrierii sau citirii numai prin intermediul registrului EEDATA care trebuie incarcat cu adresa locatiei dorite ( domeniul de adrese 0x00 - 0x3F ).

1. Organizarea memoriei program

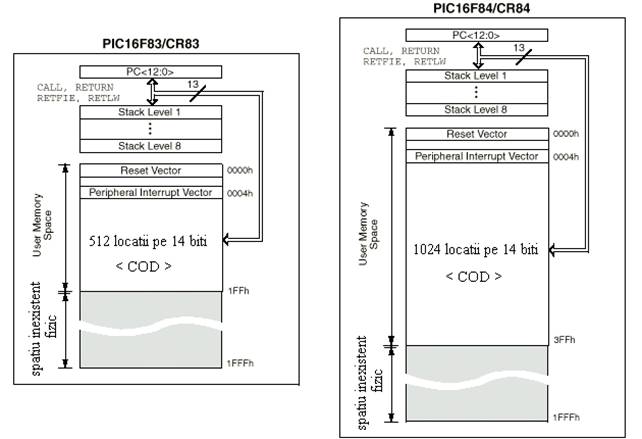

PIC16Fxx este prevazut cu un registru PC ( Program Counter ) cu lungimea de 13 biti, care poate sa adreseze pina la maximum 8K locatii de 14 biti din spatiul de memorie de cod.

Totusi, fizic nu este implementata toata aceasta cantitate de memorie program. Astfel, avem:

PIC16F83 si PIC 16CR83 are implementata numai zona primelor 512 locatii de cod

( domeniul de adrese 0x000 - 0x1FF );

PIC16F84 si PIC 16CR8 are implementata numai zona primelor 1024 locatii de cod;

( domeniul de adrese 0x000 - 0x3FF );

Observatie: Incercarea de a accesa o locatie de memorie de cod a carei adresa depaseste adresa maxima fizic implementata are ca rezultat un "warp-around"; de exemplu pentru PIC16F84 se incearca adresarea

locatiilor: 0x0020 va fi accesata locatia cu adresa 0x0020

0x0320 va fi accesata locatia cu adresa 0x0320

0x0420 va fi accesata locatia cu adresa 0x0020

0x0520 va fi accesata locatia cu adresa 0x0120

0xC120 va fi accesata locatia cu adresa 0x0120

Observatie: Tabela vectorilor de intrerupere este:

0x0000 - vectorul care indica catre adresa de inceput a rutinei de reset;

0x0004 - vectorul care indica catre adresa de inceput a rutinei comune de tratare a tuturor

surselor de cerei de intreruperi;

Figurile 4-1 si 4-2: Harta memoriei program pentru PIC16F8x

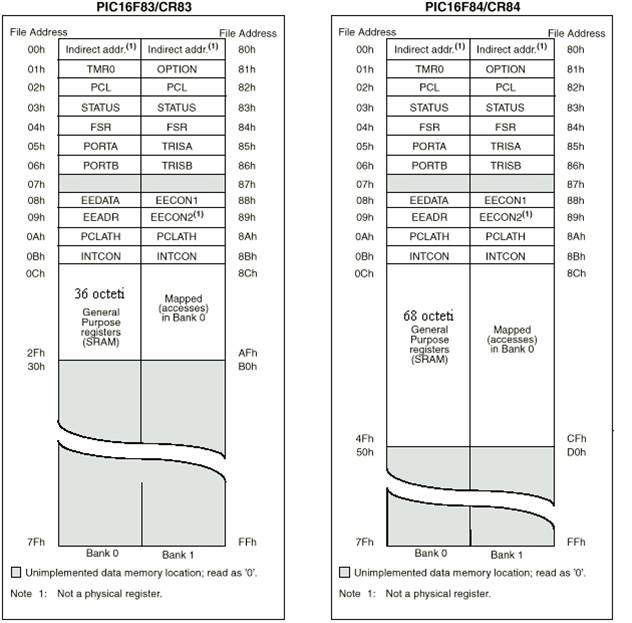

2. Organizarea memoriei de date

Cum am mai spus, memoria de date de tip SRAM este formata din doua zone avind functii diferite:

zona registrilor cu functii speciale ( Special Function Rregister-s );

zona registrilor de uz general ( General Purpose Register-s );

In plus, memoria de date de tipul SRAM este organizata si poate fi gestionata sub forma de bank-uri. In cazul familiei PIC16F8x exista doar 2 bank-uri: Bank1 si Bank0. Aceasta forma de organizare in general necesita folosirea bitilor RP1, RP0 de selectie a bank-ului curent, biti ce sunt localizati in SFR-ul STATUS.

In cazul familiei PIC16F8x trebuie observat ca zonele registrilor de uz general din cele doua

bank-uri se suprapun ( de exemplu prin adresele 0x0C si 0x8C se acceseaza acelasi registru de uz general )

ceea ce inseamna ca bitii RP1 si RP0 nu au nici un rol in selectia GPR-urilor.

Se observa ca NU acelasi lucru se intimpla cu zonele registrilor cu functii speciale, caz in care unele dintre acestea sunt selectate cu ajutorul bitilor RP1 si RP0 ( de fapt intervine numai RP0 )

( de exemplu adresa 0x01 adreseaza registrul TMR0 iar adresa 0x81 adreseaza registrul OPTION_REG, dar in acelasi timp adresele 0x02 si 0x82 adreseaza acelasi registru PCL ).

Figurile 4-1 si 4-2 Harta memoriei de date de tipul SRAM pentru PIC16F8x

Observatie: Instructiunile urmatoare pot transfera continutul oricaruiregistru in W si invers:

MOVWF f ( muta data din W in registrul de la adresa [ [ Rp1 RP0 ] [ f ] ] )

MOVF f, d ( daca d=0 => muta data din registru de la adresa [ [ Rp1 RP0 ] [ f ] ] in reg. W )

( daca d=1 => muta data din registru de la adresa [ [ Rp1 RP0 ] [ f ] ] in el insusi )

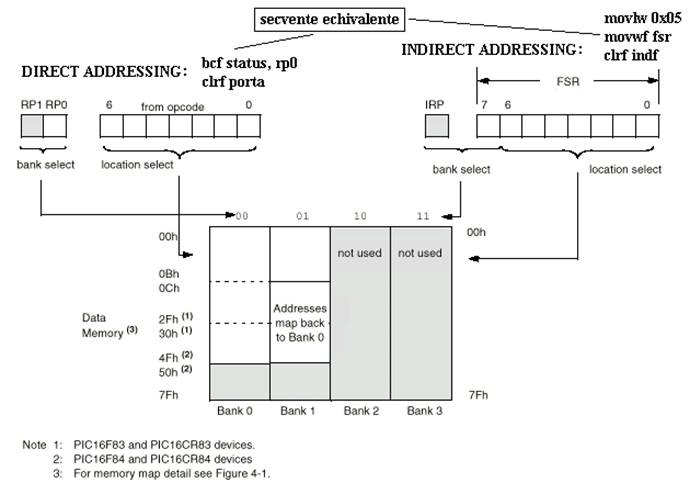

Observatie: Orice locatie din memoria de date de tipul SRAM poate fi accesata in doua moduri:

prin adresare INDIRECTA: se face uz de registrul FSR ( File Select Register ) care este un veritabil pointer pe 8 biti si care contine adresa registrului sursa sau destinatie dorit, iar operandul folosit in instructiune este registrul INDF ( fizic acesta nu exista );.

prin adresare DIRECTA: operandul folosit in instructiune este chiar registrul sursa sau destinatie;

Observatie: Deci memoria de date de tipul SRAM este impartita in doua bank-uri care contin, fiecare, atit SFR-uri cit si GPR-uri. Selectarea unuia dintre cele doua bank-uri, la un moment dat, se realizeaza cu ajutorul bitilor RP1 si RP0 din cadrul registrului STATUS.

In cazul PIC16F8x avem: totdeauna RP1 = 0 ( nu intervine in selectia bank-urilor )

RP0 = 0 => selectare Bank0

RP0 = 1 => selectare Bank1

Observatie: Fiecare Bank, teoretic, poate contine pina la 0x7F ( 128 biti ). In cazul PIC16F8x avem:

primii 12 octeti din fiecare Bank sunt rezervati pentru SFR-uri,

urmatorii 36 sau 68 de octeti reprezinta GPR-uri,

restul pina la 0x07F nu sunt implementati fizic .

2.1. General Purpose Registers - GPR ( File Registers )

Acesti registri formeaza de fapt spatiul de memorie de date de uz general ( 36 sau 68 de locatii pe 8 biti ). Fiecare GPR poate fi accesat fie folosind adresarea directa ( folosind adresa absoluta ) fie folosind adresarea indirecta ( folosind FSR ).

Observatie: Adresele GPR-urilor continute de Bank1 sunt mapate la aceeleasi adrese ale GPR-urilor continute de Bank0, adica la doua adrese diferite se gaseste acelai GPR. Ca o exemplificare, la adresele 0x00C si 0x08C se gaseste de fapt acelasi GPR.

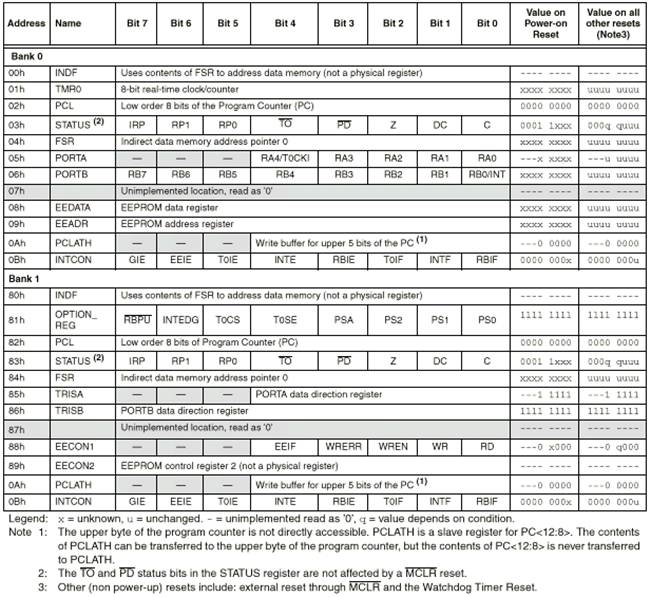

2.2. Special Function Registers - SFR

SFR-urile sunt mapate in memoria de date de tip SRAM si sunt utilizate pentru controlul CPU-ului si a perifericelor incorporate.

Din Figurile 4-1 si 4-2 se observa ca exista SFR-uri specifice pentru fiecare Blok in parte.

Figura 4-1 Prezentarea sumara a SFR-urilor

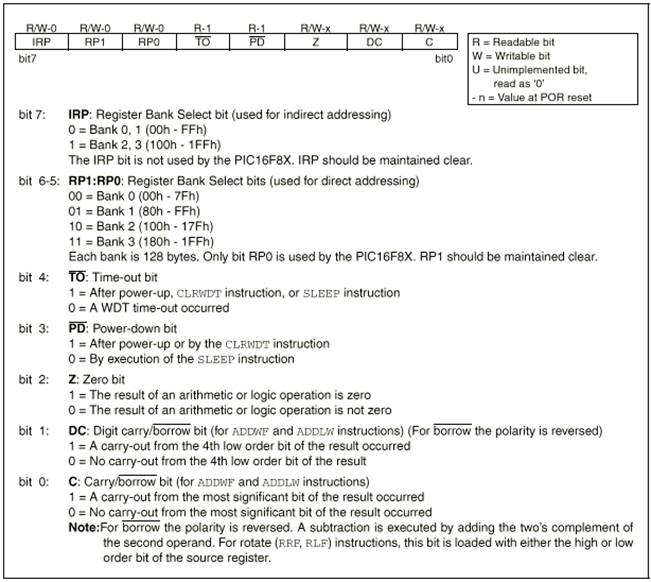

2.2.1. Status Register

Registrul STATUS contine flag-uri ce indica:

starea unor rezultate aritmetice

starea de RESET

bitii de selectare a Bank-ului curent

Acest registru poate fi folosit ca destinatie pentru orice instructiune. Daca este destinatie pentru o instructiune care afecteaza flag-urile Z, DC sau C, atunci este dezactivata inscrierea acestor biti. Acesti biti sunt setati sau resetati in concordanta cu starea dispozitivului logic. In plus bitii /TO si /PD nu pot fi decit cititi. De aceea rezultatul unei instructiuni care are ca destinatie registrul STATUS poate sa fie incorect la un moment dat.

Exemplu:

CLRF STATUS ; sterge cei mai semnificativi 3 biti si seteaza flag-ul Z

; dupa executia acestei instructiuni continutul registrului STATUS este:

; 000u u1uu unde: u = neschimbat

Observatie: Numai instructiunile BCF, BSF, SWAPF si MOVWF trebuie utilizate pentru modificarea continutului registrului STATUS deoarece aceste instructiuni nu afecteaza nici un flag de stare pe timpul executiei lor.

Observatie: Bitii IRP si RP1 nu sunt utilizati de catre PIC16F8x si trebuie fortati in "0". In plus, utilizarea acestor biti in scopuri generale de citire / inscriere nu este recomandata deoarece s-ar putea ca programul aplicatie sa nu mai fie compatibil cu noile produse compatibile pe verticala.

Observatie: Daca registrul STATUS este destinatie pentru o instructiune care afecteaza flag-urile Z, DC sau C, atunci este dezactivata inscrierea acestor biti. Acesti biti sunt setati sau resetati in concordanta cu starea dispozitivului logic.

Figura 4-1 Status Register < adresa: 0x003 sau 0x083 >

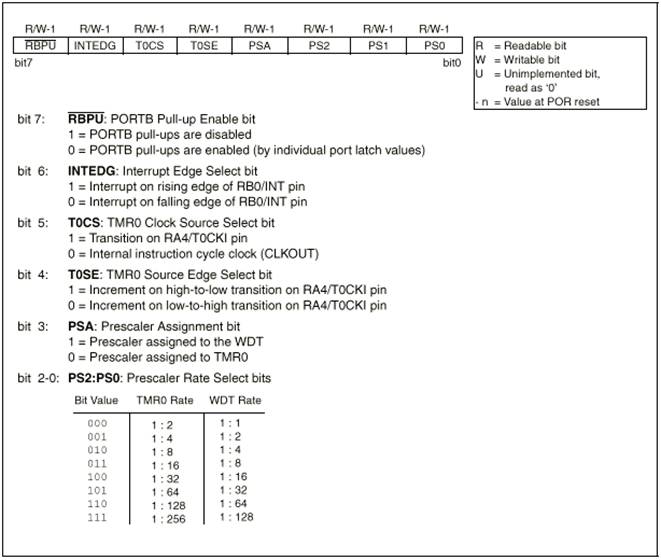

2.2.2. Option_Reg Register

Acest registru poate fi atit citit cit si inscris si contine diferiti biti de configurare pentru TMR0 / WDT prescaler, intreruperi externe, TMR0, etc .

Observatie: Cind prescalerul este asignat pentru WDT ( PSA = 1 ) , atunci TMR0 are un raport de 1:1 pentru prescaler.

Figura 4-1 Option_Reg Register < adresa: 0x081 >

2.2.2. Option_Reg Register

Acest registru poate fi atit inscris cit si citit si contine un set de biti de comanda si control pentru:

prescalerul pentru TMR0 / WDT ;

intreruperea externa INT;

timerul TMR0

rezistentele de pull-up pentro PORTB;

Figura 4-1 Option_Reg Register < adresa: 0x081 >

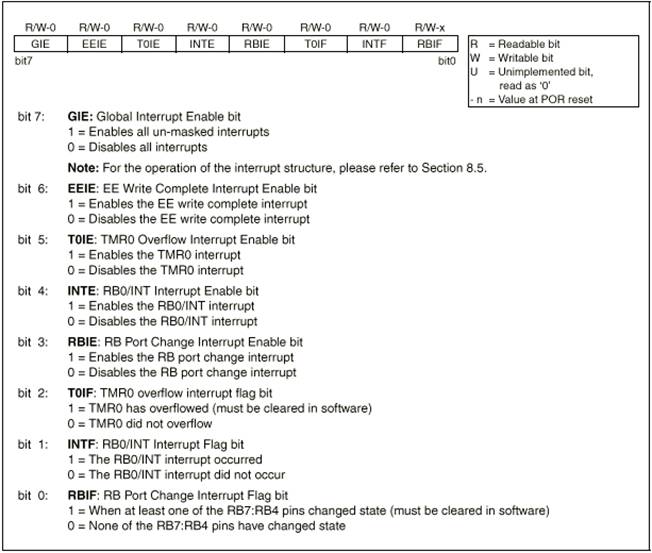

2.2.3. Intcon Register

Acest registru poate fi atit citit cit si inscris si contine 4 biti pentru configurarea sistemului de intreruperi si 3 flag-uri necesare in gestionarea sistemului de intreruperi.

Observatie: Un flag-de intreruperi este setate cind a apare o cerere corespunzatoare de intrerupere si cind bitul corespunzator de validare este setat.

Figura 4-1 Intcon Register < adresa: 0x00B sau 0x08B >

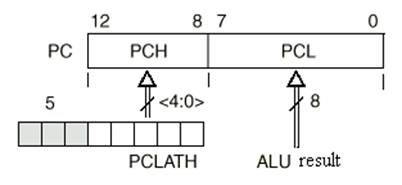

3. Program Counter: PCL si PCLATCH

Program Counter ( PC ) este un registru cu lungimea de 13 biti. Acesta este impartit in doua parti inegale: PCLATH si PCL.

Cei mai putin semnificativi 8 biti ai registrului PC pot fi accesati direct, fiind continuti de PCL care este un registru ce poate fi citit sau inscris in mod direct.

Cei mai semnificativi 5 biti ai registrului PC nu pot fi cititi sau inscrisi in mod direct, acestia fiind furnizati prin intermediul registrului PCLATH care este un latch. Continutul lui PCLATH este transferat catre cei mai semnificativi 5 biti ai lui PC numai cind PC este incarcat cu o noua valoare. Aceasta situatie apare la executia unor instructiuni de tipul CALL, GOTO sau in cazul inscriereilor directe in PCL.

Figura . . .. Incarcarea registrului PC ( Program Counter ) in cazul cind

se face o inscriere asupra registrului PCL

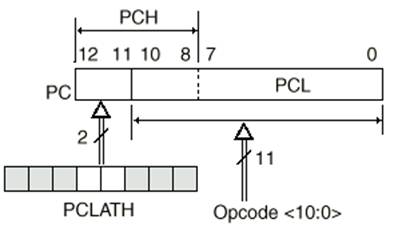

Figura . . . . Incarcarea registrului PC ( Program Counter ) in cazul

executiei unei instructiuni de tipul GOTO sau CALL

Observatie: Familia PIC16F8x nu utilizeaza bitii 3 si 4 ai registrului PCLATH.

3.1. Metoda de calculare GOTO

Metoda de calculare GOTO se realizeaza adaugind un offset la registrul PC, adica este echivalenta cu instructiunea "ADDWF PCL, 1".

De aceea, cind se realizeaza un tabel de citire folosind "metoda de calculare GOTO", trebuie avut grija sa se verifice daca zona ocupata de tabel nu depaseste limita maxima permisa de dimensiunea regis-truluin PCL ( 8 biti => limitarea se refera la blok-uri de 256 cuvinte de mem. program ).

3.2. Paginarea menoriei de cod

PIC16F83 si PIC16CR83 au cite 512 cuvinte de memorie program.

PIC16F84 si PIC16CR84 au cite 1024 cuvinte de memorie program.

Instructiunile CALL si GOTO au un domeniu de 11 biti de adresa, adica permit salturi in interiorul unor pagini de memorie program cu dimensiunea de 2048 locatii.

Pentru viitorii membri ai familiei PIC16F8x, care vor fi inzestrati cu memorie program de dimensiune mai mare, exista doi biti ce sunt destinati selectiei paginii curente de memorie program.

Acestia sunt bitii 3 si 4 ai registrului PCLATH. Astfel, inaintea oricarei instructiuni CALL sau GOTO, programatorul trebuie sa programeze corespunzator acesti biti pentru a selecta pagina de cod corecta.

La executia instructiunii CALL ( sau la detectarea unei intreruperi ), intregul registru PC

( care are lungimea de13 biti ) este salvat pe stiva.

La executia unor instructiuni de revenire, RETURN, RETLW sau RETFIE, intregul continut al registrului PC este refacut. De aceea nu este nevoie de o gestionare speciala pentru bitii 3 si 4 din PCLATH.

Observatie: Dispozitivele din familia PIC16F8x nu utilizeaza in nici un fel bitii 3 si 4 ai registrului PCLATH deoarece nu au nici macar 2k de memorie program.

Observatie: Utilizarea bitilor 3 si 4 ai registrului PCLATH ca biti de uz general ( pot fi cititi sau inscrisi )

NU este recomandata deoarece nu se asigura portabilitatea programelor si pe dispozitivele mai noi ale familiei PIC16F8x.

3.3. Stiva

Dispozitivele din familia PIC16F8x sunt inzestrate cu o stiva avind urmatoarele caracteristici:

este gestionata hard, neexistind in setul de instructiuni "PUSH" sau "POP";

permite pina la 8 nivele de imbricare;

este mapata intr-o zona speciala de memorie ce nu are nimic comun cu memoria de date;

indicatorul de stiva nu poate fi nici citit nici inscris;

In mod automat, in cazul detectarii unei cereri de intrerupere sau in cazul executiei unei instructiuni CALL, intregul continut ( pe 13 biti ) al registrului PC ( Program Counter ) este salvat pe stiva ( stiva este implementata intr-o zona speciala de ram ce nu este accesibila programatorului ).

In mod automat, in cazul executiei unei instructiuni de "intoarcere" de tipul RETURN, RETLW sau RETFIE , intregul continut ( pe 13 biti ) al registrului PC ( Program Counter ) este refacut de pe stiva

Observatie: Familia PIC16F8x poseda un set de instructiuni care NU contine instructiuni explicite de gestionare a stivei, cum sunt "PUSH" si "POP", deoarece stiva este gestionata hard.

Observatie: Stiva se comporta asemeni unui buffer circular. Astfel, daca s-au salvat pe stiva 8 valoari succesive ale continutului registrului PC ( s-a atins numarul maxim de imbricare ) si daca se forteaza

acest nivel maxim de imbricare prin salvarea unei a 9-a valori a reg. PC, atunci noua valoare va fi supra-scrisa peste locatia din stiva unde se salvase prima valoare . e.t.c.. Pe de alta parte, daca din stiva se extrag mai multe valori decit s-au salvat, atunci extragerile suplimentare din stiva vor avea aceeasi valoare cu valoarea primei inscrieri.

Observatie: Nu exista flag-uri care sa indice overflow stiva si nici flag-uri care sa indice underflow stiva.

Orice locatie din memoria de date de tipul SRAM poate fi accesata in doua moduri:

prin adresare INDIRECTA: se face uz de registrele FSR ( File Select Register ) si INDF ( care nu exista fizic ); FSR este un veritabil pointer pe 8 biti si contine adresa registrului sursa sau destinatie dorit, iar operandul folosit in instructiune este registrul INDF;.

prin adresare DIRECTA: operandul folosit in instructiune este chiar registrul sursa sau destinatie din cadrul bank-ul curent selectat;

Figura . . . . Modurile de adresare pentru PIC16F8x

Exemplu:

movlw 0x10 ; incarca in W constanta literala 0x10 -

movwf 0x05 ; incarca in locatia 0x05 valoarea 0x10 - adresare directa

movlw 0x05 ; incarca in W constanta literala 0x05

movwf FSR ; incarca in FSR valoarea 0x05 - adresare directa

incf INDF, 1 ; increm. continutul locatiei pointata de FSR - adresare indirecta

movf INDF, 0 ; incarca in W valoarea pointata de FSR - adresare indirecta

movf, 0x05 ; increm. continutul locatiei de la adresa 0x05 - adresare directa

Exemplu: Resetarea unei zone contigue de memorie 0x20 - 0x2F folosind adresarea indirecta:

movlw 0x20 ; incarca in W constanta literala 0x10 - initializare pointer

movwf FSR ; incarca pointerul in FSR

next: clrf INDF ; reseteaza continutul locatiei pointate de FSR

incf FSR ; incrementeaza pointerul

btfss FSR, 5 ; test bit 5 din FSR si daca acesta este "1", atunci se sare peste instr. urmat.

goto next ; reluarea buclei prin salt la "next"

. . . . . . ; continuarea codului

Observatie: Registrul W este folosit de toate instruct. de transfer ( MOVF, MOVWF, MOVLW ).

Observatie: Citirea continutului reg, INDF folosind metoda indirecta de adresare va avea ca rezultat

0x00. Inscrierea reg, INDF folosind metoda indirecta de adresare este neoperationala.

Observatie: In general adresa efectiva pe 9 biti in cazul adresarii indirecte se obtine prin concatenarea

bitului STATUS.IRP cu continutul registrului FSR, asa cum este aratat si in figura anterioara.

Observatie: Familia PIC 16F8x NU utilizeaza:

bitul STATUS.RP1 in adresarea directa pentru selectarea bank-ului curent de lucru ( existind doar doua bank-uri de lucru, pentru selectarea lor este suficient doar bitul STATUS.RP0 );

bitul STATUS.IRP in adresarea indirecta pentru selectarea bank-ului curent de lucru;

Copyright © 2025 - Toate drepturile rezervate