| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Specializarea: Calculatoare

Sporirea inteligenta a randamentului

testorului HP 3070 UNIX

Tema: Sporirea Inteligenta a Randamentului Testorului HP3070 UNIX

Termenul de predarea lucrarii practice si a proiectului:

Continutul proiectului:

Cap. I Introducere in tehnologia SMD

Cap. II Procesul de amplasare a componentelor SMD

Cap. III Testare in circuit a componentelor

Cap. IV Sporirea inteligenta a randamentului testorului HP3070

- Cap. V Concluzii

- Cap. VI Bibliografie

Anexa A. Parte aplicativa

Locul de documentare pentru elaborarea proiectului si executie a lucrarii practice:

Data emiterii temei:

COORDONATOR STIINTIFIC,

SEMNATURA DE PRIMIRE,

Inca din 1970, in industria electronica miniaturizarea a devenit mai importanta decat costurile.

Asa s-a infiripat idea de tehnologie in dimensiuni minimale care, in versiunea tehnologiei SMD, a revolutionat echiparea circuitelor imprimate. Astazi, tehnologia SMD este considerata tehnologia viitorului iar gradul inalt de automatizare specific acesteia a creat standarde noi de calitate si fiabilitate in domeniu.

Circuitele imprimate conventionale (PCB) folosesc componente care sunt conectate prin pini care trec prin gauri (tehnologie de plantare in gaura = THT) pe fata cealalta a cablajului pe care se solderizeaza in val (sau manual). Componentele SMD creeaza marele avantaj de a se aseza si solderiza cu zonele lor de contact direct pe padurile circuitului imprimat. Acesta este principiul inovatic al tehnologiei SMD.

Notiuni de baza in tehnologia SMD:

Exista trei elemente pe care se bazeaza tehnologia si implicit orice abordare:

- componentele;

- substratul;

- sistemul de asamblare (plantare).

Componente SMD

O mare varietate de componente SMD exista in arealul practic; configuratia lor acopera o gama optionala de la componente fara terminale cu extremitati metalizate pana la componente cu terminale lungi si flexibile. Fiecare tip de terminal si incasetare asigura totalitatea cerintelor impuse de manipulare si montaj cerute de standardele internationale.

Ambalarea componentelor SMD

Necesitatile de ambalare a componentelor SMD s-au definit in baza necesitatii de alimentare automata a procesului de plantare si sunt: rola, bagheta, platou. Dintre acestea, rola este varianta cea mai des intalnita, in cazurile uzuale asigurand 10.000 de componente pe o singura rola. Componentele sunt ambalate intr-o banda de masa plastica sau hartie cu lacasuri preformate, in care componentei i se asigura un bun control al orientarii in momentul 'culegerii', o buna protectie in timpul stocarii, transportului si manipularii. Dimensiunile standard ale latimii benzii sunt: 8, 12, 16, 24, 32 mm.

Pentru circuitele integrate cu gabarit mare si componentele cu forme atipice, care nu se acomodeaza la ambalarea pe rola, s-au configurat tuburi (baghete). Pe o bagheta se gasesc aproximativ 200 de componente. Ca si in cazul rolelor, masina de plantat asigura prin mecanismele ei proprii avansul componentelor intr-o cadenta si cu un pas regulat si reglabil.

Materiale:

Materialele folosite in tehnologia SMD includ: materialul, circuitul imprimat, adezivi, aliaje de lipit, decapanti dezoxidanti, masti protectoare electric sau chimic, agenti de curatire.

Alegerea substratului circuitului imprimat depinde de tipul componentelor, densitatea de plantare si de costuri.

Adezivii de inalta eficienta sunt folositi pentru a retine componentele in pozitiile corecte pe substrat in timpul plantarii si solderizarii (in cazul solderizarii in baie cu val).

Aliajele de lipit asigura lipirea componentei pe padurile circuitului imprimat: solderul ca topitura in cuva masinii de cositorit in val, solder paste-ul ca strat conductiv (15-30mm) depus prin printare pe padurile circuitului imprimat.

Alegerea aliajelor de lipit, a fluxurilor si agentilor de spalare se face in contextul efectiv al procesului tehnologic.

Plantarea componentelor SMD

Masini automate sau semiautomate realizeaza preluarea componentelor de pe ambalajul lor si plantarea pe circuitul imprimat cu ajutorul unor capete de plantare. In linii mari, acestea sunt pensete cu vacuum, care 'sorb' componenta si o planteaza in locul descris cu exactitate de programul masinii. In fapt, capetele de plantat se configureaza ca unitati de plantare care includ una sau mai multe pensete.

Parametrii operatiei de plantare sunt: secventialitatea si simultaneitatea, combinarea si realizarea acestora fiind specifica fiecarei masini. Capacitatea de plantare, direct dependenta de configurarea unitatii de plantare, variaza de la cateva sute la zeci de mii de componente pe ora.

Solderizarea

Exista doua metode importante de solderizare: 'cu val' si 'prin recristalizare.'

In cazul metodei 'cu val', un adeziv special retine componenta de plantare. Acest adeziv polimerizeaza in cuptor, faza dupa care aderenta componentei pe pad-uri este suficienta pentru a trece prin dublul val al masinii de cositorit.

In cazul metodei 'prin recristalizare', solderul este o pasta de solderizare cu 10 % flux in compozitie care se depune pe padurile circuitului imprimat. La plantare, terminalele componentei se scufunda in solder paste. In cuptor se incalzeste aliajul, are loc topirea, apoi recristalizarea.

Proiectarea circuitului imprimat

Proiectarea PCB populate cu SMD introduce elemente specifice, cum ar fi:

- materialul substratului si componentele pot avea coeficienti termici diferiti si trebuie prevazut un strat absorbant al stress-ului termic:

- pozitia componentelor SMD este relativa fata de padurile cu solder, ele pot aluneca in timpul procesului, de aceea dimensiunile componentelor, toleranta la dimensiune, toleranta padurilor, acuratetea de plantare a masinii au alte semnificatii decat in plantarea componentelor prin gauri;

- alegerea procesului de plantare, implicit proiectarea circuitului imprimat, este facuta in cooncordanta cu tipul echiparii:

Tip I - PCB cu componente exclusiv SMD, cu una sau doua fete;

Tip II A - PCB mixt: cu componente SMD si gaura pe prima fata si componente SMD (de obicei mici) pe fata a doua;

Tip II B - PCB mixt: cu componente SMD, gaura pe prima fata si componente SMD (de obicei mici) pe fata a doua.

Primul pas in proiectarea unui circuit SMD consta in definirea amprentelor pentru toate componentele SMD. Parametrii proiectarii care tin de dimensionarea amprentelor, toleranta la dimensiuni, pozitia amprentelor rezulta in urma analizelor statistice sau sunt preluate din documentatia de firma.

1.2. Realizarea cablajelor multistrat

Circuitele electronice ajuta la conectarea componentelor active si pasive dintr-un circuit,acesta nefiind altceva decat niste trasee din cupru care strabat straturi izolatoare fiind astfel si ele izolate unele fata de altele. Aceste trasee datorita tehnologiei avansate pot sa aiba grosimi foarte mici cca 0,101mm. Datorita acestui fapt se pot crea circuite de conectare foarte complexe si pe suprafete foarte mici , prin utilizarea cablajului multistrat. Pentru a putea face o comparati trebuie sa spunem ca parul uman are o grosime de cca 0,07mm

Astazi placile de circuit se utilizeaza in aproape toate echipamentele care folosesc circuite electrice Se disting mai multe tipuri de circuite imprimate:

- simplu placat -are o folie de cupru aplicata pe un suport ozolator de obicei pertinax sau sticlotextolit.

- dublu placat-acesta este format din doua folii de cupru izolat intre ele de un material dielectic care in afara de cele mentionate mai inainte mai poate sa fie kevlar,kalit,teflon,etc.

- multistrat-acestea contin mai multe straturi de circuite izolate intre ele printr-un dielectric de obicei de acelasi tip

- flexibile-in acest caz materialul izolator este fabricat dintr-un dielectric flexibil care in final va avea o flexibilitate ridicata.

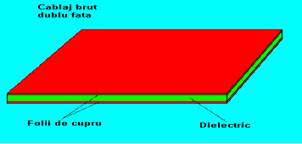

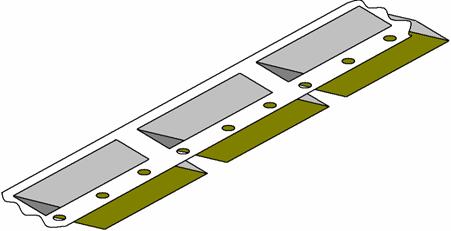

Fabricarea circuitelor

multistrat porneste de la un prefabricat (placat cu cupru) compus din doua

straturi de cupru separate intre ele de un dielectric.

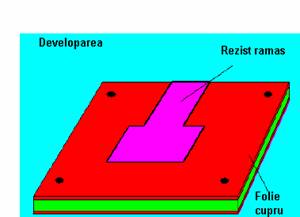

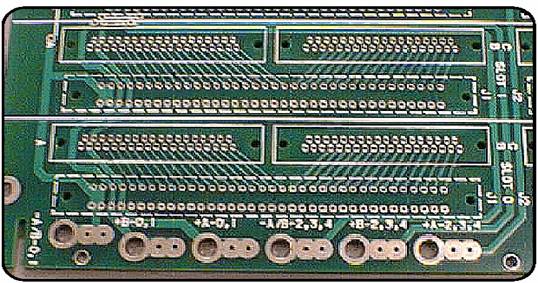

Figura 1 : Cablaj brut

Acesta se curata de impuritati si se degreseaza datorita faptului ca dorind sa executam circuite de foarte mare acuratete si de grosimi mici , se da o mare importanta acestei operatii pentru ca altfel circuitul nou creat ar putea fi distrus in timp , de catre eventualele resturi ramase pe suprafata de cupru (corodat). Dupa aceasta operatie acest prefabricat va fi acoperit cu un strat fotosensibil de material numit rezist.Se acopera cu acest strat protector pentru a proteja folia de cupru in timpul proceselor pe care l-e vom parcurge.

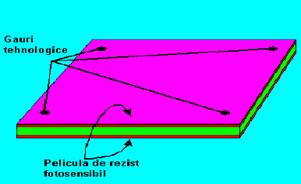

Materialul cu care a

fost acoperit este sensibil de asemenea la radiatia ultravioleta de aceea in

Figura 2 : Procesul de gaurire

timpul lucrului se foloseste o lumina galbena. Acest material este aplicat prin presare cu o rola fierbinte care sa asigure omogenizarea acesteia pe suprafata de cupru .Daca acest strat de rezist nu este corect aplicat si uniform , se vor crea brese prin care ar putea patrunde substanta de corodare distrugand astfel prin intrerupere circuitul in lucru.

Odata facuta aceasta acoperire, in cablajul (prefabricatul) creat se practica in cele patru colturi niste gauri tehnologice care vor ajuta la o buna fixare a acestuia si apoi a straturilor care vor urma sa fie suprapuse peste aceasta. Dupa ce se realizeaza aceste gauri , pe acest prefabricat se aplica filmul creat inainte cu imaginea cablajului care se doreste sa fie executat pe acest nivel de cablaj.

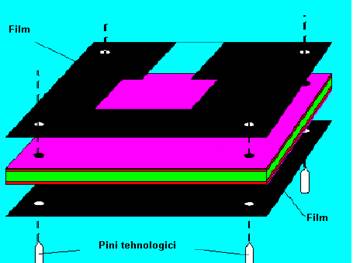

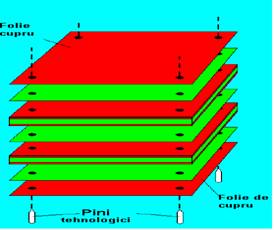

Figura 3 : Niveluri de strat

Pentru fiecare nivel de circuit imprimat pe care il vom crea se va aplica un alt film creat pentru acel nivel , care va trebui sa se suprapuna foarte precis , acesta fiind ghidat de cei patru pini tehnologici care patrund foarte precis in gaurile tehnologice executate. Prefabricatul acoperit cu film este expus apoi unei lumini albe foarte puternice. Observam ca acolo unde filmul nu a fost transparent stratul de material fotosensibil nu a fost fixat pe folia de cupru si acesta va putea fi indepartat la urmatorul pas din procesul tehnologic adica prin developare.

Prin acest proces stratul de material fotosensibil care nu a fost expus la lumina datorita filmului foto va fi inlaturat.pe portiunile unde fotorezistul a fost expus la lumina , acesta a ramas fixat pe placa formad o pelicula subtire care acopera portiunea din folia de cupru luand forma filmului prin care a fost expus la lumina si protejeaza astfel portiunea respectiva din folia de cupru pentru urmatoarea etapa tehnologica.

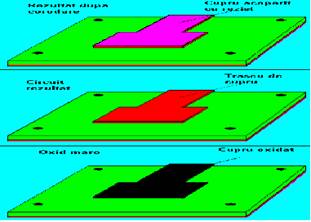

Figera 4: Cablajul multistrat

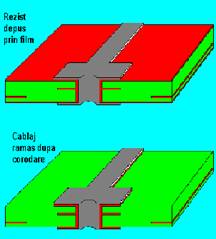

In aceasta etapa

tehnologica acea portiune din folia de cupru care nu este acoperita cu

fotorezist trebuie sa dispara de pe acest prefabricat ramanand astfel numai

traseele acoperite cu fotorezistul ramas dupa developare. Acest procedeu este o

reactie chimica prin care cuprul de pe suprafetele neacoperite cu fotorezist se

combina cu solutia in care prefabricatul este scufundat pana la indepartarea

oricaror reminiscente din acesta.

Figura 5: Decaparea cablajului

Dupa ce si aceasta etapa a fost parcursa si prefabricatul este curatat ,inclusiv de stratul de fotorezist care l-a protejat in timpul reactiei chimice obtinem o fata de cablaj propriu zis. Acest cablaj este acoperit apoi printr-un procedeu chimic de un oxid maro , acesta se va depune astfel intr-un strat foarte subtire pe folia de cupru ramasa schimband astfel caracteristicile chimice ale acestuia prin adeziune , atunci cand cablajul individual va fi combinat pentru a crea un cablaj multistrat schimband astfel culoarea cuprului in negru.

Pentru a putea crea un cablaj multistrat toate , cablajele din fiecare nivel care il compun trebuie sa parcurga aceste etape , apoi fiecare din aceste cablaje singulare sant fixate dupa cum se poate vedea si in figura creandu-se astfel un sandwich fixat cu precizie de pini tehnologici pe orizontala si prin presare folosind intre fiecare doua straturi un lipici cu caracteristici izolatoare foarte bune. Cablajul multistrat obtinut este astfel tinut un timp presat pana cand lipiciul isi va face efectul. Acest proces se va termina prin prelucrarea acestui cablaj mutlistrat ca un bloc compact indepartand orice rest din procesul tehnologic care ar putea fi ramas accidental.

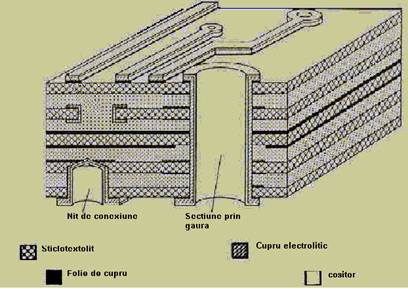

Cablajul obtinut astfel nu are inca nici o legatura electrica intre starturile care il compun , aceasta urmand sa se faca ulterior prin gaurile care se vor realiza.

Operatiunea de gaurire

trebuie sa fie foarte precisa si in functie de complexitatea circuitului

aceasta

Figura 6: Gaurirea cablajului multistrat

poate fi coordonata de catre un computer care arata cu exactitate locul unde acestea trebuie facute.Alinierea gaurilor se va face tot tinandu-se seama de gaurile tehnologice.

Dupa ce si aceasta operatie a fost facuta se va depune un

strat foarte subtire de cupru atat pe suprafetele exterioare cat si in

interiorul gaurilor .

Figura 7: Metalizarea gairilor

Cablajul multistrat este astfel conectat dinspre exterior spre interior , dar fara nici o urma pe straturile exterioare in folia de cupru de pe acestea .

Acum cablajul multistrat va urma aceleasi etape ca si unul dintre straturile din interior , pentru ca la final pe straturile exterioare sa avem trseele de cupru de care avem nevoie.La final straturile exteriore sant acoperite cu un strat de material (lac care va proteja cablajul contra oxidarii si distrugerii in timp),iar gaurile si in jurul acestora se va depune un strat subtire de cositor de obicei, sau un alt metal a carui oxid nu afecteaza proprietatile electrice ale acestuia . Straturile din acest multistrat mai pot fi conectate si prin alte metode. Cel mai raspandit procedeu mecanic de "metalizare" a gaurilor consta in introducerea unor capse metalice (avand lungimea putin mai mare decat grosimea stratului izolant) in gaurile cablajului finit, urmata de blancuirea (rasfrangerea)

ambelor extremitati ale capsei.

Este evident ca acest

procedeu comporta numeroase inconveniente: este laborios si putin fiabil

(intrucat probabilitatea unui contact perfect intre capsa si conductorul imprimat este destul de redusa), implica

tolerante foarte stranse pentru gauri si capse, necesita un consum relativ

ridicat de materiale (capse) etc.

Figura 8: Structura finala

In consecinta, este mai avantajoasa realizarea pe cale chimica a cablajelor imprimate multistrat (si a gaurilor metalizate respective). In figura urmatoare se prezinta un cablaj multistrat realizat prin tehnica descrisa mai sus.

Figura 9: Cablajul final multistrat

2. Procesul de amplasare a componentelor SMD

2.1. Tehnologii de amplasare a componentelor SMD

Tehnologia montarii pe suprafata sau SMT ( SMT=Surface Mount Technology ) s-a impus in ultimii ani ca principala metoda de fabricatie a modulelorelectronice. Tehnologia montarii pe suprafata a permis realizarea de module electronice mai performante si mai fiabile, cu greutate, volum si costuri mai scazute decat tehnologia anterioara, ce utilizeaza componente cu terminale pentru insertie THT (THT=Through-Hole Technology). Componentele electronice utilizate au primit denumiri corespunzatoare acestor tehnologii. Intalnim astfel componentepentru montarea pe

suprafata (SMD =Surface Mounted Devices) si componente cu terminale pentru insertie pe care le vom numi in continuare componente THT.

O caracteristica definitorie pentru SMT este montarea componentelor electronice pe suprafata circuitului imprimat, fara a patrunde prin gaurile practicate in circuitul imprimat, ca in tehnologia THT. Aceasta modificare, minora la prima vedere, avea sa influenteze practice toata industria electronica, de la proiectare, procese de prelucrare sau de asamblare, materiale si capsule ale componentelor electronice, etc.

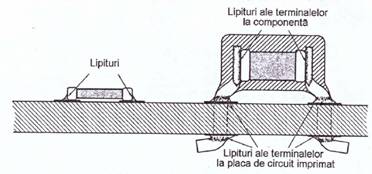

Figura 1: Lipirea terminalelor

In figura 1 se prezinta un condensator ceramic montat in variantele SMT si THT. Se observa modul de conectare la circuitul imprimat, in cele doua cazuri. Se observa, deasemenea si faptul ca varianta THT a condensatorului are doua lipituri suplimentare, cele ale terminalelor, fapt care constiutuie o sursa de reducere a fiabilitatii asamblarii. Ideea montarii pe suprafata a componentelor nu este noua. Primele componente SMD, asa numitele "flat packs" sau capsule plate, au fost utitlizate la circuitele hibride in anii 1960.

Metodele de proiectare si echipamentele tehnologice ale tehnologiei montarii pe suprafata actuale sunt insa diferite de cele de atunci. Tehnologia actuala necesita regandirea profunda a proceselor tehnologice alaturi de o infrastructura corespunzatoare care sa le sustina. In stadiul actual de dezvoltare nu toate componentele sunt disponibile in varianta SMD si de aceea, procesul tehnologic trebiue sa permita si utilizarea componentelor cu montare prin insertie.

Exista trei mari categorii de module SMT numite "Tipul 1", "Tipul 2", "Tipul 3". Ordinea operatiilor si procesare sunt diferite pentru fiecare tip si fiecare varianta necesita echipament diferit.

Tipul 1 de subansamblu care contine numai componente cu montare pe suprafata, mai este numit "SMT pur". Poate exista varianta echipata pe o fata sau pe ambele.

Tipul 3 de subansamblu SMT contine numai componente discrete cu montare pe suprafata (cum ar fi rezistoare, condensatoare si tranzistoare) lipite pe partea inferioara a circuitului imprimat, pe fata superioara fiind componente THT.

Tipul 2 de modul reprezinta o combinatie intre tipurile 1 si 3. De regula nu contine nici o componenta SMD integrata pe partea inferioara, dar poate contine componente discrete lipite pe aceasta parte.

Componentele cu montare pe suprafata de tipul pasiv sau active nu difera functional de componentele cu terminale pentru insertie (THT), componente devenite acum clasice. Ceea ce le diferentiaza este varianta diferita de package (incapsulare) a celor doua. Componentele SMD asigura o densitate mare de echipare a circuitelor, in special prin dimensiunilor reduse ale acestora. Reducerea dimensiunilor este benefica nu numai pentru economisirea spatiului pe placa de circuit imprimat dar si pentru reducerea elementelor parazite ale componentelor, componentele SMD avand astfel performante electrice superioare, acest lucru fiin valabil atat pentru compnentele passive cat si pentru cele active.

Asa cum s-a amintit, componentele SMD se monteaza pe suprafata circuitului imprimat, fara a patrunde prin gaurile metalizate ca in tehnologia THT. In acest caz, zona lipiturii asigura pe langa contactul electric si robustetea mecanica a asamblarii, avand un rol decisiv in fiabilitatea produsului electronic.

Componentele SMD sunt destinate celor doua mari aplicatii: comerciale si militare. Pentru aplicatiile comerciale mediul ambient este mai bland si se pot utilize si capsule care nu sunt ermetice.

O alta caracteristica comuna componentelor SMD este solicitarea termica sporita a lor fata de componentele THT in timpul procesului de lipire. Aceasta solicitare le face mai sensibile la aparitia de crapaturi datorate umiditatii. Crapaturile se produc atunci cand umiditatea acumulata in componenta este eliberata brusc la aparitia socului termic provocat de procesul de lipire.. Pe de alta parte, la lipirea prin procedeul "reflow", termintiile componentelor SMD sunt mai putin solicitate termic decat terminalele componetelor THT la lipirea in val, temperature componentelor SMD in timpul lipirii fiind mai redusa. De aceea, cerintele privind solderabilitatea sunt mai mari pentru componentele SMD. Acest fapt este accentuat si de tendinta actuala de diminuare a utilizarii fluxurilor active la asamblarea componentelor SMD.

Alta caracteristica a componentelor SMD este faptul ca, datorita dimensiunilor mici, marcarea lor este mai dificila, in special pentru componente discrete. Daca se pierde posibilitatea de identificare a acestora, atunci de cele mai multe ori componentele nu se mai utilizeaza. Desigur, este posibila masurarea lor, dar este o operatie mare consumatoare de timp. Dimensiunile mici ale componentelor si posibilitatile limitate de identificare fac ca sa se prefere plasarea automata a acestora.

Componente pasive SMD

In ceea ce priveste componentele passive SMD exista cateva categorii importante cum ar fi rezistoare in straturi groase sau cu pelicula metalica, condensatoare ceramice, condensatoare electrolitice cu tantal, alaturi de care se impun si mai noile venite condensatoare cu aluminiu, rezistoare (semi)reglabile, condensatoare (semi)reglabile, inductoare, s.a.

Formele cele mai utilizate ale componentelor pasive sunt cele dreptunghiulare si cilindrice. Componentele pasive SMD au fost foarte repede asimilatesi utilizate in produse deoarece ocupa pe cablajul imprimat un spatiu egal cu jumatate din cel necesar pentru o componenta THT. In plus, ele se pot plasa pe fata inferioara a circuitului imprimat ca in cazul placilor SMT de tipul 2 sau 3. Masa acestor componente este de circa 10 ori mai mica dacat a componentelor similare cu terminale.

Componentele SMD

au fost utilizate pe scara larga in Japonia pentru industria bunurilor de larg consum si in SUA in industria automobilelor, pretul lor scazand astazi sub pretul componentelor THT.

2.2. Tipuri de masini de plantat component

Figura 1:FUJI NXT mașina de plantat componente

Termeni utilizati

PCB (Printed Circuit Board) - placa cu circuite imprimate;

Feeder - dispozitiv de alimentare componente;

Stick feeder - dispozitiv de alimentare componente, in bagheta;

Nozzle - dispozitv de ridicare a componentei cu ajutorul vacuum-ului;

Mark Fiducial - punct de recunoastere a placii;

Skip - a omite, a sari ;

Conveyor - sistemul de transport al placii;

Clamp - sistem de prindere;

Device - mecanism de fixare a alimentatoarelor (feeder-e);

Holder - dispozitivul de sustinere a nozzle-urilor;

Pick - a ridica;

Display - ecran;

Area - suprafata, arie;

Back-up pins - pini pentru sustinerea placii;

Tray - suport pentru componente in tava;

Tray Unit - unitate pt. tavi;

Part number - numarul de identificare al componentelor;

Maintenance - service/intretinere sau dupa caz nivel de operare;

Set-up - totalitatea componentelor existente intr-un program (fisa cu locatia, tipul si pasul feeder-ului, Part Number-ul, tipul de nozzle si programe folosite);

SIC - "Station Instruction Card" - documentul cu instructiuni de lucru;

Bottleneck Analysis Report - raportul de productie;

Moisture Sensitive Device (MSD) - "Componente sensibile la umiditate";

CHO - Change Over - schimbare de produs;

Top/Bottom - partea superioara/inferioara a PCB-ului.

Alcatuire masina

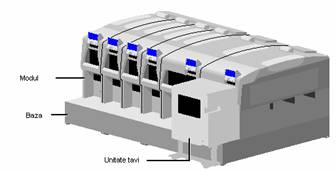

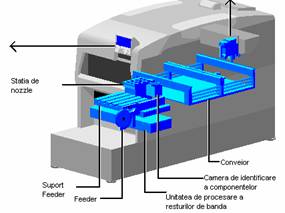

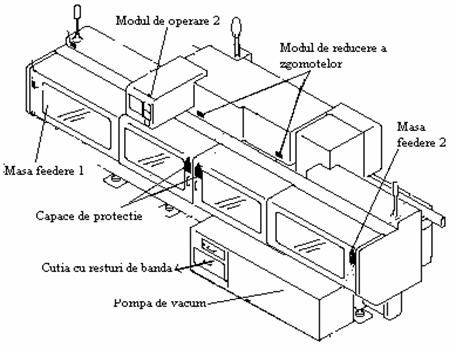

Figura 2: Subansamble ale mașinii

Masina Fuji NXT este destinata plantarii de componente mici si mari cu o mare acuratete de plantare. Pentru utilizarea corecta si sigura a acestei masini, este necesar sa lucreze la aceasta masina doar operatori calificati.

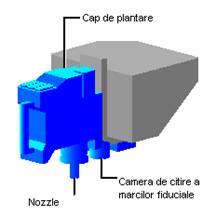

Masina este compusa din module independente (in cazul aparitiei unei erori se poate opera modulul respectiv, fara sa afecteze procesul de productie la celelalte module) in interiorul carora se realizeaza montarea componentelor de pe feedere pe PCB-uri. Modulele sunt cate 2 pe o baza/system, fiecare modul in parte avand modul de comanda si semafor. Modulul de plantare poate fi de doua tipuri: pt. feedere (MFU) si pt. tavite (Tray Unit). Ambele utilizeaza "Mark Camera", camera de citire a fiducial-ilor.

Figura 3: Modul independent

a) Multy Feeder Unit - sunt modulele care utilizeaza ca tip de alimentare: feeder-ele - alimentatoare pentru role si Stick feeder-ul - alimentator pentru componente in baghete (tuburi). Acestea pot fi utilizate in combinatie pe un modul.

b) Modul de tip MTU (Multy Tray Unit) - este un modul independent, prevazut cu sertare pe care se pot aseza tavite cu tipuri diferite de componente (mai multe Part Number-e). Tavitele se aseaza in sertare astfel incit sa nu existe nimic sub ele (componente, hartie), sa fie lipite de partea din fata a sertarului si de unul din peretii laterali. Fixarea se realizeza cu ajutorul magnetilor (pe laturile care nu sunt fixate).

Pentru colectarea componentelor rejectate acest modul utilizeaza conveiorul de rejectii (pentru Fine Pitch-uri, BGA-uri) si cutia de rejectii pentru restul componentelor. La manipularea componentelor de tip Fine Pitch se va utilize vaccum pen.

Semaforul are trei culori: alb, rosu si verde

Alb: masina este oprita temporar.

Rosu: semnalizeaza oprirea masinii datorita unei role terminate, aparitia unei erori sau semnifica o eroare de vizualizare.

Verde : semnifica un mod de asteptare (asteptare PCB, comanda) sau semnifica actionare automata (montare componente).

Transportul placilor se realizeaza cu ajutorul conveioarelor. Masina Fuji NXT are conveioare independente in interiorul fiecarui modul. Acestea actioneaza separat si sunt prevazute cu senzori de prezenta care sesizeaza intrarea sau iesirea PCB-urilor la stopper-ele din fiecare modul al masinii. Fixarea si sustinerea placii pe conveior se realizeza cu ajutorul clamps-urilor.

Back-up pini (pini magnetici) - sunt dispozitive de sustinere a PCB-urilor. Sunt situati pe un dispozitiv, pe conveyor in partea din interior a masinii. Sunt asezati pe masa ridicatoare automat de catre masina doar daca programul incarcat a fost setat in prealabil de ingineri sa utilizeze back-up pini.

Masina Fuji NXT are 2 tipuri de nozzle :

Figura 4: Tipuri de nozzle

Nozzle-ul de tip index se indexeaza intre ele in functie de marimea componentelor. Se monteaza mai multe pe o turela. O particularitate, reprezinta faptul ca la schimbarea programului nozzle-urile se schimba toate dintr-o statie de nozzle-uri. Nozzle de tip single - un singur nozzle. Nozzle-urile se schimba doar din statia de nozzle-uri, in functie de marimea componentei. Dupa fiecare schimbare de nozzle, acesta este verificat automat de masina. Acest tip de nozzle-uri se folosesc in general pentru componentele mari (BGA-uri, Fine Pitch-uri, shield-uri, etc).

Statia de nozzle - este o cutie de inmagazinare a nozzle-urilor. Nozzle-urile sunt setate in locatiile din statie .

In cazul unor probleme la nozzle operatorul poate scoate nozzle-urile din statie pentru a fi verificate si curatate.

Figura 4: Curațare nozzle

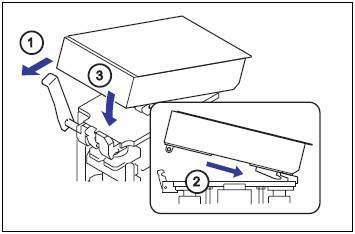

Scoaterea statiei de nozzle

Introducerea statiei de nozzle

Figura 5: Operația de schimbare nozzle

Masina Fuji CP 642,643 (Chip Placement) este destinata plantarii de componente mici si foarte mici cu o mare acuratete de plantare. Masina Fuji CP 642,643 planteaza componente de tip chip (rezistente, condensatori, diode, quarturi etc).

Figura 6: FUJI CP mașina de plantat componente

Vedere din fata

Figura 7: FUJI CP Componente si subansamble

Conveiorul de intrare;

Modulul de putere (intrerupatorul general);

Modulul de comanda (operare);

Cutia Servomotorului 1;

Cutia Servomotorului 2;

Cutia de control 1;

Cutia de control 2;

Conveiorul de iesire.

Vedere din spate

Modulul de operare;

Masa cu feedere 1 (70 device-uri);

Pompa de vacuum;

Cutia cu resturi de banda (Vaste tape box);

Modulul de reducere a zgomotelor;

Masa cu feedere 2 (70 device-uri).

Conveioarele (sistemul de transport al placilor):

Conveiorul de intrare primeste placi de la masina anterioara. Daca nu primeste placi masina afiseaza mesajul "Wait PCB".

Main Conveior (Masa XYZ) preia placa de la conveiorul de intrare (la Fuji CP 643 de pe carrier) coboara pe axa Z (efectueaza miscari sus - jos) fixeaza PCB-ul, apoi foloseste axele X (efectueaza miscari stinga - dreapta) si Y (efectueaza miscari fata - spate) pentru plantarea componentelor.

Conveiorul de iesire preia placa de pe conveiorul principal dupa terminarea programului pe placa.

Figura 8: Conveiorul de ieșire

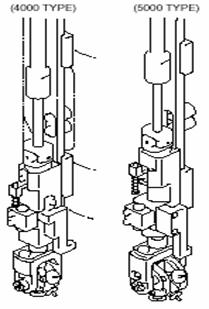

Figura 9: Capul de amplasare componente

Turela are 20 de capete identice intre ele, fiecare continind 6 nozzle-uri de dimensiuni si tipuri diferite.

Marimile de nozzle-uri folosite la masina Fuji CP 642,643 sunt: q0.7mm; q1.0mm; q1.3mm; q1.8mm, q2.5mm; q3.7mm, q5.0mm in functie de necesitatea produsului.

Tipurile, dimensiunile si pozitia nozzle-urilor sint cuprinse in NAT (Nozzle Alocation Table) tabel de alocare a nozzle.

Figura 10: Capetele turelei

Capetele turelei sunt notate de la A.la T; iar nozzle-urile sunt numerotate de la 1 la 6. Nozzle holder (sustinator de nozzle-uri), contine un ansamblu de nozzle-uri. Capul de plasare (placing head) - cele 20 de capete sunt dispuse pe o turela rotitoare. Fiecare cap are cate 6 tipuri de nozzle-uri de marimi diferite in nozzle holder, pentru a putea ridica piese de diferite marimi. Capetele ridica componentele de pe alimentatoarele cu componente (feeders), le sustin in timpul procesului de vizionare (vision processing) si le plaseaza pe placa.

Tipuri de nozzle

Nozzle cu disc (galben) reflector, de tip index (principalul folosit la CP 642/643), folosite pentru investigarea formei componentelor cu Backlight (lumina din spate) in acest caz obtinindu-se imaginea (umbra) componentei;

Nozzle cu disc negru (Black nozzle) pentru investigarea formei componentelor cu Frontlight (lumina din fata). Aceste nozzle-uri se folosesc pentru cazul in care sint pozitionate doar componente de tip J-led.

Fuji QP (quality placement ) - masina de plantat componente

Semafor

ICM Independent Control Module PLM Placement Module

![]()

Figura 11: Fuji QP (quality placement ) - masina de plantat component

Masina Fuji QP 242E (Quality Placement) este destinata plantarii de componente mari cu o mare acuratete de plantare. Masina Fuji QP 242E planteaza componente de tip BGA-uri, Fine Pitch-uri, E-prom-uri (memorii), Quart-uri, Shield-uri, Conectori, etc

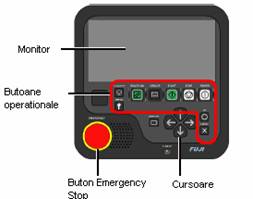

Independent Control Module -modulul de control individual, reprezinta partea de comanda (software) a masinii Fuji QP.

Modulul contine: panourile de comanda, display-urile si monitoarele specifice, hebl-ul (comutatorul de curent electric, care se afla in spatele masinii), butoanele Power On/Off, Start, Reset, Cycle Stop, cheia pentru comutarea comenzii Front/Rear, un monitor pentru vizualizarea componentelor si a ozzle-urilor si butonul de Emergency Stop.

Deasupra se afla un turn semafor care are trei culori: rosu, galben, verde.

Rosu : semnifica aparitia unei erori sau semnifica o eroare de vizualizare.

Galben : semnalizeaza oprirea masinii datorita unei role terminate, s-a terminat productia programata sau semnifica o rola terminate.

Verde : semnifica un mod de asteptare (asteptare PCB, comanda) sau semnifica actionare automata (montare componente).

Transportul placilor se realizeaza cu ajutorul conveioarelor. Masina Fuji QP are conveyor de intrare (cu rol de mentinere in asteptare a PCB-ului ce urmeaza a fi plantat) si conveioare independente in interiorul fiecarui modul. Acestea actioneaza separat si sunt prevazute cu senzori de prezenta, care sesizeaza intrarea sau iesirea PCB-urilor la stopper-ele din fiecare modul al masinii. Fixarea si sustinerea placii pe conveior se realizeza cu ajutorul clamps-urilor.

Masina Fuji QP are 2 tipuri de head-uri si 2 tipuri de nozzle:

a) Head-ul de tip index - are maxim patru nozzle-uri. Nozzle-urile se indexeaza (se schimba) intre ele in functie de marimea componentelor.

Figura 12: Head tip index Figura 13: Nozzle disc galben reflector

b) Head de tip single - un singur nozzle. Nozzle-urile se schimba intr-o statie de nozzle-uri, in functie de marimea componentei. Statiile pot avea 3, 5, 7, 9, 12 locatii pentru nozzle. Dupa fiecare schimbare de nozzle, acesta este verificat automat de masina cu ajutorul a doi senzori care verifica existenta nozzle-ului si corectitudinea schimbarii.

c) Nozzle cu disc galben reflector. Acest tip de nozzle utilizeaza pentru investigarea componentelor camera Back-light (lumina din spate).

d) Nozzle cu disc negru. Pentru investigarea componentei se

foloseste camera Front-light (lumina din fata).

d) Nozzle cu disc negru. Pentru investigarea componentei se

foloseste camera Front-light (lumina din fata).

Figura 14: Head de tip single Figura 15: Camera front-light

Obs: Acest tip de nozzle-uri se folosesc in general pentru componentele mari (BGA-uri, Fine Pitch-uri, shield-uri, etc).

PLM (Placement Module) - modul independent de plantare. In cazul aparitiei unei erori daca se selecteaza modulul respectiv, se poate interveni fara sa afecteze procesul de productie la celelalte module. Modulul de plantare poate fi de doua tipuri: MFU (Multy Feeder Unit) si MTU (Multy Tray Unit). Ambele utilizeaza "Mark Camera", camera de citire a fiducial-ilor.

a) Multy Feeder Unit - sunt modulele care utilizeaza ca tip de alimentare: feeder-ele - alimentatoare pentru role, STU (Single Tray Unit) - alimentator cu o singura tavita cu componente si Stick feeder-ul - alimentator pentru componente in baghete (tuburi). Acestea pot fi utilizate in combinatie pe un modul.

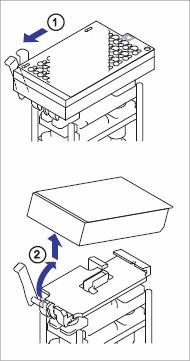

b) Modul de tip MTU (Multy Tray Unit) - este un modul independent, prevazut cu sertare (unu→ zece = 20 locatii) pe care se pot aseza tavite cu tipuri diferite de componente (mai multe Part Number-e).

Figura 16: Modul de tip MTU si STU

Tavitele se pot aseza suprapuse in sertare. Tavitele se aseaza in sertare astfel incit sa nu existe nimic sub ele (componente, hartie), sa fie lipite de partea din fata a sertarului si de unul din peretii laterali. Fixarea se realizeza cu ajutorul magnetilor (pe laturile care nu sunt fixate).

Tavita se poate indeparta automat la terminarea componentelor cu dispozitivul "Remover head". Acesta este actionat cu vacuum si are rolul de a indeparta tavile in "box reject" (cutia de inmagazinare a tavitelor goale).

Cutia de inmagazinare a tavitelor goale trebuie golita la aparitia mesajului de eroare "MTU: Emty Tray Container Full". Pentru a avea acces la cutia de inmagazinare a tavitelor goale trebuie ridicat sistemul de sertare cu ajutorul butonului "Tray Origin", localizat pe partea frontala a MTU-ului (dreapta sus).

Pentru colectarea componentelor rejectate acest modul utilizeaza conveiorul de rejectii (pentru Fine Pitch-uri, BGA-uri) si cutia de rejectii pentru restul componentelor.

Feeder-ele (tipuri de alimentatoare utilizate)

Feeder-ele se folosesc pentru alimentarea masinii Fuji QP 242 cu componente electronice ambalate in role.

Aceste feeder-e se marcheaza astfel: W (xx) y P (xx) unde:

W (xx) = este valoarea latimii benzii folosite (mm);

y = tipul benzii folosite: D - pentru hartie; E - pentru plastic.

P (xx) = pasul benzii - distanta intre centrele a 2 componente alaturate de pe banda (tape pitch = pasul benzii) in mm (xx) = mm.

Ex: W12E P8 inseamna feeder pentru banda din plastic (E) cu latimea (W) de 12 mm si pas (P) de 8 mm.

Feeder-ele pentru masina Fuji QP sunt alimentate electric si indexarea componentelor se realizeaza electronic sau pneumatic.

Feeder-ele cu alimentare electrica si indexare pneumatica sunt prevazute cu doua cabluri de alimentare. Unul pentru "priza" electrica, altul pentru "priza" de aer (aerul comprimat actionind un piston dupa fiecare ridicare de componenta). Pasul acestui tip de feeder nu poate fi modificat de catre operator. Modificarea se efectueaza de catre tehnicianul de SMT.

Feeder-ele cu alimentare electrica si indexare electronica sunt prevazute cu un singur cablu de alimentare, pentru priza electrica. Indexarea se realizeza cu ajutorul unui motoras actionat pas cu pas. Pasul feeder-ului se modifica cu ajutorul sagetilor "+","-" situate in partea superioara a feeder-ului.

Figura 17:Tipuri de Feedere

Calcularea pasului benzii cu componente:

Se aleg doua repere identice la doua componente consecutive si se masoara numarul de pasi de incrementare ai benzii dintre cele doua repere. Apoi se inmulteste numarul de pasi de indexare rezultat cu marimea pasului de incrementare si rezulta pasul benzii. Pasul de incrementare este distanta dintre doua orificii alaturate si poate fi de 4 mm (sau de 2 mm, pentru componente foarte mici intalnite mai rar).

Al doilea

reper (gaura cea mai apropiata de

marginea din stanga casutei) urmatoare din banda) Primul reper

(gaura cea mai apropiata de marginea

din stanga a unei casute din banda)

![]()

Exemplu:

Figura 18: Calcularea pasului benzii

Pentru cazul din figura anterioara avem trei gauri pe care le inmultim cu distanta dintre gauri, adica 4 mm si obtinem pasul benzii de 12 mm.

Stick feeder-ul - este un dispozitiv de alimentare ce utilizeaza baghete (PVC) cu componente. Indexarea se realizeaza prin vibratie. Poate fi setata pe "Continuose" sa vibreze continuu sau "by pick-up" sa vibreze numai la ridicarea componentei.

Figura 19: Stick feeder-ul

STU (Single Tray Unit ) - este un dispozitiv de alimentare ce utilizeaza tavite cu componente (un singur Part Number). Se monteaza in interiorul modulului de feeder-e, de catre inginerul de proces.

STU-ul are 2 cabluri: unul pentru conectarea la "priza" de curent (cablul cu eticheta "Parts Set") se conecteaza la device-ul specificat in SIC, iar cel ramas ("Tray Out"), la pozitia imediat urmatoare.

Tavițele se aseaza astfel incit sa nu existe nimic sub ele (componente, hartie), sa fie lipite de partea din fata a sertarului si de unul din peretii laterali. Fixarea se realizeza cu ajutorul magnetilor (pe laturile care nu sunt fixate).

Figura 19: STU (Single Tray Unit )

Tavițele cu componente se aseaza in dispozitiv in functie de orientare (indicate de "tesitura" tavitei - orientarea componentelor din tava trebuie sa fie conform tesiturii) specificata in SIC-ul aferent.

Tavita poate fi indepartata automat la terminarea componentelor de dispozitivul "Remover head". Acesta este actionat cu vacuum si are rolul de a indeparta tavile goale in spatiul special alocat.

3.1. Generalitati de test

Testare = in sens larg verificarea unor componente, ansambluri de circuite (placi), aparate (produs final) pentru a vedea daca sunt sau nu in parametri.

Dupa 1990 implicatiile standardelor de calitate ISO au facut ca nici un proces de productie sa nu mai poata fi realizat fara operatiunile de testare si calibrare.

De ce TEST ?

pentru a separa unitatile bune de cele defecte

pentru a localiza defectele si a repara unitatile defecte

pentru a urmari calitatea procesului

pentru a imbunartati procesul de fabricatie

pentru a creste profitul

Proces detestare:

Testul in-circuit este o metoda de testare standard a placilor electronice, ce face parte din sistemul de calitate a tuturor producatorilor de placi electronice populate.

Practic, aceasta metoda permite testarea individuala a componentelor electronice ce sunt deja plantate pe placa electronica. Informatia despre defect este furnizata la nivel de pin de componenta sau componenta pentru a facilita reparatia rapida a placilor cu defecte.

Testul in circuit permite detectarea urmatoarelor erori: scurt circuite, intreruperi de trasee electrice, componente lipsa, avariate sau defectuos plasate, componente cu parametri in afara limitelelor de toleranta, componente incorect programate, masuratori de timp/frecventa in afara limitelor de toleranta, teste analogice si digitale eronat realizate cu placa electronica alimentata.

Ca si tipuri de componente, pot fi masurate in-circuit toate tipurile de componente pasive (rezistori, capacitori, inductori, diode, tranzistori etc.) circuite integrate analogice (amplificatoare operationale, comparatoare etc) circuite hibride (CAN, CNA-uri, regulatoare de tensiune etc.) circuite electronice digitale.

De asemenea, se pot masura timpi, frecvente, curenti, tensiuni in AC si DC, se pot genera si masura forme de unda de diverse tipuri, se pot sterge / programa / verifica circuite digitale.

De ce se utilizeaza testul in-circuit

Pana la 30% din placile electronice manufacturate pot avea erori la nivel de componenta: chiar daca tehnicile de productie s-au imbunatatit scaderea dimensiunilor componentelor si a placilor electronice continua sa creeze probleme tehnologice.

Aceste erori trebuie diagnosticate si reparate rapid si eficient. Testul in-circuit testeaza componentele de pe placa elelectronica pe rand, timpul de testare al placii fiind foarte mic.

Astfel, pentru o placa electronica cu 500 de noduri electrice si 1000 de componente, timpul de testare este mai mic de 30 secunde.

Ca principiu, conexiunea electrica este facuta intre fiecare nod electric al placii electronice si interfata standard a masinii de testare pentru a permite testarea individuala a componentelor.

Aceste conexiuni electrice sunt facute prin intermediul unui adaptor individualizat denumit FIXTURE ce contine pini mecanici actionati de arcuri in exterior si o structura de fire de legatura in interior. Pini fac contact cu nodurile electrice de pe placa de testare, iar cablurile electrice din interior fac conexiunea intre pinii de acces la placa electronica si interfata standard a masinii de testare.

3.2. Fixturele de test

Fixture Test

Exista o multitudine de tipuri de pini utilizati pentru a accesa placa electronica. Accesul prin pinii de test se poate realiza numai daca layout-ul placii electronice are prevazute pad-uri de testare adaugate special in faza de design.

Pinii difera prin forma (ascutiti, cu cap tip coroana, tip cupa etc.) si prin dimensiune (100 mils, 75mils, 50 mils).

Semnalele de input/output sunt colectate/directionate de echipamentul de testare in-circuit prin intermediul unor placi de multiplexare numite UltraPIN. Capacitatea de analiza a unui tester ICT Teradyne ajunge la un maximum de 7680 de noduri electrice/ placa electronica.

Transmisia de date intre hardware si computer se face prin intermediul unei magistrale rapide de tip MXI II.

Toate cardurile din sistem sunt Plug&Play fiind recunoscute automat de catre sistem.

Sistemul permite utilizarea a maximum 14 surse DC programabile in curent sau tensiune prin GPIB, de 7V/15A, 20V/8A, 60V/2.5A. Aceste surse pot fi conectate in serie sau paralel folosind instructiuni software si permit limitarea in curent sau in tensiune.

Subsistemul analogic ce permite generarea de semnale si masuratorile analogice se concentreaza in jurul placii de masura ICA. Pentru o stabilitate si o acuratete mare ICA-ul contine un modul cu referinte pentru auto calibrare si un software de calibrare automata la o variatie mai mare de 5° a temperaturii. Capacitatea de calcul este de maxim 100 000 de esantioane de semnal pe secunda si se asigura o sincronizare a masuratorilor analogice cu testele digitale.

Capabilitatile de masura mai importante ale cardului ICA (in circuit analog module) includ:

- Magistrala analogica cu 8 canale date simultane;

- Rezistivitate (R) domeniu: 0.1 la 30 Mohm;

- Capacitate (C) domeniu: 1pF la 10,000¾F;

- Inductivitate (L) domeniu: 10¾H la 1,000H;

- Sursa interna DC Voltage: programabila 0 -18V;

- Sursa interna DC Current: programabila, 0 - 500mA;

- Sursa de inalta tensiune 120V / 50mA High;

- Voltmetru: 0 - 200V;

- DC Ampermetru: 0 la 160mA;

- Frecventa de lucru programabila intre 15Hz -100kHz;

- Generator de unda sinusoidala, dreptunghiulara si triunghiulara;

- Detector Diferential / DVM / Digitizer;

- Posibilitate conectare instrumentatie externa la magistrala analogica prin 9 mufe BNC la cele 8 canale analogice folosite intern.

Alte tipuri de instrumente electronice ce pot fi adaugate in sistem ca si carduri optionale sunt:

. System Frequency/Time Meter (SFTM) are abilitatea de a masura frecventa si timpii in spectrul 100Hz - 100MHz;

. Deep Serial Memory (DSM) - permite inscrierea, verificarea, stergerea rapida a unei cantitati de date pana la 1GB. Este utilizata la programarea memoriilor flash si a microprocesoarelor;

. Clock/SyncTrigger (CST) - furnizeaza semnale de timp sau genereaza semnale de tact pentru placa de testare pana in 25MHz; sincronizeaza trimiterea/primirea vectorilor de test digitali sincronizeaza semnalele de ceas intern cu ceasul extern al placii electronice; contine circuite de semnalizare a 15 semnale de trigger concomitent.

Referitor la sistemul de masurare digital software-ul Teradyne GR Navigate 6.2.0 contine librarii ce descriu modelul comportamental al majoritatii circuitelor integrate digitale. Pentru a descrie modelul comportamental al unui circuit integrat utilizam secvente rapide de semnale digitale ce contin semnale de input ce trebuiesc furnizate si/sau nivele de iesire ce trebuiesc masurate la un nivel dat de timp. Acestia se numesc vectori de test digitali. Pentru a avea o functionare corecta a IC-ului testat trebuie sa facem izolarea electronica a acestuia fata de componentele din jur. Acest lucru se face automat de catre ATG (automatic test generator) ce suporta pana la 99 de nivele de izolare.

Un lucru important este ca se pot utiliza pana la 25 de familii de nivele logice simultan. De exemplu, in acelasi timp, la acelasi IC pot sa generez semnale si sa interpretez nivelele de iesire in logica de 1.2V, 1.8V, 3.3V si 5V, cu o frecventa de 5MHz. Mentionam ca o data cu generarea semnalelor digitale (drive) se face verificarea generarii lor (sense). O caracteristica importanta ce diferentiaza sistemele Teradyne de competitori este faptul ca putem programa curentul / timpul de backdriving.

Aceasta inseamna ca putem controla puterea disipata pe un pin si cu aceasta putem evita distrugerea circuitelor integrate in procesul de testare. In cadrul testelor digitale toti parametri (nivelele logice, panta de crestere a semnalului, timpii de lucru si curentii de backdriving) sunt programabili individuali pe pini. Cardurile de tip Ultrapin II pot sa aiba nu numai capabilitati analogice. Un mare avantaj este faptul ca aceste carduri se pot combina cu cardurile Ultrapin ce au capabilitati digitale in acelasi sistem. Astfel, clientul isi poate alege o configuratie flexibila. Fiecare card Ultrapin permite accesarea simultana a minim 128 de pini de test/noduri electrice.

3.3. Masina de Test in Circuit ICT

Testul 'In-circuit' (In-Circuit-Test = ICT) a fost introdus in procesele de productie la sfarsitul anului 1970. Metoda include un algoritm simplu de testare care identifica impedanta dintre nodurile electrice si punctele de test.

In procesul de test ICT exista doua aspecte: detectarea defectelor si izolarea defectelor, adica:

. Trebuie asigurat accesul spre toate componentele pe care dorim sa le testam. Totodata, pentru a putea testa fiecare componenta individual, testerul trebuie sa permita conectarea instrumentelor de test la terminalele fiecarei componente.

. Trebuie asigurata izolarea fiecarei componente intrate sub test din contextul interconexiunii componentelor. Pentru ca in mod obiectiv, componentele sunt interconectate pe circuitul imprimat, iar o tehnica speciala de izolare este necesara pentru a preveni afectarea testului de celelalte componente.

Pentru a intelege global fenomenele, este necesar sa ne familiarizam cu partile componente ale unui tester de acest tip si cu functiile acestuia.

Figura 1: Prezintarea schematica ICT 'In-circuit'

Figura 1 prezinta schematic un tester 'In-circuit' ,cuprinzand:

. Instrumente de test (Test instruments);

. Receptorul de semnal (Receiver);

. Adaptorul (Fixture);

. Patul de pini (Bed of nails);

. Circuitul imprimat testat (Unit-Under Test = UUT).

Pentru a accesa nodurile de circuit electric de pe PCB, testerul foloseste un adaptor special numit 'pat de pini'. Pinii sunt elastici, incorporand un arc, si au rolul de a realiza contactul efectiv cu traseele sau/si nodurile de componente de pe PCB. Pinii sunt montati intr-un soclu si sunt conectati la tester prin fire.

Fiecare PCB necesita adaptorul sau tipic. Acesta poarta pe el sute de pini de test aranjati in adaptor in asa fel incat sa vina in contact cu nodurile de circuit de pe PCB-ul testat. Inaintea fazei efective de test, PCB-ul este plasat cu fata echipata cu componente spre adaptor si este activat vacuum-ul.

In acest moment PCB-ul este coborat pe 'patul de pini'. In unele cazuri, pinii de test trebuie sa fie plasati pe ambele fete ale PCB-ului pentru ca distributia componentelor impune acest lucru. In aceasta situatie se foloseste un tip special de adaptor.

Elementul urmator este receptorul, interfata fizica dintre tester si adaptor.

Pentru a preveni posibile confuzii este necesar sa fixam cateva notiuni:

. PIN DE TEST (TEST NAIL) = se refera la elementele elastice din adaptorul de test care realizeaza contactul cu PCB - ul testat;

. NOD (NODE) = un punct pe circuit (sau traseu);

. PIN (PIN) = se refera la punctele de pe PCB accesate simultan in timpul testului. De exemplu, se spune ca un tester are in total 640 pini.

. TERMINAL

(LEAD) = uzual, se refera la conexiunile atasate unei componente. De exemplu, un condensator are 2 terminale, un IC-16 are 16 terminale, etc. Patul de pini realizeaza conectarea PCB - ului la tester. Mai departe este necesara conectarea la instrumentele de test. Acestea pot fi analoge sau digitale in functie de tipologia testului:

. sursa de curent continuu;

. voltmetru DC;

. sursa de tensiune alternativa;

. generator de semnale;

. sursa de tensiune continua;

. ampermetru;

. voltmetru AC.

Un tester poate avea aditional instrumente de test analoge care pot extinde capabilitatea acestor instrumente standard. Acum intrebarea este: cum poate testerul sa conecteze oricare din aceste instrumente la oricare din sutele de noduri de pe PCB

Definitii in procedura de test:

Node : nod - o locatie (pozitie) dintr-un circuit care este folosit ca un punct de test pentru masuratori electrice; de obicei este un test pad sau o via.

Nail : cui - un cui special de test cu arc inauntru folosit pentru a realiza contactul electric

Bed of Nails : pat de cuie - un set complet de cuie pe care o placa este asezata in fixture. Pot fi de asemenea cuiele aflate pe receiver (la ICT) care fac contact cu partea de dedesubt a fixture-lui.

Net : retea - o lista de componente sau parti de componete care sunt interconectate electric la un nod.

Dut : Device Under Test : componenta de testat

Guard : un punct de izolare electrica folosit in test pentru a elimina componentele aflate in paralel pe circuitul pe care se afla componenta supusa testarii.

Vector : un esantion de impulsuri digitale high si low injectat la intrarile unei componente digitale, si marimile asteptate high si low la iesirile componentei

Ict : In-Circuit Test

Fa : Failure Analysis: analiza a erorii

Nff : No Fault Found: nici un defect gasit

Ground Plane: parte metalizata a fixture-lui care serveste ca punct comun de masa pentru a reduce influentele generate de semnalele de test, creand o cale de intoarcere de impedanta mica.

Interface Board :placa ce contine 'mating contacts'.

Mating Contact :conectori electrici (puncte de contact) in fixture ce fac contact cu receiver-ul.

Nail Assignment Report : raport generat de sistem ce specifica ce cui de test este conectat la un nod si listeaza toate componetele ce au terminalele conectate la acel nod

Nail Fixture Report : raport generat de masina ce specifica ce cui de test este conectat la un terminal specificat al unei componente la un nod dat.

Pin : un terminal al unei componente prin care se pot face masurari electrice. La un nod pot fi conectate mai multe terminale ale componentelor.

Receiver : parte a interfatei dintre fixture si masina de test care este permanent atasata masinii.

Receiver Contact : conectori electrici in receiver care fac contact cu un punct de test de pe partea de dedesubt a fixture-lui

Test Fixture : un ansamblu ce asigura continuitatea electrica la nodurile UUT, conectand electric si mecanic receiver-ul si punctele de test ale placii de testat

Test Point : partea dintre un nod si receiver

Unit Under Test : componenta de pe o placa sau un modul ce urmeaza a fi testata

Component Hole : o gaura folosita pentru conectarea electrica a terminalului componentei cu restul placii

Component side: partea de sus a placii (top side) este cunoscuta ca si primary side (partea principala a placii). De obicei componentele ce se monteaza cu terminalele in gaurile placii (through hole=prin gauri) si cele care se monteaza la inceput pe placa se afla pe aceasta parte a placii.

Bottom side : Parte a placii opusa celei denumite top side, adesea denumita secondary side sau solder side.

Double sided board : o placa cu componente pe ambele parti

Internal layer : trasee conductoare care sunt incluse in totalitate in straturile interne ale placii

Jumper wire : o conexiune electrica cu fire care este parte a proiectarii, adaugata intre 2 puncte ala unei placi dupa ce traseele conductoare au fost formate.

Land ( pad ) : portiune din traseul conductor folosita pentru conexiuni electrice sau prinderi ale terminalelor componentelor.

Modification : o actiune in urma careia o functie electrica sau structura mecanica a produsului sunt

schimbate.

Multi-layered board :este un termen general pentru o placa cu circuite imprimate formata din straturi conductive si straturi izolatoare lipite intre ele, straturile conductoare fiind mai mult de doua si interconectate intre ele dupa cerintele clientului. Acest termen face referire atat la placile flexibile cat si la cele rigide.

Pin hole : o gaura micuta ce apare ca o imperfectiune ce strapunge un intreg strat

Pit : o gaura micuta ce apare ca o imperfectiune care nu strapunge intregul strat..

Single sided board : o placa cu strat conductor pe o singura parte

Solder side : La placile cu componente pozitionate pe o singura parte, solder side este partea opusa celei cu componente.

Surface Mounting : montarea si conectarea electrica a componentelor pe suprafata stratului conductor fara a folosi terminale care strapung placa prin gauri.

Via hole : gauri metalizate pe interior folosite pentru realizarea conexiunilor electrice in care nu vor intra terminale ale componentelor

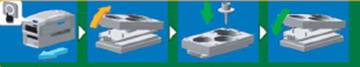

Etapele procesului prin care trece o placa la test

Figura 2: Etapele procesului

|

|

3.4. Masina de Test in Circuit ICT HP3070

Figura 1: ICT HP3070 UNIX

Figura 2: ICT HP3070 METALIST XP

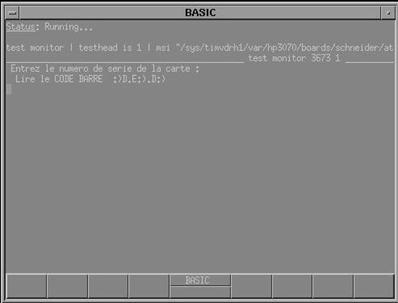

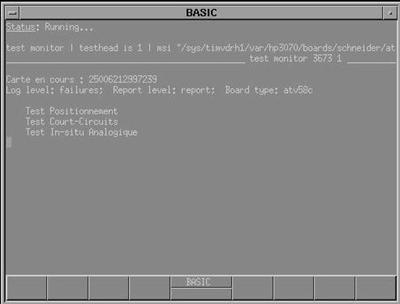

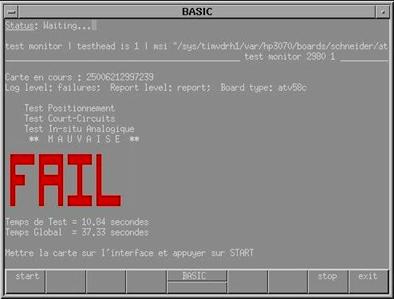

Pentru testare, se incarca placa in fixture, se apasa pedala sau tasta F1, dupa care se scaneaza placa in momentul in care pe ecran va aparea mesajul din Fig 2. In acest moment, testarea propriuzisa va incepe si se poate inchide capacul fixture-ului

Figura 3: Mesajul pentru scanarea placii in vederea testarii

Figura 4: Desfasurarea testarii

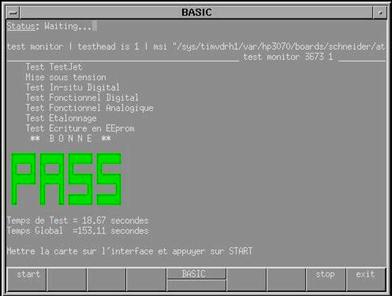

In cazul in care rezultatul testarii va fi PASS acest va fi afisat pe ecran Fig. 4. Placa PASS va fi marcata in modul descris in anexa corespunzatoare si va fi pusa in zona marcata ICT OUT.

Figura 5: Mesaj PASS

In cazul in care placa a fost FAIL Fig. 5, ea va fi retestata de maxim trei ori. In functie de rezultatul de la retestare placa va fi marcata PASS sau FAIL in modul descris in anexa corespunzatoare. Daca rezultatul final dupa retestare este FAIL, placa se va trimite la debug impreuna cu mesajul de fail listat de imprimanta ICT-ului si de eticheta F-09-0059 Fig. 6 pe care se va trece tipul de defect.

Figura 6: Mesaj FAIL

4.1. Prezentare IYET

Intelligent Randament Enhancement Test (IYET)

" sporirea inteligenta a randamentului de Test" (IYET)

IYET dinamic este o re-test de strategie care in mod automat re-testesteaza in lipsa "unpowered" teste Deoarece numai in lipsa unpowered testele sunt re-testate

Cu " IYET testplan" executa unpowered test la fel ca o testplan standard. In cazul in care un unpowered test nu reuseste "sporirea inteligenta a randamentului de Test"in testplan depoziteaza un raport tampon de la un fisier, acesta pentru ca nu testeaza cicluri de vid, ci re-testeaza numai masuratorile eronate "FAIL". Toate caracteristicile unui "standard testplan" (data-loguri, panouri, mai multe versiuni de bord, serii de eticheta, etc) sunt pastrate intact IYET ' sporirea inteligenta a randamentului de Test" face captura la re-testul cu esecul de date si afiseaza Re-testul pentru istoria masuratorii corective. In timp, aceasta poate duce la o mai buna fixare si de testare a performantei prin examinarea Re-testelor din istorie, apeluri false. Datorita acestui dispozitiv cele mai multe probleme de contact sau erori de debugged-teste pot fi identificate si corectate inainte ca acestea sa aiba un impact negativ in randamentul de test.

4.2. Crearea unui nou IYET Testplan

Aceasta procedura presupune ca am finalizat un tipic de testare in procesului de dezvoltare. dar inca nu am inceput procesul de de depanare al respectivului program.

Un nou testplan va fi creat si bazat pe unul din IYET testmains

Descarcam fisierul testmains.zip si dezarhivam IYET testmains.

testmains.zip

Un director numit 'testmains' vor fi create cu urmatoarele fisiere:

Copiati testmain adecvat pentru fisierul director in conformitate cu 'Ipg' director. Daca utilizati FTP pentru a copia in 'UX' testmains la o 3070UX sistem, asigurati-va pentru a utiliza 'ascii' ca metoda de transfer. Pentru multi-board, re-denumim Fisierul 'ipg / testmain_panel' in 'Ipg / testmain'.

generarea testplan off

la

genera testplan on

Din fereastra de BT-Basic - Din directorl baza al programului , se executa comanda:

Testplan generare

Un nou 'testplan' va fi scris utilizand testmain gasit in 'Ipg / testmain'. Acum, putem incepe normal testplan de depanare pentru proces.

Acest lucru va determina testplanului de a crea IYET testmains pentru toate directoarele bord dezvoltat pe acest sistem. Atentie, aceste fisiere vor fi suprascrise in timpul unei actualizare software.

Nou creat testplan contine indicatori suplimentari in subroutine

'Set_Custom_Options', care sunt utilizat pentru a controla IYET.

In mod implicit, IYET este oprit, astfel incat nu are active functiile " IYET testplan ",dar are active functiile unui " standard testplan."

Edit 'Set_Custom_Options'

Pentru a incepe sa utilizati de IYET, gasim subroutinele :

'Set_Custom_Options'.

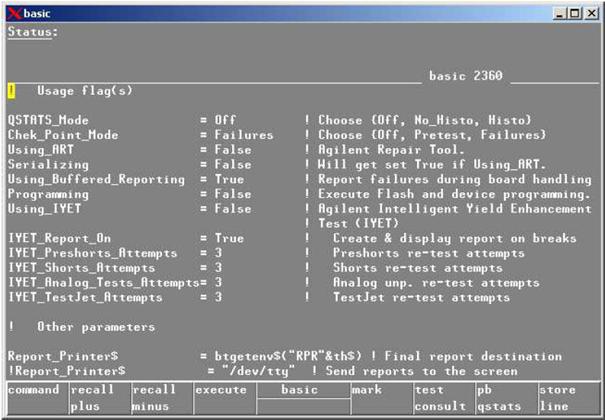

Figura 1:Caracteristicile IYET

Figura 1 BT-Basic de baza pentru utilizare IYET

Setati: 'Using_IYET' active va fi pe 'True'. IYET de utilizare a altor steaguri si parametri. Ele sunt rezumate in Tabelul 1 si pot fi modificate dupa cum dorim. Alte testplan-uri de utilizare si de parametri sunt neschimbate si pot fi editate dupa cum dorim. Exceptie este 'Chek_Point_Mode' care este descrisa in sectiunea

'IYET SUBROUTINE Descrierile '.

Tabelul 1

Descrierea IYET de utilizare steaguri si parametric

Dupa cum este descris mai sus. Activeaza IYET pentru testplan.

Afiseaza top 10 re-teste pentru ziua curenta de productie. Data Date vine de la re-test log fisier numit 'retest <date>. txt', in 'iyet ' director in cadrul fisierului director. Acest director este creat in cazul in care nu sunt prezente.

Controleaza numarul de incercari de re-test pentru lipsa teste in 'Preshorts' subroutine de testplan. Trebuie sa fie un intreg > = 1. Setarea egala cu 1 va determina 'Preshorts' subroutine de a fi executat doar o singura data, indiferent de esecuri, in mod eficient dezactivarea IYET pentru acest subroutine

Controleaza numarul de incercari de re-test pentru lipsa teste in 'scurt' subroutine de testplan. Trebuie sa fie un intreg> = 1. Setarea egala cu 1 va determina 'scurt' subroutine pentru a fi executat doar o singura data, indifferent de esecuri, in mod eficient dezactivarea IYET pentru acest subroutine.

IYET_Analog_Tests_Attempts

Controleaza numarul de incercari de re-test pentru lipsa teste in 'Analog_Tests' subroutine de testplan.Trebuie sa fie un intreg> = 1. Setarea egala cu 1 va determina 'Analog_Tests' subroutine a fi executat doar o singura data, indiferent de esecuri, in mod eficient dezactivarea IYET pentru acest subroutine.

IYET_TestJet_Attempts

Controleaza numarul de incercari de re-test pentru lipsa teste in 'TestJet' subroutine de testplan. Trebuie sa fie un intreg> = 1. Setarea egala cu 1 va determina 'TestJet' subroutine pentru a fi executat doar o singura data, indiferent de esecuri, in mod eficient dezactivarea IYET pentru acest subroutine.

Tabelul 1

IYET presupune ca fixturele poate fi actionat in mod corect, utilizand 'faon' si 'faoff' comenzi 1.5 secunde, cu o intarziere de fiecare. Daca nu, consultati sectiunea 'IYET SUBROUTINE descrierile ' pentru detalii cu privire la subroutines,

'IYET_Vacuum_On'

si

'IYET_Vacuum_Off'.

IYET executa re-testele individual. Asigurati-va ca testul pentru fiecare test va contine subroutine pass 'pe cont propriu'. Fereste-te pentru GPrelay la conexiuni, variabile, suplimentare 'Unpowered' declaratii, sau alte setarile care se afla in testplan, dar nu sunt in test sursa.

Odata activata, "IYET testplan" diferentele vor fi usor vizualizat fata de "standard testplan" .

In primul rand, mesajul de pornire va indica ca IYET este activata.

Figura 2 arata nou mesaj de pornire.

Figura 2: mesaj de initializare

Figura 2 BT-basic de ecran de pornire al IYET mesaj

Nota:

Noua linie de IYET mesaj evidentiate cu galben.

Daca pavilionul 'IYET_Report_On' este fals, atunci sirul, 'Raport' va fi disparut. Testplan creeaza un director numit 'iyet' in fisierul local daca in director nu este prezent. Mesajul de Fail si Re-test fisierele din jurnal sunt tinute in aceleasi locati.

Daca 'iyet' directorul este creat si lansat pentru prima data raportul de incercare nu va fi generate, chiar daca de pavilion 'IYET_Report_On' este adevarat (nu sunt date in director).

Figura 3: fluxul de test

Figura 3 BT-baza de screenshot IYET test pentru fluxul de test

Arata in BT-Basic fereastra pe durata normala de executare a testplan.

Nota :

Aatunci cand un unpowered test subroutine nu reuseste," Faoff" va fi actionat si va elibera fixturele In timpul acestei 'pauze' de timp, testplan este afisat. Esecul de teste este analizat si o lista de teste sunt create in lista.

Dupa un operator "start", "Faon" este pornit si esecuri sunt re-testate.

Nu comenta acest prompt cu exceptia cazului in care este aprobat un dispozitiv de actionare fara operator de interventie.

Vezi sectiunea 'IYET SUBROUTINE descrierile ' pentru detalii.

Figura 4: IYET fail raport de testare

Figura 4 BT-baza de screenshot IYET fail raport de testare

'IYET raport Teste Defecte', cu numarul total de reteste vine de la un fisier care figureaza in titlu, in acest caz, './iyet/retest050114.txt'. Fisiere sunt numite 'retest <date>. txt'.

Acest fisier este adaugat cu fiecare mesaj esec pentru data curenta. In cazul in care nu exista sau nu exista retest nici un dosar pentru data curenta, apoi acest ecran se afiseaza un mesaj, 'Nu a retest gasit sau lipsa fisier'. Fisierul este analizat si de top 10 instabilitate teste si sunt enumerate dea lungul testului pentru acea zi. Aceste dete de afisare trebuie sa fie utilizat pentru a face actiuni de corectare, de pe dispozitiv (inlocuire de sonde associate cu test, de exemplu) sau de test de revizuire a re-test fisierele jurnal program (a se adauga la 'ed' optiune pentru un zgomot de test, de exemplu). In timp, 'iyet' directorul se va umple cu aceste re-test log fisiere Utilizatorul poate vizualiza, copia si stergeti-le, dupa cum este necesar.

Aceasta sectiune ofera o prezentare detaliata a IYET testplans. Acesta este destinat pentru cei familiarizati cu BT-baza care au nevoie de ea pentru a adauga informatii la "IYET testplans" existent.

Testplans format din doua parti, test main si de testare subroutines.

De testplan scriitor copii de testmain in tinta fisierului director si adaugat de test subroutines. De IYET testmain este un editor testmain standard cu 7 subroutines (8 pentru Boarduri panelizate).De denumirile.

Conventionale pentru suplimentarele IYET cod sunt, dupa cum urmeaza:

Declaratiile sunt in interspersed de testmain si etichetat cu comment '! IYET". IYET '.

Tabelul 2 este o harta simplificata a unui singur bord IYET testplan.

Din text in albastru scoate in evidenta locatii de cod suplimentar daugat la un standard de testmain suport IYET.

Dimensiunea declaratii

Asteptati pentru a incepe bucla

Eroare si Break capcane

Subroutines

Test_Sections,

Reset_Board, Chek_Point_OK, Start_Logging, Get_Serial_Num $, Verify_Board_Names, IllegalChars_In_Board_Name, Create_Log_Queue, Setup_Logging,

Initializations, Print_Startup_Message, Get_Board_Revision, Do_Version_Inits, Get_Version_Label, Initialize_Constants,

Set_Custom_Options, Cleanup_Flash, Set_Log_LevelIYET Subroutines

|

Test Subroutines Caracterizeaza Preshorts, Analog_Tests, TestJet, Connect_Check, Polarity_Check |

Tabelul 2 IYET Testplan Harta

Fiecare dintre cele in albastru elementele din figura 5 este descris in detaliu mai jos:

Dimensiunea Declaratii

IYET necesita trei reluari la esecul procesului de test si de re-un raport de incercare in istorie. Ele au 40 de caractere, deoarece aceasta este limita de raportul de la imprimanta.

Ele sunt dimensionate in partea de sus a testplan ca urmeaza:

! IYET

print IYET_Failing_Tests $ (0:2047) [40]

print IYET_Retest_Failing_Devices $ (0:8191) [40]

print IYET_Top_Retests $ (0:8191,2) [40]

Sub Initializations

IYET este initializata la sfarsitul acestui subroutine. O declaratie de la nivel global, este necesara de asemenea

! IYET IYET

global Using_IYET

! IYET IYET

if Using_IYET apoi apel IYET_Initializare

Subend

Sub Print_Startup_Message

Urmatorul cod este utilizat pentru a imprima IYET pornire mesaj de la sfarsitul acestui subroutine. Un nivel global declaratia este, de asemenea, necesara.

! IYET

Using_IYET la nivel global, IYET_Report_On

! IYET IYET

O3 $ = ''

if Using_IYET then

O3 $ = O3 $ & 'Intelligent Yield Enhancement Test '

if IYET_Report_On apoi O3 $ = O3 $ & '-Raport'

end if

print O3 $

print using '2 /'

Subend

Sub Test_Sections (Single Board)

IYET lucrari de test cu subrutinele suna la 'Test_Sections' subroutine Retineti ca, de pavilion 'Using_IYET' este utilizat pentru apeluri direct de baza IYET subroutine pentru unpowered test subroutines 'Preshorts', 'scurt', 'Analog_Tests' si 'TestJet'.

In cazul in care nu este setat, acest subroutine se comporta ca un testplan standard.

'Analog_Tests' include, de asemenea, apel controale pentru a se asigura ca IYET nu este utilizat in timpul de invatare sau prelevare de probe. Acest lucru asigura ca re-test de date nu este corupt in fisierul data_logging.

! IYET

global Using_IYET, prelevarea de probe, IYET_Preshorts_Attempts

IYET_Shorts_Attempts la nivel global, IYET_Analog_Tests_Attempts, IYET_TestJet_Attempts

if Using_IYET apoi

call IYET (PreshortsMsg $, IYET_Preshorts_Attempts)

else

call Pre_Shorts (Failed_In_Preshorts, Mod PreshortsMsg & $ $)

add if

daca board failed apoi subexit

if Using_IYET then

call IYET (ShortsMsg $, IYET_Shorts_Attempts)

else

call Shorts (Failed_In_Shorts, Mod ShortsMsg & $ $)

end if,

if board failed apoi subexit

if Using_IYET, nu invata si nu Esantioneaza atunci

call IYET (AnalogMsg $, IYET_Analog_Tests_Attempts)

else

call Analog_Tests (Failed_In_Analog, Mod AnalogMsg & $ $)

end if,

if board failed apoi subexit

end if

if Using_IYET then

call IYET (TestJetMsg $, IYET_TestJet_Attempts)

else

call TestJet (Failed_In_TestJet, Mod TestJetMsg & $ $)

end if

if boardfailed apoi subexit

Sub Test_Sections (Panelized Board)

IYET lucrari de test cu subroutine apelate de la 'Test_Sections' cu subroutine.

Retinem ca, de fisierul 'Using_IYET' este utilizat pentru apelul direct de baza IYET subroutine pentru unpowered test subroutine 'Preshorts', 'scurt', 'Analog_Tests' si 'TestJet'. In cazul in care fisierul nu este setat, se comporta acest subroutine ca un standard testplan.Atunci 'Analog_Tests' include, de asemenea, apel controale pentru a se asigura ca IYET nu este utilizat in timpul de invatare sau prelevare de probe. Acest lucru asigura ca re-test de date nu este corupt in "datalogging".

! IYET

global Using_IYET, prelevarea de probe, IYET_Preshorts_Attempts

IYET_Shorts_Attempts la nivel global, IYET_Analog_Tests_Attempts, IYET_TestJet_Attempts

if Using_IYET then

call IYET (PreshortsMsg $, IYET_Preshorts_Attempts)

else

call Pre_Shorts (Failed_In_Preshorts, Mod PreshortsMsg & $ $)

end if

if All_Failed apoi subexit

if Using_IYET then

call IYET (ShortsMsg $, IYET_Shorts_Attempts)

else

call Shorts (Failed_In_Shorts, Mod ShortsMsg & $ $)

end if

if All_Failed apoi subexit

if Using_IYET, si nu de invatare si de atunci nu Esantionarea

call IYET (AnalogMsg $, IYET_Analog_Tests_Attempts)

else

call Analog_Tests (Failed_In_Analog, Mod AnalogMsg & $ $)

end if

if All_Failed apoi subexit

end if

if Using_IYET apoi

call IYET (TestJetMsg $, IYET_TestJet_Attempts)

else

call TestJet (Failed_In_TestJet, Mod TestJetMsg & $ $)

end if

if All_Failed apoi subexit

Sub Update_Status (Panelized Board)

Pentru paneluri IYET, se foloseste, de subroutine 'Update_Status', acestea trebuie sa fie passed in timpul re-test succesiune si re-executat la sfarsitul celei de-a re-test de succesiune.

Acest lucru se realizeaza prin urmatoarele:

Cod:

! IYET

global IYET_Skip_Update_Status

if IYET_Skip_Update_Status then subexit

IYET Subroutine Descrieri

Acesta este un nivel inalt descriere in IYET subroutines. In cele mai multe cazuri, nu vom avea nevoie sa modificam aceste subroutine. Ele sunt descrise aici ca referinta.

Sub IYET_Initialize

Aceasta subrutina se apeleaza la inceputul incarcarii testplan_ului pentru a initializa caile, imagini, mesaje si constantele folosite de IYET. Este apelat de fiecare data cand testplan este difuzat. Directorul apelat, numit 'iyet' este creat in fisierul director, in cazul ca aceasta nu este prezent. Acest director va fi folosit pentru a depozita cele doua fisiere;

curent esec bilet ( 'failure.txt'), precum si o re-test fisier jurnal ( 'retest <today's date>. txt').

Re-test log. include ziua si data cu numele sau. Actualul esec bilet este de adaugat la acest fisier pentru fiecare re-test de succesiune. Astfel, re-test log pastreaza toate mesajele esec bilete pentru o anumita zi. In timp, aceast director se va umple cu re-test fisierele jurnal. Utilizatorul poate vizualiza, copia si sterge aceste fisiere dupa cum este necesar.

In cazul in care fisier 'IYET_Report_On' este activ, atunci subroutine 'IYET_Create_Report' este denumit (a se vedea mai jos). IYET va da ciclu de "faoff-faon" intre reteste. De intarziere pentru "faoff-faon" in miscare de eliberare si sunt controlate de catre 2 parametri:

'IYET_Vacuum_Off_Delay'

Si

'IYET_Vacuum_On_Delay'.

Acestea sunt stabilite la 1,5 secunde si poate fi ajustata. IYET va modifica comportamentul Chek-Point (cu 'pin' test). In cazul in care testplan apeleaza 'Chek_Point_Mode' este setat la 'erori', apoi IYET va seta 'Max_Times_To_Fix_Contact' la 1. Din "faoff-faon" este ciclu de IYET pe retest, previne acest vid cicluri suplimentare in cazul in care 'mesajul' de test este difuzat. Chek-Point este nemodificat in cazul in care 'Chek_Point_Mode' este 'off' sau 'Pretest'.

Sub IYET_Create_Report

In cazul in care 'IYET_Report_On' este activata, atunci acest lucru se numeste subroutine la inceputul urmatoarei testari si afiseaza top 10 re-testate teste curente de la re-test de fisier de log. Numarul de teste afisata este controlat de de 'IYET_Max_Report_Count' parametru si poate fi ajustata. Daca nu sunt re-teste sau fisierul nu exista, apoi un mesaj de avertizare va fi afisat. Re-test de fisier de log este numit cu ziua curenta. Astfel, numai in re-test de istorie pentru ziua curenta este afisate. Daca nu sunt re-teste sau fisierul nu exista, atunci un mesaj de avertizare va fi afisat.

Sub IYET_Vacuum_Off, IYET_Vacuum_On

Acest control vacuum actioneaza in timpul IYET re-test succesive.

Aceste rutine presupune ca pentru vid de dispozitiv este controlata utilizand:

'faon'

si

'faoff'

ca si comenzi.

Daca utilizati alte pause de comenzi ( 'fbon / fboff') vom edita aceste rutine, sa fim constienti de faptul ca procesele de IYET re-test esecul de date in timpul de intarziere pentru vid versiune. In 'IYET_Vacuum_Off' subroutine, de parametru 'IYET_Start_Vacuum_Off' este setat la curent 'msec'. Aceasta este, la randul sau, trecuta la 'IYET_Vacuum_On' subroutine si utilizata pentru a pune in aplicare 'IYET_Vacuum_Off_Delay'. 'IYET_Vacuum_On' subroutine va solicita operatorului inainte de a actiona pauza de vid in timpul re - Secventa de testare, utilizand urmatoarea linie de cod:

Intrebare: IYET_Cont_Msg $,

Continuati | daca nu Continuati stop

Sub IYET (TestType $, Maximum_Number_Attempts)

Acesta este nucleul subroutine pentru IYET. In cazul in care pavilion 'Using_IYET' este stabilit, aceasta se numeste de la testplan subroutine 'Test_Sections' in loc de apeluri normale de la

'Analog_Tests' include, de asemenea, apeluri controlate pentru a se asigura ca IYET nu este utilizat in timpul de invatare sau prelevarea de probe. Acest lucru asigura ca re-test de date nu este corupt datalogging. Acest lucru contine subroutinele urmatoarele:

Verificari, ca 'Maximum_Number_Attempts' este mai mare sau egala cu 1 runde si la cel mai apropiat integer. Variabila 'Retests_Remaining' este acum setat la 'Maximum_Number_Attempts'.

Este restaurat la nivelul corect, inainte de ultima re-test secventa de apel in subroutine, 'Cleanup_Flash'.

Testul subroutine ( 'Preshorts', 'Shorts', 'Analog_Tests', 'TestJet') este alelat pentru prima data, 'TestType $'.

Variabila, 'Retests_Remaining' este decrementat.

Re-test bucla este acum la intrare si are urmatorul text:

Iesirile in cazul in care test initial subroutine trece.

Iesirile in cazul 'Retests_Remaining' = 0

Se stinge vid, apeluri 'IYET_Get_Failed_Tests', se transforma pe vid.

Iesirile in cazul 'IYET_Get_Failed_Tests' returneaza un 'Abort' pavilion.

Daca 'Retests_Remaining' = 1, restabileste logare de apel 'Cleanup_Flash'.

Apeluri 'IYET_Retest_Failed_Tests'. Aceastea re-testeaza toate testele esuate.

Decrements 'Retests_Remaining'.

Dupa re-test bucla, unde Curatarea se face inainte de a iesind din subroutine.

Restaurare de logare de apel 'Cleanup_Flash'.

Daca tamponul de raportare a fost initial off, dump raportul tampon (e) de a opri tamponul de raportare.

IYET executa re-testate de test individual.

Sub IYET_Get_Failed_Tests (IYET_Abort)

Acest lucru are subroutinele urmatoarele:

Salveaza esecul bilet la un esec fisier si adauga-l la re-test de fisier de log.

Daca nu exista in lista de test sau nu arecapacitate de compensare trebuie sa fie invatat, atunci 'IYET_Abort' pavilion este setat In cazul in care 'IYET_Abort' nu este stabilit, atunci raportul tampon (e) si esecul pavilion (e) sunt sterse.

6. Concluzii

6.1. Avantaje ale aplicatiei

6.2. Dezavantaje ale aplicatiei

Uzura cuielor de test. Daca un cui de test este garantat pentru 45000-50000 de actionari, acestea au o uzura suplimentara in cazul unui retest la bordurile multiple la panel deoarece se actioneaza toate cuiele de pe fixturele de test

Uzura Fixturelui de test. Prin apelari repetate ale vacumului la fa-on / fa off

Uzura PCB_urilor. Actionarile multiple ale punctelor de test de pe PCB duc la uzura acestora

Informatii incorecte despre un PCB. In SITEQ un PCB este vazut ca si PASS din prima testare chiar daca aceasta a fost retestata.

7. Bibliografie

Constructia si tehnologia echipamentelor radioelectronice, Autori:Rodica Strugaru,Vasile Catuneanu

Introducere in arhitecturi paralele si neconventionale, Autor: Mircea Popa

Issues on Developing Real-Time Control Applications, Autori: V.Groza, Vladimir-Ioan Cretu, D.Zmaranda

Limbaju C -elemente fundamentale, Autor: Titus Slavici, Serban Popa

5. PCB Primer, Autor : Don Ecker (EE Services)

6. Tehnici fundamentale de programare, Autor: Horia Ciocarlie

7. www.agilent.com/go/manufacturing

8. https://www.home.agilent.com /upload/cmc_upload/All/05_31 _E4000i300_unixsys.book.pdf

9. https://www.home.agilent.com/ agilent/facet.jspx?cc=US&lc=eng&k= unix&sm=g&c=152893.i.0

10. https://www.fuji.co.jp/e/SMT/index.html

12. https://www.zibb.com /electronics/theme/semiconductor-equipment/ Fuji+QP-242E

Anexa A. Parte aplicativa (se muta la final dupa biblio)

A.1 Initializari testplan

sub Test_Sections

global PreshortsMsg$, ShortsMsg$, PowerMsg$, DigitalMsg$, AnalogMsg$

global Status(*), Failed_In_Preshorts, Failed_In_Shorts, Failed_In_Functional

global Logging, Number_Boards_On_Panel, True, False, BoardSet(*)

global TestJetMsg$, Failed_In_TestJet

global PolarityMsg$, Failed_In_Polarity_Check

global All_Failed

! IYET

global Using_IYET, Sampling, IYET_Preshorts_Attempts

global IYET_Shorts_Attempts, IYET_Analog_Tests_Attempts, IYET_TestJet_Attempts

if Using_IYET then

call IYET (PreshortsMsg$, IYET_Preshorts_Attempts)

else

call Pre_Shorts (Failed_In_Preshorts, Mode$ & PreshortsMsg$)

end if

if All_Failed then subexit

unpowered

if Using_IYET then

call IYET (ShortsMsg$, IYET_Shorts_Attempts)

else

call Shorts (Failed_In_Shorts, Mode$ & ShortsMsg$)

if All_Failed then subexit

unpowered !SLR

!if panelfailed then subexit !SLR