| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Arhitectura familiei PIC16F8x

Performantele familiei PIC16F8x se datoreaza, in primul rind, arhitecturii.

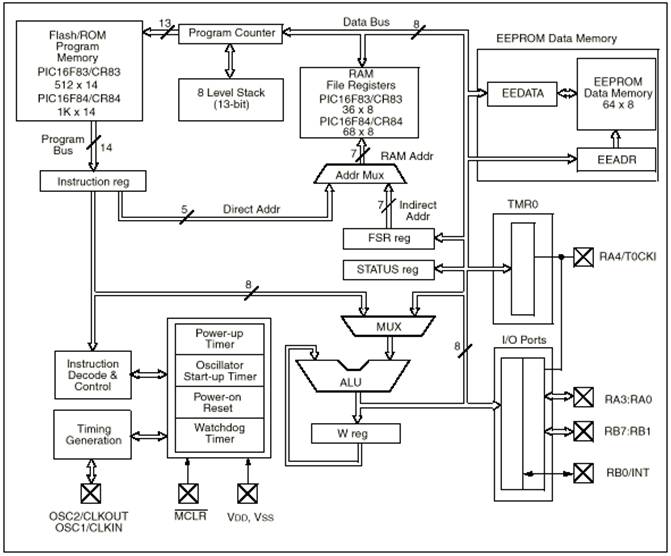

S-a adoptat o arhitectura RISC de tipul Harvard. Aceasta arhitectura foloseste doua tipuri distincte de memorie: memoria program si memoria de date. Astfel, exista doua magistrale distincte: magistrala de memorie program ( 14 biti ) si magistrala de memorie de date ( 8 biti ). In plus, fiecare tip de memorie are propria magistrala de adrese, permitandu-se transferul. de date de la memoria program la memoria de date.

Avantajul acestei arhitecturi consta in faptul ca ciclurile fetch si ciclurile de executie ale instructi-unilor pot fi suprapuse, prin folosirea unei structuri de tipul "two-stage pipeline", ceea ce inseamna ca urmatoarea instructiune poate fi adusa din memoria program in timp ce instructiunea curenta este executata. Prin urmare toate instructiunile sunt executate doar pe perioada unui singur ciclu masina (4Clk), exceptind doar instructiunile de ramificare care necesita ( pentru executie ) doua cicluri masina.

Observatie: pipelining = metoda de aducere, decodare si executie a instructiunilor, unde, in orice moment, diverse instructiuni de program se gasesc in diferite stadii de aducere decodare sau executie. Ideal, aceasta metoda accelereaza durata de executie asigurand ca microprocesorul sa nu astepte in momentul cand incheie executia instructiunii curente, urmatoarea instructiune fiind gata deja pentru decodare si executie.

Observatie: Acest tip de arhitectura conduce la o viteza de lucru mult mai mare fata de o arhitectura traditionala von Neumann ce are un singur tip de memorie care contine atit codul cit si datele. In acest caz exista o singura magistrala de adrese si o singura magistrala de memorie care este folosita atit pentr aduce-rea instructiunilor din memorie cit si pentru citirea / inscrierea datelor din / in memorie.

PIC16F83 si PIC 16CR83 adreseaza 512 locatii ( pe 14 biti ) de memorie program interna.

PIC16F84 si PIC 16CR84 adreseaza 1024 locatii ( pe 14 biti ) de memorie program interna.

PIC16Fxx poate acccesa direct sau indirect atit registrele de uz general ( File Registers ) cit si registrele cu functii speciale ( Special Function Register ) care sunt mapate in memoria de date de tipul SRAM. De notat ca si registrul PC ( program counter ) este mapat in memoria de date.

Setul simetric ( ortogonal ) de instructiuni face posibila executarea oricarei operatii asupra oricarui registru, folosind oricare mod de adresare.

PIC16Fxx contine un ALU pe8 biti si un registru de lucru pe 8 biti ( acumulator ), notat W. ALU este o unitate aritmetico-logica de uz general care executa operatii logice si aritmetice intre continutul registrului W si continutul oricarui alt registru ( file register ) mapat in memoria de date.

ALU poate realiza o gama larga de operatii aritmetice ( adunarea, scaderea, deplasari ) si logice ( OR, XOR, . etc ).

In cazul instructiunilor cu doi operanzi, in mod tipic, un operand este registrul W iar celalalt este un file register sau o constanta imediata.

In cazul instructiunilor cu un singur operand, acesta poate fi registrul W sau un file register.

In functie de operatia executata si in functie de rezultatul obtinut, ALU modifica valoarea flagurilor de stare din cadrul registrului de stare, notat cu STATUS.

Figura 3-1: Diagrama bloc pentru 16F8x

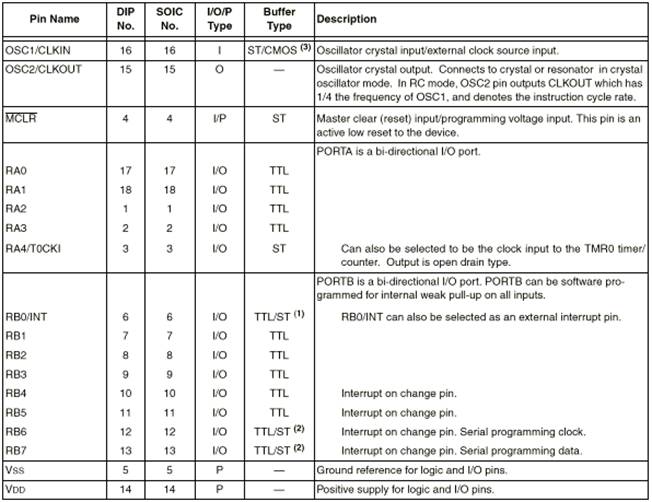

Tabelul 3-1: Asignarea pinilor pentru PIC 16F8x

1. Descrierea ciclului instructiune

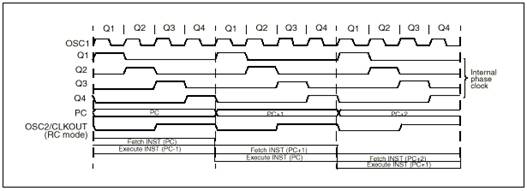

Semnalul de Clk, aplicat pe pinul OSC1, este divizat intern in 4 semnale distincte, identice ca forma de unda dar defazate cu 90 unul fata de altul, notate Q1, Q2, Q3, Q4.

Intern, registrul PC ( Program Counter ) este incrementat cu 1 pe parcursul lui Q1, dupa care instructiunea este adusa din memoria program si este zavorita in IR ( Instruction Register ) pe parcursul lui Q4. Pe parcursul urmatorului ciclu Q1-Q2-Q3-Q4 instructiunea adusa anterior va fi executata in paralel cu aducerea unei noi instructiuni din memoria program.

Fig 3-2: 4Clk / Ciclu masina

Functionarea structurii "pipeline"

Dupa cum am vazut anterior, durata de executie a unei instructiuni este de 1 ciclu masina ( 4 Clk )

datorita faptului ca operatiile de aducere si de executie ale unei instructiuni sunt "inlantuite".Astfel, operatia de aducere se deruleaza de-a lungul un ciclu masina iar operatia de executie se deruleaza de-a lungul urmatorului ciclu masina. Totusi, datorita structurii pipeline cu 2 stadii fiecare instructiune este efectiv executata doar pe parcursul unui singur ciclu masina.

Observatie: Daca o instructiune ( GOTO ) determina modificarea continutului registrului PC, atunci sunt necesare doua cicluri masina pentru executia primei instructiuni ce se gaseste la noua adresa deoarece structura pipeline a fost "golita" prin efectuarae saltului.

Un ciclu fetch incepe cu Q1 prin incrementarea cu 1 a registrului PC.

Un ciclu de executie incepe tot cu Q1 pe parcursul caruia instructiunea adusa anterior din memorie este zavorita in registrul IR. Aceasta este apoi decodificata si executata pe parcursul lui Q2, Q3 si Q4.

Memoria de date este citita ( citire operand ) pe parcursul lui Q2 si inscrisa ( inscriere operand ) pe parcursul lui Q4.

Exemplul 3-1 Executia inlantuita a instructiunilor

Copyright © 2025 - Toate drepturile rezervate