| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Aplicatii Verilog.

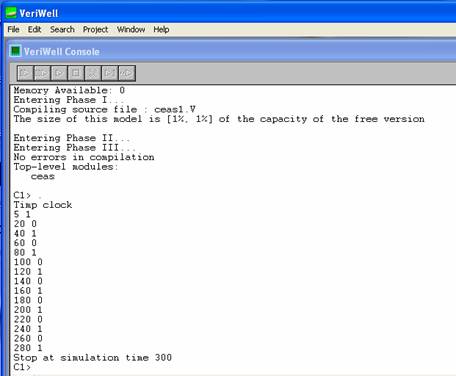

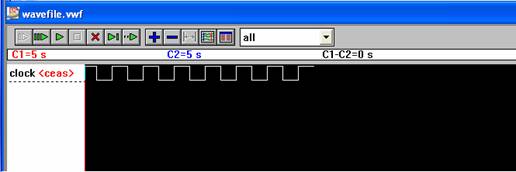

1. Exemplu de model de descriere pentru un ceas

// Ceas.

module ceas(clock);

output clock;

reg clock;

time timp;

initial begin: stop_at

#300; $stop;

end

initial begin

#5; clock = 1;

$display('Timp clock');

$monitor('%0d %b', $time, clock);

$vw_dumpvars();

$vw_group('all', timp,clock);

end

always begin: main_process

#20; clock = ~clock;

end

endmodule

2. Exemple de modele de descriere pentru un bistabil bazat pe circuite Nand

// Bistabil bazat pe circuite Nand

module ffNand;

wire q, qBar;

reg preset, clear;

nand #1

g1(q,qBar,preset),

g2(qBar,q,clear);

initial

begin

$monitor($time,,

'preset = %b clear=%b q=%b qBar=%b',

preset , clear, q, qBar);

$vw_dumpvars();

$vw_group('all',preset,clear,q,qBar);

//Forme de unda

#10;preset=0; clear=1;

#10;preset=1;

#10;clear=0;

#10;clear=1;

#10;$stop;

end

endmodule

3. Exemple de atribuiri

3.1. Atribuire nonblocanta.

module atr_nonbloc;

reg a,b,clk;

always @(posedge clk) begin

a <= b;

b <= a;

end

initial begin

clk = 0; a = 0; b = 1;

#10 clk = 1;

#10 $display('a=%d b=%dn',a,b);

$finish;

end

endmodule

Rezultatul executiei: a=1 b=0

3.2. Atribuire blocanta.

module atr_bloc;

reg a,b,clk;

always @(posedge clk) begin

a = b;

b = a;

end

initial begin

clk = 0; a = 0; b = 1;

#10 clk = 1;

#10 $display('a=%d b=%dn',a,b);

$finish;

end

endmodule

Rezultatul executiei: a=1 b=1

3.3. Interschimb blocant

module intersch_bloc;

reg a,b,clk;

always @(posedge clk) a = b;

always @(posedge clk) b = a;

initial begin

clk = 0; a = 0; b = 1;

#10 clk = 1;

#10 $display('a=%d b=%dn',a,b);

$finish;

end

endmodule

Rezultatul executiei: a=1 b=1

Interschimb nonblocant

module intersch_nonbloc;

reg a,b,clk;

always @(posedge clk) a <= b;

always @(posedge clk) b <= a;

initial begin

clk = 0; a = 0; b = 1;

#10 clk = 1;

#10 $display('a=%d b=%dn',a,b);

$finish;

end

endmodule

Rezultatul executiei: a=1 b=0

Interschimb nonblocant-blocant

module intersch_nonbloc_bloc;

reg a,b,clk;

always @(posedge clk) begin

a <= b;

b = a; // consistenta ?!

end

initial begin

clk = 0; a = 0; b = 1;

#10 clk = 1;

#10 $display('a=%d b=%dn',a,b);

$finish;

end

endmodule

Rezultatul executiei: a=1 b=0

4. Exemple de modele de descriere pentru un demultiplexor 2-la-4

// Demultiplexor 2-la-4 cu iesiri active pe nivel coborat

// model structural

module demux1(a,b,enable,z);

input a,b,enable;

output [3:0] z;

wire abar,bbar; // semnale locale

not v0(abar,a), v1(bbar,b);

nand n0(z[0],enable,abar,bbar);

nand n1(z[1],enable,a,bbar);

nand n2(z[2],enable,abar,b);

nand n3(z[3],enable,a,b);

endmodule

// Demultiplexor 2-la-4 cu iesiri active pe nivel coborat

// model 'flux de date'

module demux2(a,b,enable,z);

input a,b,enable;

output [3:0] z;

assign z[0] = ~(enable & ~a & ~b); // sau: |;

assign z[1] = ~(enable & a & ~b);

assign z[2] = ~(enable & ~a & b);

assign z[3] = enable ? ~(a & b) : 1'b1;

endmodule

// Demultiplexor 2-la-4 cu iesiri active pe nivel coborat

// model comportamental

module demux3(a,b,enable,z);

input a,b,enable;

output [3:0] z;

reg [3:0] z; // nu este chiar registru!

always @(a or b or enable)

case ()

default: z = 4'b1111;

3'b100: z = 4'b1110;

3'b110: z = 4'b1101;

3'b101: z = 4'b1011;

3'b111: z = 4'b0111;

endcase

endmodule

module principal_test;

reg a,b,enable;

wire [3:0] s_z,fd_z,c_z;

initial begin

// antetul de afisare.

$display('a b enable s_z fd_z c_z');

// afiseaza valorile A, B, C in cazurile in care acestea se modifica.

$monitor(' %b %b %b %b %b %b',a, b, enable, s_z, fd_z, c_z );

end

initial begin

enable = 0; a = 0; b = 0;

#10 enable = 1;

#10 a = 1;

#10 a = 0; b = 1;

#10 a = 1;

#10 enable = 0;

#60 $finish;

end

demux1 structural(a,b,enable,s_z);

demux2 dataflow(a,b,enable,fd_z);

demux3 behavioral(a,b,enable,c_z);

endmodule

Rezultatele compilarii si executiei:

This is a free version of the VeriWell for Win32 Simulator

Distribute this freely; call 1-800-VERIWELL for ordering information

See the file '!readme.1st' for more information

Copyright (c) 1995 Wellspring Solutions, Inc.

All rights reserved

Memory Available: 0

Entering Phase I

Compiling source file : DEMUX.V

The size of this model is [4%, 3%] of the capacity of the free version

Entering Phase II

Entering Phase III

No errors in compilation

Top-level modules:

main

C1> .

a b enable s_z fd_z c_z

0 0 0 1111 1111 1111

0 0 1 1110 1110 1110

1 0 1 1101 1101 1101

0 1 1 1011 1011 1011

1 1 1 0111 0111 0111

1 1 0 1111 1111 1111

Exiting VeriWell for Win32 at time 110

0 Errors, 0 Warnings, Memory Used: 54781

Compile time = 0.0, Load time = 0.0, Simulation time = 0.0

Normal exit

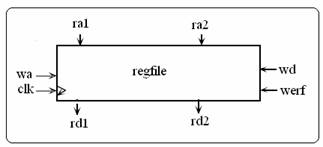

5. Exemplu de modul Fisier de Registre Generale: 32 cuvinte x 32 de biti, port 1 de intrare, 2 porturi de iesire

/* Fisier de Registre Generale: 32 locatii, 1 port de intrare, 2 porturi de iesire, iesirea activa pe frontul cazator al semnalului de ceas*/

module regfile(ra1,rd1,ra2,rd2,clk,werf,wa,wd);

input [4:0] ra1; // adrese pentru portul de citire 1

output [31:0] rd1; // date citite de la portul 1

input [4:0] ra2; // adrese pentru portul de citire 2

output [31:0] rd2; // date citite de la portul 2

input clk;

input werf; // activare scriere pe nivel ridicat

input [4:0] wa; // adrese pentru portul de scriere

input [31:0] wd; // date pentru scriere

reg [31:0] registers[31:0]; // fisierul de registre generale

// caile de citire sunt combinationale

assign rd1 = registers[ra1];

assign rd2 = registers[ra2];

// portul de scriere este activ atunci cand werf este pw nivel ridicat

always @(posedge clk)

if (werf) registers[wa] <= wd;

endmodule

6. Exemplu de modul pentru calculul celui mai mare divizor comun (cmmdc).

/* calculeaza cmmdc pentru numerele XI[15:0], Y[15:0], activeaza RESET pentru initializare, apoi se dezactiveaza pentru a incepe executia. DONE este activat atunci cand raspunsul este disponibil de la modulul CMMDC[15:0] */

This is a free version of the VeriWell for Win32 Simulator

Distribute this freely; call 1-800-VERIWELL for ordering information

See the file '!readme.1st' for more information

Copyright (c) 1995 Wellspring Solutions, Inc.

All rights reserved

Memory Available: 0

Entering Phase I

Compiling source file : cmmdc1.V

The size of this model is [3%, 3%] of the capacity of the free version

Entering Phase II

Entering Phase III

No errors in compilation

Top-level modules:

principal

C1> .

cmmdc= z done=z x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= x done=0 x= 27 y= 15

cmmdc= 3 done=1 x= 27 y= 15

Exiting VeriWell for Win32 at time 75

0 Errors, 0 Warnings, Memory Used: 45218

Compile time = 0.0, Load time = 0.0, Simulation time = 0.0

Normal exit

Thank you for using VeriWell for Win32

Copyright © 2025 - Toate drepturile rezervate