| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Codificator

Codul

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this codificator1e.

--library UNISIM;

--use UNISIM.VComponents.all;

entity codificator1 is

Port ( EI_L : in STD_LOGIC;

I_L : in STD_LOGIC_VECTOR (7 downto 0);

EO_L, GS_L : out STD_LOGIC;

A_L : out STD_LOGIC_VECTOR (2 downto 0));

end codificator1;

architecture Behavioral of codificator1 is

signal EI: STD_LOGIC; -- versiuni active H ale intr?rilor

signal I: STD_LOGIC_VECTOR (7 downto 0);

signal EO, GS: STD_LOGIC; -- si ale ie?irilor

signal A: STD_LOGIC_VECTOR (2 downto 0);

begin

process (EI_L, I_L, EI, EO, GS, I, A)

variable j:integer range 7 downto 0;

begin

EI <= not EI_L; -- conversia intr?rii

I <= not I_L; -- conversia intr?rilor;

EO <= '0';

GS <= '0' ;

A <= '000' ;

if (EI) = '0' then EO <= '0' ;

else for j in 7 downto 0 loop

if I(j) = '1' then

GS <='1'; EO <= '1'; -- prima linie din tabelul de adev?r

A <= CONV_STD_LOGIC_VECTOR (j,3);

exit;

end if;

end loop;

end if;

EO_L <= EO; -- conversia ie?irii

GS_L <= GS ; -- conversia iesirii

A_L <= A ; -- conversia ie?irilor

end process;

end Behavioral;

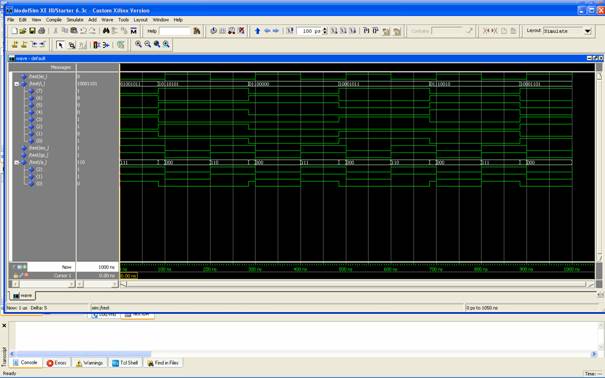

Afisarea rezultatelor simularii

|

Politica de confidentialitate |

Copyright © 2025 - Toate drepturile rezervate