| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Automatul More

Codul

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity MOORE is

port (X, CLOCK: in std_logic;

Z: out std_logic );

end MOORE;

architecture Behavioral of MOORE is

type STATE_TYPE is (S0, S1,S2,S3);

signal CURRENT_STATE, NEXT_STATE: STATE_TYPE;

begin

-- Proces pentru sec?iunea combinationala

COMBIN: process (CURRENT_STATE,X) begin

case CURRENT_STATE is

when S0 =>

if X = '0' then

Z<= '0';

NEXT_STATE <= S0;

else

Z<= '1';

NEXT_STATE <= S2;

end if;

when S1 =>

if X = '0' then

Z<= '0';

NEXT_STATE <= S0;

else

Z<= '0';

NEXT_STATE <= S2;

end if;

when S2 =>

if X = '0' then

Z<= '1';

NEXT_STATE <= S2;

else

Z<= '0';

NEXT_STATE <= S3;

end if;

when S3 =>

if X = '0' then

Z<= '0';

NEXT_STATE <= S3;

else

Z<= '1';

NEXT_STATE <= S1;

end if;

--toate starile curente

end case;

end process COMBIN;

-- Proces pentru sec?iunea secven?iala (bistabile)

SYNCH: process begin

wait until CLOCK'event and CLOCK ='1';

CURRENT_STATE <= NEXT_STATE;

end process SYNCH;

end architecture;

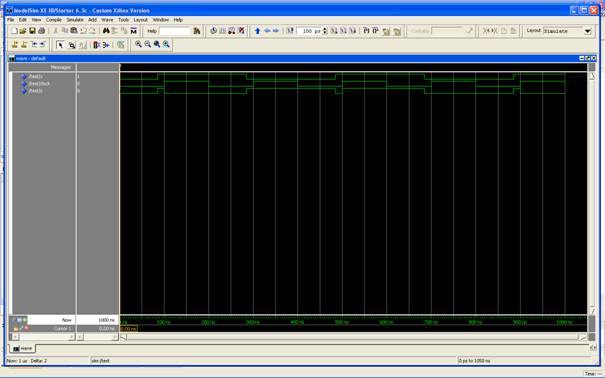

Afisarea rezultatelor simularii

|

Politica de confidentialitate |

Copyright © 2025 - Toate drepturile rezervate