| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Adunare

Codul

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity adunare is

port (A,B:in std_logic_vector (3 downto 0 ) ; -- doua intr?ri de cate 4 biti

CIN:in std_logic; -- intrarea de transport

C: out std_logic_vector (3 downto 0) ; --? rezultatul pe 4 biti

CAR_OUT :out std_logic ); --? ie?irea de transport

end adunare;

architecture Behavioral of adunare is

begin

P1:process(A,B,CIN)

variable PADDED_CIN: std_logic_vector (3 downto 0);

variable A_UNSIGNED: UNSIGNED(3 downto 0);

variable C_UNSIGNED: UNSIGNED(4 downto 0);

variable temp: std_logic_vector(4 downto 0);

begin

A_UNSIGNED := UNSIGNED(A);

PADDED_CIN := '000'&CIN ; --? concatenarea lui CIN cu 000

C_UNSIGNED := CONV_UNSIGNED(A_UNSIGNED,5 ) + UNSIGNED(B) +

UNSIGNED(PADDED_CIN);

C <= CONV_STD_LOGIC_VECTOR (C_UNSIGNED,4) ;

temp := CONV_STD_LOGIC_VECTOR (C_UNSIGNED,5); ---- se ob?ine din C_UNSIGNED

CAR_OUT <= temp(4);

end process;

end Behavioral;

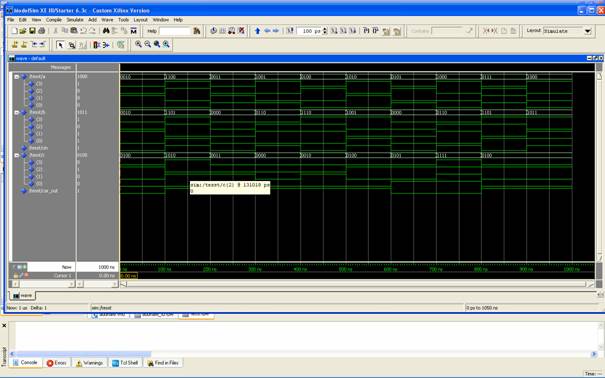

Afisarea rezultatelor simularii

|

Politica de confidentialitate |

Copyright © 2025 - Toate drepturile rezervate