| Aeronautica | Comunicatii | Constructii | Electronica | Navigatie | Pompieri |

| Tehnica mecanica |

T.P.C.L.P.

Tema de proiect

Tema nr. 9

Urmatoarea organigrama ASM reprezinta o masina de stare:

Se cere sa se:

a) Gaseasca blocurile ASM si conexiunile de stare si sa se construiasca tabelul de stare asociat masinii de stare descrise

b) Proiecteze masina de stare utilizandu-se bistabili de tip D. Sa se implementeze Generatorul Noii Stari (GNS) utilizandu-se un singur etaj de multiplexoare iar pentru implementarea Logicii Combinationale a Iesirilor (LCE) se vor utiliza porti logice. Este necesara minimizarea lui GNS utilizandu-se tehnica VID (Variabile Incluse in Diagrama). Sa se deseneze o schema de conexiune / electrica / de montaj a ASM-lui complet, aratandu-se clar conexiunile necesare la intrarile de date ale fiecarui multiplexor precum si semnalele aplicate pe intrarile lor de selectie. Se presupune ca toate iesirile sunt instantanee si ca distorsiunile / perturbatiile / glitches - semnalelor sub forma de input pot fi tolerate (cu alte cuvinte: schema nu prezinta hazard).

c) Deseneze schema corespunzatoare (incluzand continutul ROM-ului), reprezentand o implementare care utilizeaza o memorie ROM si decodificarea completa a intrarilor si variabilelor de stare, pentru ASM-ul descris mai sus; se vor utiliza bistabili de tip D si o memorie ROM.

d) Proiecteze si se implementeze masina de stare descrise mai sus, utilizandu-se bistabili de tip D si un FPLA; se va utiliza, de asemenea, maparea directa a cailor de legatura. FPLA-ul va fi de capacitate minima. Se va arata modul in care este facuta programarea dispozitivului prin desenarea unei scheme de conexiune pentru FPLA, ca parte a schemei generale a sistemului digital / numeric, pentru masina de stare. Sa se stabileasca dimensiunile necesare pentru FPLA.

A. Blocurile ASM si Tabelul de stare

Tabelul de stare asociat masinii de stare

|

Intrari |

Starea curenta |

Starea urmatoare |

Iesiri |

||

|

S T1 T2 T3 |

Simb |

A B C |

Simb |

NA NB NC |

X Y Z C1 C2 C3 C4 |

|

0 * * * |

0 0 0 |

0 0 0 |

|

||

|

1 * * * |

0 0 0 |

0 0 1 |

|

||

|

* 0 * * |

0 0 1 |

0 1 1 |

|

||

|

* 1 * * |

0 0 1 |

0 0 1 |

|

||

|

* * 0 * |

0 1 1 |

0 0 0 |

|

||

|

* 0 1 * |

0 1 1 |

0 1 1 |

|

||

|

* 1 1 * |

0 1 1 |

1 0 0 |

|

||

|

* * * * |

1 0 0 |

1 1 0 |

|

||

|

* * * 0 |

1 1 0 |

0 0 0 |

|

||

|

* * * 1 |

1 1 0 |

1 1 0 |

|

Bloc ASM 1 Bloc ASM 2 Bloc ASM 3 Bloc ASM 4 Bloc ASM 5

B. Proiectarea cu bistabili D si implementare cu multiplexoare si porti logice

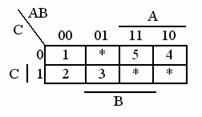

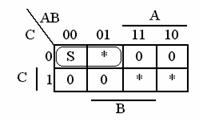

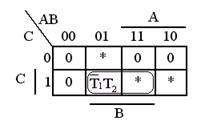

Realizarea diagramelor VID prin maparea directa din tabela ASM a functiilor NAsDA, NBsDB si NCsDC, prin includerea in diagrama a variabilelor de intrare S, T1, T2 si T3. Se recurge la aceasta metoda deoarece completarea diagramelor Karnough de 7 variabile este anevoioasa.

Modul in care se completeaza diagramele VID:

Daca toate caile de legatura sau conexiunile de stare (dintr-o stare bloc ASM) dau iesiri in 1" logic, locatia corespunzatoare din diagrama VID se completeaza cu logic.

Daca toate caile de legatura sau conexiunile de stare (dintr-o stare bloc ASM) dau iesiri in " logic, locatia corespunzatoare din diagrama VID se completeaza cu logic.

Daca toate conexiunile de stare dau iesiri diferite, atunci locatia corespunzatoare din diagrama VID este completata cu o variabila sau expresie logica (formula din variabile include in diagrama) si care se obtine luandu-se in considerare valorile variabilelor incluse pentru care iesirea sau functia de iesire considerata are valoarea logica "1" sau "0".

Completarea diagramei de stare:

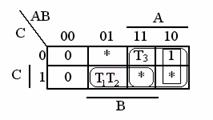

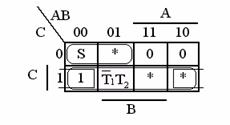

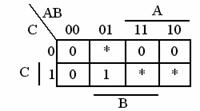

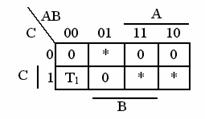

Diagrama VID pentru functia DA:

![]()

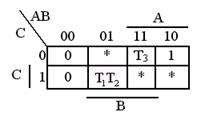

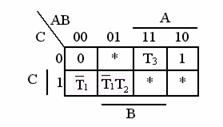

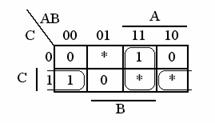

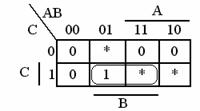

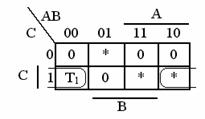

Diagrama VID pentru functia DB:

![]()

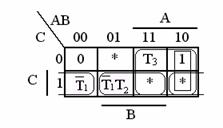

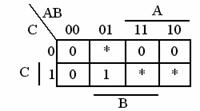

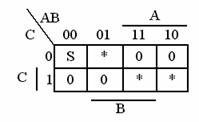

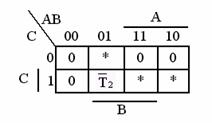

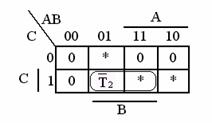

Diagrama VID pentru functia DC:

![]()

In continuare trebuie obtinute expresiile iesirilor / functiilor de iesire pentru masina de stare studiata si care sunt realizate de catre Logica Combinationala a Iesirilor (LCE). Si in acest caz aceste functii se obtin utilizandu-se maparea directa din tabela ASM corespunzatoare masinii de stare, precum si tehnica diagramei VID.

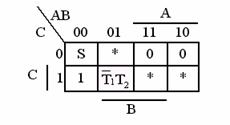

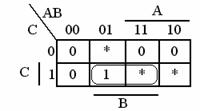

Diagrama VID pentru functia X:

![]()

Diagrama VID pentru functia Y:

![]()

Diagrama VID pentru functia Z:

![]()

Diagrama VID pentru functia C1:

![]()

Diagrama VID pentru functia C2:

![]()

Diagrama VID pentru functia C3:

![]()

Diagrama VID pentru functia C4:

![]()

Implementarea GNS utilizand un singur etaj de multiplexoare si a LCE folosind porti logice:

C. Implementarea cu ROM si bistabili D

|

Stare prezenta (simb) Nr.cai de leg. / conexiuni de stare Starea urm. (simb) |

|||||||||

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

5 |

|

Adresa |

Locatie ASM |

Continut |

Adresa |

Locatie ASM |

Continut |

||

|

S T1 T2 T3 A B C |

Bloc |

Cale |

(hex) |

S T1 T2 T3 A B C |

Bloc |

Cale |

(hex) |

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

0C00 |

|

0C80 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

0C80 |

|

0C80 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

D000 |

|

D000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

6C40 |

|

8C00 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

6C40 |

|

8C00 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

D000 |

|

D000 |

||||

|

|

| ||||||

|

Adresa |

Locatie ASM |

Continut |

Adresa |

Locatie ASM |

Continut |

||

|

S T1 T2 T3 A B C |

Bloc |

Cale |

(hex) |

S T1 T2 T3 A B C |

Bloc |

Cale |

(hex) |

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

0C80 |

|

0C80 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

0C80 |

|

0C80 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

D000 |

|

D000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

6C40 |

|

8C00 |

||||

|

|

C000 |

|

C000 |

||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

| ||||||

|

|

6C40 |

|

8C00 |

||||

|

|

C000 |

|

C000 |

||||

|

|

|

| |||||

|

|

D000 |

|

D000 |

||||

|

|

| ||||||

Pentru MAS definite printr-un numar de stari mai mare decat 20 se recomanda si se justifica din punct de vedere economic utilizarea memoriei ROM (EPROM) in raport cu logica realizata cu circuite integrate pe scara redusa respectiv medie pentru constructia GNS.

Procedura obisnuita de utilizare a memoriilor ROM o reprezinta partitionarea variabilelor acestora pe zone de biti la iesire asociate adresarii starii urmatoare, codificarii testelor sau intrarilor (de fapt a iesirilor de comanda catre proces). Elementele de decizie (intrarile) pot fi memorate in diverse moduri, fie prin includerea lor in decodificatoare de adresa sau locatiile unei zone de memorie, fie prin aplicarea lor la un MUX al intrarilor. O organigrama rigida a informatiilor intr-o memorie ROM impune intotdeauna anumite restrictii asupra constructiei algoritmului lui si alcatuirii organigramei ASM fie ca aceste restrictii se refera la un numar de elemente de stari, de intrari, de teste efectuate in fiecare stare, sau la numarul de iesiri conditionate de intrari.

Formatul cuvantului de iesire:

|

DA |

DB |

DC |

X |

Z |

Y |

C1 |

C2 |

C3 |

C4 |

|

T1 | ||||||||||||||||||||||||

|

CLK T2 | ||||||||||||||||||||||||

|

| ||||||||||||||||||||||||

|

T3 | ||||||||||||||||||||||||

|

DC DB DA A |

0C80 |

0C80 |

6C40 |

6C40 |

0C80 |

0C80 |

6C40 |

6C40 |

0C80 |

0C80 |

6C40 |

6C40 |

0C80 |

0C80 |

6C40 |

6C40 |

||||||||

|

D Q Q |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

C000 |

||||||||

|

C B | ||||||||||||||||||||||||

|

'A' |

D000 |

D000 |

D000 |

D000 |

D000 |

D000 |

D000 |

D000 |

||||||||||||||||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

D. Implementarea cu FPLA si bistabili D

Implementarea cu FPLA a masinii algoritmice de stare in care se utilizeaza maparea sau tabelarea directa a conexiunilor de stare sau a cailor de legatura. Pentru obtinerea expresiilor necesare programarii FPLA-ului se analizeaza tabela ASM de la punctul a), luandu-se in considerare valorile '1' logic din coloanele corespunzatoare iesirilor (X, Y, Z, C1, C2, C3 si C4), respectiv starilor urmatoare (DA, DB, DC).

Copyright © 2024 - Toate drepturile rezervate