| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

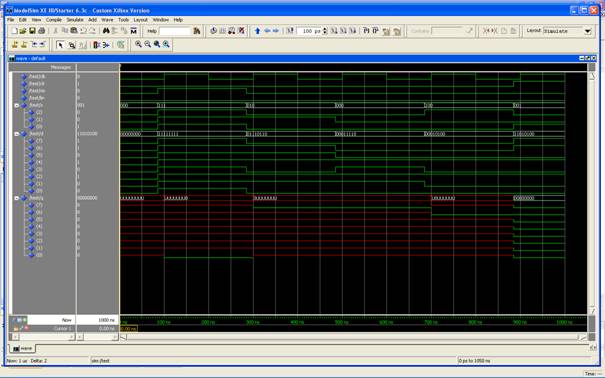

Registru de deplasare cu functii extinse

Codul

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity shift_reg is

port (CLK, CLR, RIN, LIN: in STD_LOGIC;

S: in std_logic_vector (2 downto 0 ) ;

D: in std_logic_vector ( 7 downto 0) ;

Q: buffer std_logic_vector(7 downto 0));

end shift_reg;

architecture schift_reg_arch of shift_reg is

signal IQ: STD_LOGIC_VECTOR (7 downto 0);

begin

process (CLK, CLR, IQ)

begin

if (CLR = '1') then IQ <= (others => '0');

elsif (CLK'event and CLK = '1') then

case CONV_INTEGER (S) is

when 0 => null;

when 1 => IQ <= D;

when 2 => IQ <= RIN & IQ(7 downto 1);

when 3 => IQ <= IQ( 6 downto 0) & LIN;

when 4 => IQ <= Q(0) & IQ (7 downto 1);

when 5 => IQ <= IQ (6 downto 0) & Q(7);

when 6 => IQ <= Q(7) & IQ (7 downto 1);

when 7 => IQ <= IQ (6 downto 0) & '0';

when others => null;

end case;

end if;

Q <= IQ;

end process;

end architecture;

Afisarea rezultatelor simularii

|

Politica de confidentialitate |

Copyright © 2025 - Toate drepturile rezervate