| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Unitatea aritmetica si logica

Codul

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity alu is

port(A,R: in STD_LOGIC_VECTOR(7 downto 0);

LD_CRY, ALU_CRY, SET_CRY, RESET, PASS, LD_Z, LD_ACC, CLOCK, ADD:

in STD_LOGIC;

ZERO, CARRY: out STD_LOGIC;

ACC: out STD_LOGIC_VECTOR(7 downto 0));

end alu;

architecture alg of alu is

signal A_sig, R_sig: UNSIGNED (8 downto 0):='000000000';

signal ACC_sig : UNSIGNED (8 downto 0):='000000000';

signal CARRY_sig: std_logic;

signal CARRY_sig_out: std_logic;

signal Zero_sig: std_logic;

signal sel: std_logic_vector (1 downto 0);

begin

sel <= PASS&ADD;

p2_secvential: process (RESET, CLOCK, PASS, ADD, R_sig, A_sig,

CARRY_sig, ACC_sig, zero_sig, sel, A, R )

begin

zero_sig <= (A(7)and R(7))or (A(6)and R(6))or (A(5)and R(5))or

(A(4)and R(4))or (A(3)and R(3))or

(A(2)and R(2))or (A(1)and R(1))or (A(0)and R(0));

A_sig <= '0'& UNSIGNED (A);

R_sig <= '0'&UNSIGNED(R);

CARRY_sig_out<= ACC_sig (8);

case sel is

when '00' => ACC_sig <= '0' & UNSIGNED(A xor R);

when '01' => ACC_sig <= A_sig (7 downto 0) + R_sig (7

downto 0) + '0000000'& CARRY_sig;

when others => ACC_sig <= A_sig;

end case;

if reset = '1' then

CARRY_sig <= '0';

ZERO_sig <= '0';

ACC_sig <= (others => '0');

elsif clock'event and clock = '1' then

if LD_Z = '1' then

ZERO <= ZERO_sig;

end if;

if LD_CRY = '1' then

if ALU_cry = '1' then

carry_sig <= carry_sig_out;

carry <= carry_sig_out;

elsif ALU_cry = '0' then

carry_sig <= set_cry;

end if;

end if;

if LD_ACC = '1' then

ACC <= conv_std_logic_vector (ACC_sig(7 downto 0),8);

end if;

end if;

end process;

end architecture ALG;

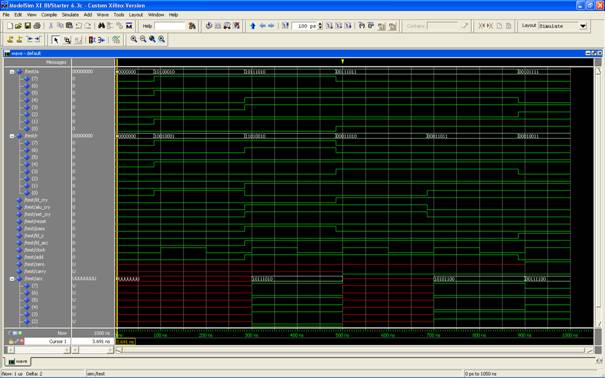

Afisarea rezultatelor simularii

|

Politica de confidentialitate |

Copyright © 2024 - Toate drepturile rezervate