| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

1. Ce sunt asambloarele? Descrieti etapele procesului de asamblare.

Asambloarele sunt programe care traslateaza programele sursa, scrise in limbaj de asamblare, in cod masina. Primele asambloare utilizau pt referirea datelor adrese fizice, dupa care s-au introdus nume simbolice pentru date si adrese. Ulterior au aparut macroasambloare, care permit utilizarea de macroinstructiuni, care permit ca unor secvente de instructiuni sa li se asocieze un nume. Se pot utilize nu numai date simple, dar si date structurate, asemanatoare celor din limbajele de nivel inalt.

Operatia de asamblare se realizeaza in 2 etape:

a) Se genereaza o tabela de simboluri, ce va contine toate numele simbolice din program, exceptand numele simbolice externe (definite in alte module), instructiuni si directive de asamblare. In aceasta etapa, asamblorul contorizeaza instructiunile si datele si asociaza numelor simbolice o pozitie relativa ( deplasament) fata de inceputul programului, ca si cum programul ar incepe de la adresa 0. In realitate, programul nu se incarca in memoria RAM de la adresa 0 (care este o zona folosita de SO), ci de la o adresa furnizata de SO, in functie de spatial de memorie disponibil. Din acest motiv, programul furnizat de asamblor este relocabil.

b) La pasul al doilea se obtine programul obiect, translatand programul instructiune cu instructiunesi inlocuind in instructiunile respective numele simbolice cu valorile numerice associate in tabela de simboluri. Programul executabil se obtine in urma etapei de editare de legaturi (linkeditare), care permite legarea mai multor module relocabile intr-un fisier executabil, rezolvandu-se toate referintele incrucisate care au fost folosite in alte module.

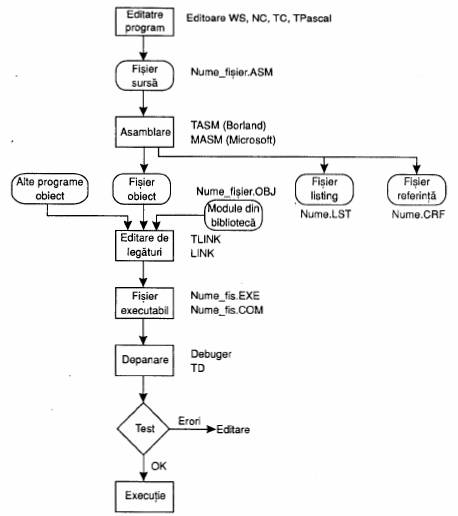

2. Etapele parcurse pentru realizarea unui program in limbaj de asamblare.

Prima etapa este cea de editare a programului sursa, ce are extensia .ASM si care poate fi realizata cu orice editor. Dupa aceasta, urmeaza asamblarea, care furnizeaza programul obiect, cu extensia .OBJ; daca apar erori in faza de asamblare, se reia editarea programului, corectand erorile respective. La editarea de legaturi, pe langa programul current, pot fi utilizate si alte programe obiect, eventual din biblioteca. Fisierul executabil astfel obtinut poate fi testat si depanat utilizand una din utilitarele TurbaDebugger (TD) sau Debug.

Operatiile executate in mod repetat de procesor, la care se rezuma functionarea sa. (ciclurile realizate de procesor pentru executia unei instructiuni)

1. Citeste instructiunea - pe durata acestui ciclu se transmite adresa instructiunii de executat si se aduce, din memorie, instructiunea in CPU (ciclul Fetch)

2. Decodifica instructiunea.

3. Transmite adresa si citeste un operand din memoriem daca se specifica in instructiune (ciclul Read) 4. Executa instructiunea (ciclul Execution).

5. Transmite adresa si scrie rezultatul in memorie, daca intructiunea o cere (ciclul Write).

Descrieti unitatile functionale ale unui procesor (286/386/486/Pentium).

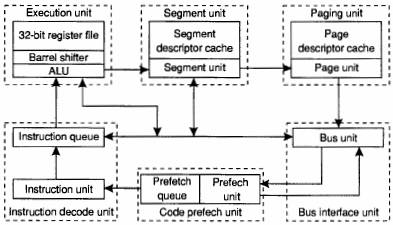

Cele patru unitati functionale ale procesorului 286 sunt: unitatea de adresare (AU), unitatea de interfata cu magistrala (BU), unitatea de decodificare instructiuni (IU) si unitatea de executie (EU).

Unitatea de adresare(AU - Address Unit) determina adresa fizica si contine un sumator de deplasament si un sumator de adrese fizice; aceasta determina adresa fizica, ca suma intre adresa de segment si offset. De asemenea, in modul protejat, verifica limita si dimensiunea unui segment si furnizeaza adresa de baza a segmentului; aceasta unitate este complet izolata de exterior.

Unitatea de interfata cu magistrala (BU - Bus Unit) contine circuite driver si latch pentru adrese, o unitate de citire anticipata a instructiunilor (PreFetcher), interfata cu extensia de procesor, logica pentru controlul magistralei, o coada de instructiuni (de 6 octeti) si realizeaza transmisia/receptia datelor. Luungimea cozii a fost aleasa astfel incat BU sa tina ocupata unitatea de executie cat mai mult timp posibil. De fapt, aceasta unitate realizeza comunicatia cu exteriorul.

Unitatea de decodificare a instructiunilor (IU - Instruction Unit) preia octetii din coada de instructiuni si ii translateaza in microcod. Instructiunile decodificate (in numar de trei) sunt puse intr-o coada, unde asteapta sa fie prelucrate de EU. Unitatea lucreaza in paralel cu celelalte unitati si incepe o noua decodificare in momentul in care o locatie din coada devine libera.

Unitatea de executie (EU - Execution Unit) executa instructiunile din coada de instructiuni decodificate si comunica cu celelate unitati. Aceasta unitate implementeaza functiile de executie ale tuturor instructiunilor, furnizeaza adrese spre AU, si date spre BU, manipuleaza registrele generale si indicatorii de stare. Cu exceptia unor pini de control, EU este complet izolata de exterior. EU si IU functioneaza asincron si se sincronizeaza in caz de coada goala sau coada plina. Daca EU necesita un acces la memorie sau la circuitele de I/O, se lanseaza o cerere de acces catre BU, care controleaza si efectueaza accesul la adresa furnizata catre AU. Daca o astfel de cerere apare in timp ce BU este intr-un ciclu de magistrala de citire a unei instructiuni, BU termina ciclul curent dupa care raspunde cererii de acces lansata de EU.

5. Structura interna a procesorului 286/386/486.

M/IO = separa ciclurile de memorie de cele I/O (1 = mem, halt; 0 = I/O, recunoastere intrerupere)

cod/INTA, S1 - S0 = semnale de stare a magistralei

READY = termina ciclul de magistrala

HOLD (bus HOLD request) = permite unui alt modul master (procesor) sa ceara controlul magistralei

HLDA (bus HOLD Acnkowledge)

PEREQ = Processor Extension operand REQuest

PEACK = Processor Extension operand ACKnowledge

INTR = INTerrupt Request

NMI = Non Maskable Interrupt

Structura interna a procesorului 386:

Structura interna a procesorului 486:

Unitatile componente ale procesorului 386/486/Pentium.

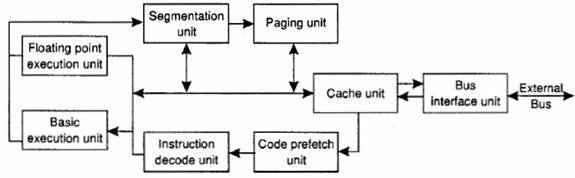

Interfata cu magistrala (BIU - Bus Interface Unit) realizeaza legatura procesorului cu lumea externa. Orice alta unitate ce necesita date din exterior va solicita acestei unitati sa realizeze operatia respectiva. Pentru a realiza transferul datelor (la memorie sau la porturile de I/E), unitatea va furniza numai adrese fizice, deci adresele operanzilor trebuie, mai intai, sa treaca prin unitatea de segmentare si cea de paginare, daca este necesar.

Unitatea de citire anticipata a instructiunilor (IPU - Instruction Prefetch Unit sau Code Prefetch Unit) are rolul de a rnentine plina coada de instructiuni; unitatea de decodificare extrage instructiunile din aceasti coada, de 16 octeti, ori de cate ori se elibereaza octeti din aceasta coada. Unitatea de anticipare lanseaza o cerere catre BIU pentru citirea altor octeti din memorie (cite 4 octeti la un ciclu de citire). Deci BIU este ocupata cu o cerere de la o alta unitate, atunci, dupa servirea unitatii respective, va fi luata in considerare si cererea unitatii de anticipare. Unitatea IPU este anuntata ori de cite ori unitatea de executie prelucreaza o instructiune de salt (CALL, JMP sau intrerupere) astfel incat ea poate incepe citirea instructiunilor de la noua adresa. In aceste situatii coada este reinitializata, pentru a evita ca unitatea de executie sa primeasca instructiuni ce nu sunt in secventa executata in mod curent.

Unitatea de decodificare (IDU - Instruction Decode Unit). Aceasta unitate preia octeti individuali din coada de instructiuni si determina numarul de octeti necesari pentru a completa instructiunea urmatoare. O instructiune 80386 poate avea de la 1 la 16 octeti. Dupa extragerea intregii instructiuni din coada, unitatea reformuleaza codul operatiei

intr-un format de instructiune intern si plaseaza instructiunea decodificata intr-o coada de instructiuni (decodificate), care este de 3 operatii. Unitatea de decodificare va semnala unitatea BIU daca instructiunea decodificata va necesita o referire la memorie. Aceasta permite operanzilor instructiunilor sa fie obtinuti anterior executiei instructiunilor.

Unitatea de executie (EU - Execution Unit). Aceasta este acea parte din CPU (Central Processor Unit) care realizeaza calculele. Ea realizeaza diferite operatii (deplasari, adunari, inmultiri, impirtiri etc.) necesare pentru executia instructiunilor. Setul de registre se afla in aceasta unitate. Unitatea contine, de asemenea, o componenta logica denumita barrel shifter, care poate realiza deplasiri/rotiri multi-bit, intr-un singur ciclu de ceas. Aceasta facilitate este utilizata de EU nu numai in instructiunile de deplasare, dar si pentru accelerarea inmultirilor si

in generarea adreselor indexate. De asemenea, EU se adreseaza unitatii BIU, cand ea are datele necesare a fi transmise catre memorie sau magistrala de I/E.

Unitatea de segmentare (SU - Segmentation Unit) transleaza adresele segmentate in adrese liniare. Timpul de translare a segmentului este aproape in intregime ascuns de paralelismul arhitecturii procesorului 386. Timpul tipic este deci de 0 impulsuri de ceas, dar daca este necesar timp pentru translarea adresei, acesta este de cel mult 1 impuls de ceas. Unitatea de segmentare contine o memorie (cache) ce pastreaza informatii din tabela de descriptori pentru fiecare dintre cele 6 registre segment.

Unitatea de paginare (PU - Paging Unit) primeste adresele liniare generate de SU si le converteste in adrese fizice. Daca paginarea nu este activata (deci PU este dezactivata), adresa liniara de la SU devine adresa fizica. Cand paginarea este activata, spatiul de adrese liniar al procesorului 386 este impartit in blocuri de 4096 octeti, denumite pagini. Fiecare pagina poate fi mapata (suprapusa) la o adresa fizica total diferita. Procesorul 386 utilizeaza o tabela de pagini pentru a translata fiecare adresa liniara la o adresa fizica. Unitatea contine un cache asociativ denumit tampon de translare a adresei liniare in adresa fizica-TLB (Translation Lookaside Buffer), care contine intrarile (adresele) pentru 32 de pagini, cel mai recent utilizate. Daca o intrare in tabela de pagini nu este gasita in TLB, un ciclu de citire din memorie pe 32 de biti aduce intrarea din memoria RAM. in conditii normale de operare, mai putin de 2% din toate referirile la memorie cer procesorului sa caute in afara tabelei TLB o intrare in tabela de pagini. Timpul necesar pentru a realiza translatia este intre 0 si 5 impulsuri de ceas. Datorita tabelei TLB, intarzierea tipica este de 0,5 impulsuri de ceas.

Imbunatatiri aduse procesoarelor Pentium fata de procesorul 486.

- memoria cache distincta pentru instructiuni si pentru date (cate 8 Ko pentru fiecare);

- doua benzi de asamblare pentru numere intregi (denumite U si V);

- prezicerea adreselor de salt (numita si predictie dinamica) folosind un tampon care retine aceste adrese de salt (BTB - Branch Target Buffer);

- unitatea de calcul in virgula mobila organizata ca banda de asamblare;

- magistrala externa pe 64 de biti, deci intr-un singur acces (impuls de ceas) la memorie se pot transfera cuvinte de 64 de biti;

- arhitectura interna imbunatatita (superscalara) si algoritmii imbunatatiti (rapizi) pentru executia instructiunilor FPU (cele in virgula mobila) intr-un singur impuls de ceas sau doua instructiuni cu numere intregi intr-un singur impuls de ceas;

- folosirea paritatii pentru magistrala de date si memoriile cache interne;

- monitorizarea performantelor; executie pas cu pas;

- alte facilitati: modul de administrare al sistemului, extensie pentru mod virtual, suport biprocesor, gestionarea alimentarii; detectia erorilor si a integritatii datelor.

8. Descrieti cateva (2-3) concepte noi utilizate la procesoarele Pentium.

Banda de asamblare (pipeline): mai multe instructiuni masina sunt incarcate secvential intr-o linie complexa de prelucrare, asemanatoare cu memoria FIFO (in locul celulelor de memorie, aici sunt automate secventiale, care efectueaza diferite modificari asupra datelor ce trec prin pipeline) sau cu o banda de asamblare. Prin pipeline se sparg (transleaza) instructiunile in micro-operatii ce se executa in unitati separate. Rezultatul este asamblat si se trimite exteriorului. Daca s-au incarcat date incorecte in structurile secventiale din pipeline (de exemplu la executia speculativa ultimul salt a fost gresit), atunci banda pipeline este golita si reincarcata cu date corecte; deci el contine toate operatiile/rezultatele ce se executa in acel moment in diferite stadii, in functie de pozitia lor in structura secventiala din pipeline.

Microinstructiune: instructiunile in cod masina sunt sparte in 1-4 microinstructiuni de lungime fixa, care se executa cvasiparalel. Timpii lor de executie sunt cunoscuti si astfel elementele de prelucrare din pipeline pot face o planificare corecta, in timp, a executiei.

Superscalar: procesoare cu mai multe benzi de asamblare, paralele, care pot executa mai multe instructiuni simultan, intr-un singur impuls de ceas (Pentium II are doua benzi, U si V); nivelul superscalar reprezinta numarul de instructiuni care se pot executa simultan. Se mai utilizeaza si termenul de superbanda de asamblare, care inseamna banda de asamblare cu peste 10 niveluri (etape sau stagii).

9. Operatiile realizate de procesor pe durata unui ciclu de magistrala, pentru comanda altor dispozitive (memorie, echipamente de I/E).

se activeaza pe magistrala de adrese adresa unei locatii de memorie sau a unui port I/O si se memoreaza intr-un registru de adrese extern;

se genereaza semnalul de comanda corespunzator pentru citire/scriere date;

dispozitivul selectat (memoria sau portul l/O) realizeaza transferul de date si transmite procesorului un semnal de raspuns, pentru a incheia ciclul.

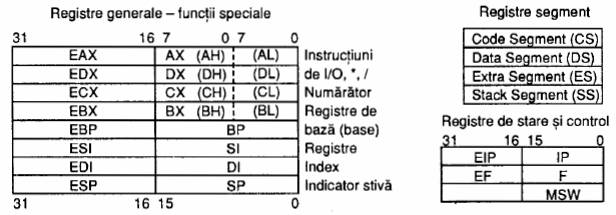

10. Resursele procesorului (registrele sale, dimensiune, tipul lor, etc.)

11. Descrieti indicatorii din registrul indicatori (stare, control, speciali).

Indicatori de stare:

- OF (Overflow Flag) - este pozitionat pe 1 daca rezultatul unei operatii aritmetice depaseste domeniul de reprezentare (limita superioara/inferioara a acestuia) pentru numerele cu care se lucreaza, adica rezultatul nu poate fi memorat in destinatia stabilita de instructiune (de exemplu, impartirea prin zero sau adunarea/inmultirea a doua numere mari - la limita superioara a domeniului).

- SF (Sign Flag) - este indicatorul de semn al rezultatului unei operatii si, de fapt, coincide cu primul bit al rezultatului, fiind 1 daca numarul este negativ si 0 pentru pozitiv.

- ZF (Zero Flag) - este pozitionat pe 1 daca rezultatul unei operatii aritmetice sau logice este zero, altfel 0

- AF (Auxiliary carry Flag) - este 1 daca in urma executiei unei instructiuni a aparut un transport din rangul 3 in rangul 4 sau un imprumut dinspre rangul 4 spre rangul 3. Acest indicator este utilizat pentru implementarea aritmeticii pentru numere zecimale codificate binar (BCD - Binary Coded Decimal).

- PF (Parity Flag) - este pozitionat pe 1 cand numarul de unitati din rezultat este par (paritate para)

- CF (Carry Flag) - se pozitioneaza pe 1 daca a aparut un transport sau un imprumut in/din rangul cel mai semnificativ al rezultatului, in urma executiei unei instructiuni aritmetice.

Indicatorii de control:

- DF (Direction Flag) - este utilizat de instructiunile pe siruri si specifica directia de parcurgere a acestora (0 parcurgere de la adrese mici spre adrese mari;1 invers)

- IF (Interrupt Flag) - acest indicator controleaza acceptarea semnalelor de intrerupere externa. Daca IF = 1, este activat sistemul de intreruperi, adica sunt acceptate semnale de intrerupere externa (mascabile, pe linia INTR), altfel acestea sunt ignorate. Indicatorul nu are influenta asupra semnalului de intrerupere nemascabila - NMI.

- TF (Trace Flag) - este utilizat pentru controlul executiei instructiunilor in regim pas cu pas (instructiune cu instructiune), in scopul depanarii programelor. Daca indicatorul este 1, dupa executia fiecarei instructiuni se va genera un semnal de intrerupere intern (pe nivelul 1). Evident, executia secventei de tratare a acestor intreruperi se va face cu indicatorul TF = 0.

Indicatori speciali:

- IOPL (Input/Output Privilege Level) - acest indicator ocupa doi biti si defineste dreptul de a utiliza instructiuni de intrare/iesire (I/O). Aceste instructiuni, precum si instructiunile ce opereaza asupra lui IF, sunt denumite instructiuni "sensibile' la IOPL, deoarece ele nu pot fi executate decat daca CPL <=IOPL - procedura care executa aceste instructiuni trebuie sa se execute la un privilegiu cel putin egal cu cel specificat de IOPL.

- NT (Nested Task) - este automat pozitionat pe 1 sau O de operatiile de comutare de task; executia unei instructiuni IRET, cu NT=1, realizeaza o comutare de task. La procesorul 386/486 acest registru (EF) are 32 biti, dintre care ultimii 16 sunt identici cu acestia, dar in plus mai sunt utilizati inca doi biti (16 si 17) care au urmatoarea semnificatie:

- RF (Resume Flag) - acest indicator dezactiveaza temporar exceptiile de depanare (debug), astfel incat sa se poata reporni o instructiune dupa o exceptie de depanare, fara a se genera imediat o alta exceptie de depanare; adica nu se executa o instructiune de breakpoint, daca este returnat controlul de exceptie de depanare direct la o astfel de instructiune.

- VM (Virtual 8086 Mode) - acest bit arata ca se executa un program 8086, daca este pozitionat pe 1.

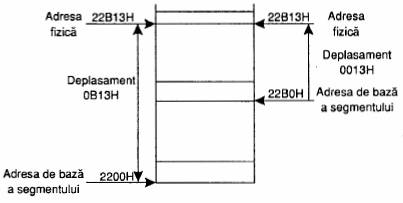

12. Organizarea memoriei (modalitatea de memorare a datelor, instructiunilor, referirea la memorie-adresa logica)

Memoria este

organizata ca seturi de segmente de lungime variabila. Fiecare segment este o secventa continua, liniara de pana la 64 Kocteti

(2^16). Adresa fizica de inceput a unui segment este

multiplu de 16. Fiecare segment este alcatuit din

locatii succesive de memorie si este o unitate independenta si adresabila

separat. Fiecarui segment i se asociaza o adresa de baza, care este adresa de start, in spatiul memoriei. Segmentele, in modul real, pot fi adiacente, disjuncte sau

suprapuse total sau partial. O locatie de memorie poate fi continuta in

mai multe segmente. Unei locatii de memorie i se asociaza o adresa fizica, de

20 sau 24 biti, care identifica in mod unic locatia, si o adresa logica (de

fapt cu acestea lucreaza programatorul) care nu este unica. Adresa logica se

compune dintr-un selector (adica adresa de baza a segmentului) si un deplasament fata de inceputul segmentului; practic

aceeasi adresa fizica poate fi referita de mai multe adrese logice: modificand

in mod corespunzator deplasamentul, pentru o alta adresa de baza a segmentului

se poate accesa aceeasi locatie de memorie, ca in figura.

Memoria este

organizata ca seturi de segmente de lungime variabila. Fiecare segment este o secventa continua, liniara de pana la 64 Kocteti

(2^16). Adresa fizica de inceput a unui segment este

multiplu de 16. Fiecare segment este alcatuit din

locatii succesive de memorie si este o unitate independenta si adresabila

separat. Fiecarui segment i se asociaza o adresa de baza, care este adresa de start, in spatiul memoriei. Segmentele, in modul real, pot fi adiacente, disjuncte sau

suprapuse total sau partial. O locatie de memorie poate fi continuta in

mai multe segmente. Unei locatii de memorie i se asociaza o adresa fizica, de

20 sau 24 biti, care identifica in mod unic locatia, si o adresa logica (de

fapt cu acestea lucreaza programatorul) care nu este unica. Adresa logica se

compune dintr-un selector (adica adresa de baza a segmentului) si un deplasament fata de inceputul segmentului; practic

aceeasi adresa fizica poate fi referita de mai multe adrese logice: modificand

in mod corespunzator deplasamentul, pentru o alta adresa de baza a segmentului

se poate accesa aceeasi locatie de memorie, ca in figura.

Din punct de vedere fizic, memoria este organizata sub forma a doua blocuri: blocul superior (high) este conectat la magistrala de date pe liniile D15-D8, iar blocul inferior (low) conectat la liniile D7-D0. Ambele blocuri sunt selectate in paralel, pe liniile de adresa A19(A23)-A1; pentru accesul selectiv la octetul inferior, la cel superior sau la ambii octeti simultan, deci la un cuvant, se activeaza in mod corespunzator liniile A1 si BHE. Pentru procesoarele 386/486 poate fi considerat inca un bloc de memorie, conectat la liniile de date D31-D16, pentru a se putea citi si cuvinte de 32 biti.

Pentru citirea/scrierea datelor de 16 sau 32 biti, memorate la adrese ce nu sunt multiplu de 2 sau 4, vor fi necesare doua cicluri de magistrala, in loc de unul, daca datele sunt aliniate in memorie.

Conventia de memorare a datelor multiplu de octeti, 16, 32, 64 sau 80 biti, este: se incepe cu octetul mai putin semnificativ la prima adresa (cea mai mica) si se depun in continuare octetii urmatori, in ordinea crescanda a semnificatiei, terminand cu octetul cel mai semnificativ la adresele urmatoare.

O clasa speciala de date este cea pe dublu cuvant (32 biti), denumite si pointeri sau referinte, utilizate pentru a adresa date si cod. Si acestea se memoreaza dupa aceeasi regula: la adresa mai mica se afla deplasamentul (offset), iar la adresele urmatoare se afla adresa de segment a pointerului.

13.

Generarea adreselor fizice in modul real de adresare.

13.

Generarea adreselor fizice in modul real de adresare.

In acest mod, 80286 executa setul de instructiuni 8086. Memoria fizica este o retea continua de 1Mo, adresabila prin pinii A0A19 si BHE (A20-A23 pot fi ignorati). In acest mod, procesorul genereaza o adresa de 20 biti, direct dintr-o adresa de segment de baza de 20 biti si un offset de 16 biti, ca in figura. Portiunea selectorului unui pointer este interpretata ca primii 16 biti dintr-o adresa de segment de 20 biti (ultimii patru sunt intotdeauna zero). Adresele de segment sunt intotdeauna multiplii de 16. in modul real de adresare toate segmentele au dimensiunea de 64 Ko. In modul real sunt rezervate doua zone de memorie, si anume: zona de initializare a sistemului (FFFF0-FFFFFH) si zona tabelei de intreruperi (00000H-003FFH).

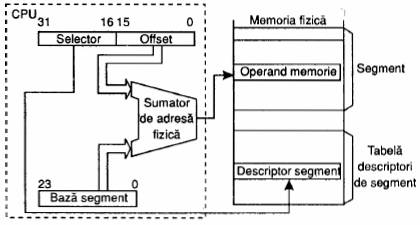

14. Generarea adreselor fizice in modul protejat de adresare virtuala

Modul

protejat utilizeaza pointeri de 32 biti, constand dintr-un selector de 16 biti

si un offset de 16 biti. Selectorul specifica un index intr-o tabela rezidenta in memorie, in loc de

primii 16 biti ai adresei reale de memorie. Adresa

de baza de 24 biti a segmentului

Modul

protejat utilizeaza pointeri de 32 biti, constand dintr-un selector de 16 biti

si un offset de 16 biti. Selectorul specifica un index intr-o tabela rezidenta in memorie, in loc de

primii 16 biti ai adresei reale de memorie. Adresa

de baza de 24 biti a segmentului

dorit se obtine de la tabelele din memorie. Deplasamentul se aduna la adresa de baza a segmentului pentru a forma adresa fizica, ca in figura.

Modul de translatare a adresei logice in adresa fizica (segmentare, paginare).

Paginare: In locul maparii intregului spatiu logic de adrese ca o unitate, mecanisme mai avansate de translatie a adresei mapeaza "pagini"de dimensiune fixa, mai mici, ale spatiului de adrese logice, in pagini de memorie fizica. Astfel, un program mare nu trebuie sa fie realocat intr-o zona continua de memorie care poate fi greu gasita intr-un cadru cu programe multiple, decat mai degraba , in mai multe dectiuni de memorie, mai mici, care sunt mult mai usor de gasit, disponibile. Sunt mai usor de gasit 20 de pagini de 1Ko decat un bloc de 20Ko.

Segmentare: Maparea in acest caz este implementata printr-o tabela de segment, care pastreaza un descriptor pentru fiecare segment. Descriptorul contine adresa de inceput a segmentului si lungimea acestuia. Componenta selectorului de segment a unei adrese logice este utilizata ca un index pentru a selecta descriptorul in tabela (descriptorilor) de segment. Apoi, deplasamentul este adunat la adresa de start a segmentului, furnizata de descriptor, pentru a calcula adresa fizica a operandului referit. Deplasamentul este verificat hardware, pentru a exista siguranta ca referinta nu depaseste lungimea segmentului.

Formatul unui selector. Modul de calcul al spatiului virtual de memorie gestionat de procesor.

![]()

RPL - (Requested Privilege Level) - nivelul de privilegiu dorit;

TI - (Table Indicator) - acest bit face selectia intre tabela de descriptor globala/locala.

Ceilalti biti (15-3) selecteaza intrarea respectiva din tabela. Deci bitii RPL, din campul 1+0, nu sunt implicati, de fapt, in selectarea si specificarea segmentelor. Ceilalti 14 biti ramasi din componenta selectorului desemneaza in mod unic un segment particular. Spatiul de adresa virtuala al unui program va fi format din cel mult 2^14 segmente distincte, intrucat dimensiunea maxima a unui segment este de 64 Kocteti (2^16), rezulta ca spatiul virtual de adresa al unui program poate ajunge la 1 Goctet (2^14*2<6 = 230) de locatii adresabile individual. La 386/486, intrucat dimensiunea unui segment este de 32 de biti, se ajunge la un spatiu total de adresa virtuala de 64 Tocteti (2^14*2^32 = 2^46).

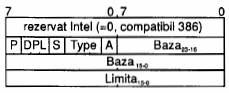

17. Structura unui descriptor de segment (campurile continute de acesta).

- P (Present), daca este 1, segmentul este mapat in memoria fizica altfel nu este mapat in memoria fizica, iar baza si limita nu sunt utilizate;

- DPL - (Descriptor Privilege Level) este atributul de privilegiu, utilizat in teste de privilegiu;

- S- (Segment Descriptor) specifica tipul de segment definit de descriptor (1 este descriptor de segment de cod sau date; 0 descriptor de sistem)

- Type - specifica tipul segmentului: de cod sau de date; cei trei biti au urmatoarea semnificatie:

(3) Executable = 0 => un descriptor de segment de date si, in acest caz

- (2) Expansion Direction (ED) (0 => segmentul se extinde spre adrese mari (date; offset<=limita); 1 => segmentul se extinde spre adrese mici (stiva; offset > limita))

- (1) Writeable (0 => nu se poate scrie in acel segment)

(3) Executable = 1 => un descriptor de cod si atunci semnificatia bitilor urmatori este:

- (2) Conforming (1 => acest segment poate fi executat numai cand CPL >= DPL)

- (1) Readable (0 => segmentul nu poate fi citit, adica este numai executabil, altfel el poate fi citit)

- A (Accessed) (0 => segmentul nu a fost adresat; 1 => selectorul de segment a fost incarcat in registrul segment, sau utilizat de instructiuni de test selector)

18. Niveluri de privilegiu. Obiecte recunoscute de procesor ce contin niveluri de privilegiu.

Mecanismele de protectie ale procesorului 286 se bazeaza pe notiunea de ierarhie de incredere (sau de privilegiu). Exista patru niveluri de privilegiu, mergand de la 0 - cel mai privilegiat, pana la 3 - cel mai putin privilegiat. Urmatoarele obiecte, recunoscute de procesor, contin niveluri de privilegiu:

- descriptorii de segment contin un camp DPL - Descriptor Privilege Level, adica descriptor de nivel de privilegiu;

- selectoarele de segment contin un camp RPL - Requestor's Privilege Level, adica nivelul de privilegiu al procedurii careia ii apartine selectorul;

- un registru intern al procesorului memoreaza CPL - Current Privilege Level, care este egal cu DPL al segmentului pe care il executa procesorul.

Instructiunile pot incarca un registru segment de date (si deci utiliza segmentul tinta) numai daca nivelul DPL al segmentului tinta este, numeric, mai mare sau egal cu maximul dintre nivelurile CPL si RPL ale selectorului. Deci, procesorul preia nivelurile CPL si RPL si creeaza EPL = max(CPL,RPL), denumit nivel efectiv de privilegiu, adica nivelul cel mai putin privilegiat din tre cele doua; apoi acesta (EPL) se compara cu DPL.

Domeniul adresabil al unui task depinde de valoarea lui CPL, si anume pot fi adresate segmentele de date de la acelasi privilegiu sau segmente mai putin privilegiate (adica nivelul de privilegiu asociat segmentului adresat trebuie sa fie, numeric, mai mare sau cel putin egal cu cel al taskului curent), in acest fel, se poate preveni ca o procedura de aplicatie sa citeasca sau sa modifice tabelele sistemului de operare.

19. Ce este si ce contine TSS.

Un TSS este un segment special de memorie, pe care preprocesorul il utilizeaza pentru a suporta multitasking. Acesta contine o copie a tuturor registrelor ce trebuie salvate, pentru a reface starea unui task; el mai contine valori asociate task-ului, dar nu sunt memorate in registrele CPU. TSS contine 3 selectori de segment de stiva aditionali (SS0, SS1, SS2) si 3 pointeri de stiva corespunzatori (ESP0, ESP1, ESP2).

Cand un apel sau intrerupere printr-o poarta determina o modificare de privilegiu, noile registre SS: ESP sunt incarcate din TSS. registrul de task (TR) contine selectorul TSS activ curent.

Cand apare o comutare de task, toate registrele task-ului curent executat sunt salvate in TSS-ul activ. Registrul task se incarca, apoi, cu selectorul unui nou TSS, iar fiecare registru general este incarcat cu valorile corespunzatoare, din noul TSS.

20. Organizarea spatiului de I/O

Procesorul are doua spatii de adrese fizice distincte: memoria si I/O (intrari/iesiri). Dispozitivele periferice (consola, ecranul, tastatura, imprimanta etc.) sunt controlate si comandate de procesor, in general, prin operatii de citire/scriere la anumite locatii, diferite de spatiul de memorie. Acest spatiu este denumit spatiu de l/O si accesul la locatiile respective se face cu instructiuni specifice (In, Out). Locatiile din acest spatiu sunt denumite registre dispozitiv sau porturi de l/O. In general, in acest spatiu sunt plasate perifericele, desi procesorul poate permite maparea (suprapunerea) in memorie a perifericelor.

Spatiul de I/O consta din 64 Kocteti si poate fi impartit in 64 Kporturi de 8 biti, 32 Kporturi de 16 biti sau, la 386/486,16 Kporturi de 32 biti. Pentru a accesa acest spatiu nu se utilizeaza registre segment si, deci, nici mecanismul de segmentare sau pagina. Pinul M/IO specifica spatiul de memorie adresat (fizica sau I/O), deci daca se adreseaza o locatie de memorie sau un port de I/O. Instructiunile I/O, IN si respectiv OUT pot furniza adresa direct in instructiune, ca o constanta de 8 biti (pentru porturile din spatiul 0-255) sau indirect prin registrul DX (pentru tot spatiul de 64 K).

21.Avantajele utilizarii segmentarii si paginarii.

Segmentare

- tehnica partajarii segmentului care permite ca doua sau mai multe task-uri sa partajeze acelasi cod. (sisteme multiutilizator).

De asemenea, un sistem de MV, orientat pe segmente, poate furniza un mod pentru a compacta memoria. Compactarea memoriei permite rezolvarea unei probleme numite fragmentare. Fragmentarea memoriei apare cand memoria ce nu este continua este disponibila pentru a rula aplicatii suplimentare.

Paginarea este utilizata pentru a implementa MV bazata pe blocuri de dimensiune fixa, pagini. Asemanator segmentarii, paginarea translateaza adresele virtuale in adrese fizice, prin maparea (suprapunerea) blocurilor de lungime fixa, de memorie, in locatiile de memorie fizica, denumite cadru pagina. Segmentarea si paginarea sunt similare: un nume si un offset sunt translatate intr-o adresa.

Avantajul esential al paginarii fata de segmentare este reprezentat de dimensiunea fixa a paginarii. Deoarece MV utilizeaza discul se pot alege dimensiuni de pagina care se potrivesc cu dimensiunea sectorului de pe disc. De asemenea paginarea evita problema fragmentarii memoriei, specifica segmentarii. Ori de cate ori o pagina este scoasa din memorie, alta pagina se potriveste exact in spatiul eliberat; (apare alt tip denumit "fragmentare interna").

Alt avantaj alocarea pentru un obiect mare nu trebuie sa fie facuta intr-un spatiu continuu de memorie.

Pagina poate contine portiuni din mai multe segmente, sau invers.

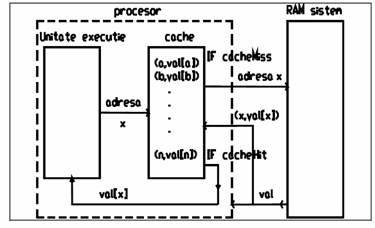

Memoria cache (descrieti organizarea de principiu a acesteia).

Memoria cache memoreaza instructiuni si date, recent accesate, astfel incat ele sunt furnizate transparent si mai rapid decat memoria principala. Cahe-ul este organizata pe linii. Aceste linii sunt organizate ca seturi, fiecare set este mapat pe un grup separat de adrese de memorie, si care sunt de obicei intre 16 si 64 linii pe set.

Acceseaza repetat date din aceeasi locatie de memorie sau din locatii diferite

Concepte utilizate de memoria cache pentru actualizarea informatiei.

- memoria cache stocheaza perechi (adresa & valoare)

- la scrierea unei date de la intrare se verifica daca e segment in prealabil stocat

24. Sistemul de intreruperi. Tipuri de

intreruperi.

24. Sistemul de intreruperi. Tipuri de

intreruperi.

O intrerupere transfera executia la o noua adresa de program. Vechea adresa (CS:IP) a programului si starea masinii (registrul de indicatori) sunt salvate in stiva pentru a permite refacerea programului intrerupt. Structura stivei dupa aparitia unei intreruperi este urmatoarea (fig).

Intreruperile sunt impartite in trei clase: initiate de hardware, instructiunile de intrerupere INT si exceptii dejnstructiune. intreruperile initiate hardware apar ca raspuns la un semnal extern si sunt clasificate ca nemascabile si mascabile. Programele pot determina o intrerupere prin executia instructiunii INT. Exceptiile de instructiune apar cand o conditie neobisnuita, care impiedica executia ulterioara a instructiunii, este detectata in timp ce incearca sa execute o instructiune. Adresa returnata de o exceptie va referi intotdeauna instructiunea ce a cauzat exceptia si include orice prefix de instructiune.

Prioritatile intreruperilor:

|

Ordin |

Intrerupere |

|

Instructiunea INT sau exceptie |

|

|

Intrerupere "Single Step' |

|

|

Intrerupere nemascabila (NMI) |

|

|

Depasire segment extensie de procesor |

|

|

Intrerupere mascabila (INTR) |

Daca apar mai multe intreruperi simultan, ele sunt servite in ordinea din tabela. Daca alte intreruperi raman active, ele sunt prelucrate inainte de prima instructiune din rutina de tratare a intreruperii. Ultima intrerupere prelucrata va fi prima servita.

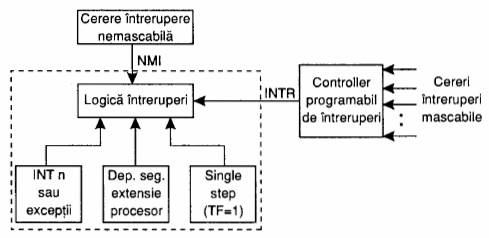

Reprezentarea schematica a sistemului de intreruperi:

25. Intreruperile externe

Intreruperile externe (transmise de dispozitive externe), sunt primite de procesor pe doua linii: NMI si INTR.

Linia INTR este controlata de PIC (Programmable Interrupt Controller); rolul sau este de a accepta cereri de intrerupere de la dispozitivele externe, de a determina care cerere este cea mai prioritara si de a activa linia INTR, daca dispozitivul care a cerut intreruperea este mai prioritar decat cel curent in servire. Cand linia INTR devine activa, procesorul executa diferite actiuni, in functie de starea indicatorului de validare a intreruperilor (IF); oricum, nu se executa nici o actiune pana nu se termina executia instructiunii curente, pe durata careia a aparut intreruperea. Daca IF=0, deci intreruperile mascabile sunt dezactivate procesorul ignora semnalul INTR. intreruperile se activeaza cu instructiunea STI (SeT Interrupt enable flag), deci IF=1 si se dezactiveaza cu instructiunea CLI (CLear Interrupt enable flag). Ele pot fi, de asemenea, mascate selectiv prin transmiterea de comenzi corespunzatoare catre PIC.

Instructiunile de activare a intreruperilor se vor lansa dupa sfarsitul instructiunii urmatoare, pentru a nu incarca excesiv stiva, intreruperea este recunoscuta prin executarea a doua cicluri de magistrala de recunoastere a intreruperii (INTA); pe durata acestor doua cicluri se activeaza semnalul LOCK, pentru a indica altor procesoare ca nu pot obtine magistrala. Primul ciclu este utilizat de procesor pentru a transmite catre PIC ca se onoreaza cererea, iar in timpul celui de-al doilea ciclu, PIC raspunde plasand un octet pe magistrala de date, care contine tipul intreruperii (32+255), asociat cu servirea cererii de intrerupere. Tipul este asignat la initializarea procesorului, prin program. Procesorul utilizeaza acest cod pentru a apela o procedura de tratare a intreruperii.

O cerere externa de intrerupere poate veni si pe linia NMI, care e comandata pe frontul semnalului (INTR e comandata pe nivel) si este utilizata pentru evenimente deosebite (cadere tensiune, repornire). intreruperile nemascabile, NMI, nu pot fi dezactivate si au prioritate fata de cele mascabile, INTR.

26. Intreruperile interne

Intreruperile interne sunt evenimente sincrone si sunt raspunsuri ale procesorului la anumite evenimente detectate in timpul executiei unei instructiuni, intreruperile externe (mascabile si nemascabile) sunt evenimente asincrone. Deosebirea majora intre aceste doua tipuri de intreruperi este originea lor: o intrerupere interna este intotdeauna reproductibila prin reexecutia programului si datelor ce au cauzat intreruperea, in timp ce o intrerupere externa este, in general, independenta de executia curenta a taskului. Intreruperile interne sunt de doua tipuri. Un tip de intrerupere este denumit exceptie, deoarece intreruperea apare numai daca exista o anumita conditie de eroare, care nu permite executia corespunzatoare a instructiunii; celalalt tip de intrerupere genereaza intrerupere ori de cate ori instructiunea INTn este executata. Aceste instructiuni sunt utilizate fie in scopul de a testa rutinele utilizatorului pentru tratarea intreruperilor externe, fie in scopul de a apela rutine DOS. Pentru apelul rutinelor DOS se utilizeaza acest mecanism si nu mecanismul de apel de procedura din doua motive: fie nu se cunosc aceste adrese, fie ca ele se modifica de la o versiune la alta.

Exemple de exceptii sunt: eroare de impartire, depasire detectata de instructiunea INTO, depasire limite detectata de instructiunea BOUND, depasire segment (overrun), cod de operatie invalid, eroare de extensie de procesor etc. In modul protejat sunt detectate mult mai multe conditii de eroare, care rezulta intr-o intrerupere interna, in acest mod de adresare virtuala, tabela de vectori de intrerupere nu are adrese fizice fixe si deci nu poate fi adresata direct. De aceea, programele care, in modul real de adresare, manipuleaza direct tabela de vectori de intrerupere, nu vor lucra in modul protejat.

Celalalt tip de intrerupere genereaza intrerupere ori de cate ori instructiunea (INT?) este executata. Aceste intreruperi, instructiunile INT, sunt utilizate, de obicei, pentru testarea procedurilor de tratare a intreruperilor sau pentru a apela servicii DOS.

Intreruperile interne au urmatoarele caracteristici:

- codul intreruperii este continut in instructiune sau este predefinit;

- nu se executa cicluri de recunoastere intrerupere;

- nu pot fi dezactivate, cu exceptia intreruperii "single step';

- sunt prioritare fata de cele externe.

27. Intreruperile : ' single step (pas cu pas)' si 'breakpoint'.

Intreruperea single step. Aceasta intrerupere, de tipul 1, este generata in mod automat dupa executia fiecarei instructiuni, daca indicatorul TF este 1. Ea mai este denumita si exceptie de depanare deoarece permite executia unui program instructiune cu instructiune (adica "pas cu pas'). Procesorul salveaza in stiva registrul de indicatori si adresa urmatoarei instructiuni de executat si face indicatorii TF si IF zero, astfel ca la intrarea in procedura de tratare a intreruperii single step, procesorul nu mai este in modul pas cu pas; se evita astfel recursivitatea infinita. Procedura va permite vizualizarea programului intrerupt (registre, indicatori, variabile memorie etc.); la sfarsitul procedurii se vor reface indicatorii din stiva, astfel ca programul poate reveni in modul de executie pas cu pas. Procesorul nu dispune de instructiuni directe pentru modificarea acestui indicator (TF); el poate fi modificat numai prin modificarea imaginii sale din stiva (utilizand instructiunile PUSHF, POPF).

Intreruperea de breakpoint (suspendare). Aceasta instructiune, INT 3, este singura instructiune de intrerupere care are lungimea de un octet (toate celelalte ocupa cate doi octeti, primul fiind codul instructiunii, iar cel de-al doilea tipul intreruperii). Ea este folosita la implementarea de programe de depanare, deoarece necesita un singur octet de cod si poate substitui foarte usor orice octet de cod de instructiune. Ea permite in acest mod suspendarea programului si executarea rutinei de tratare a intreruperii de pe acest nivel.

Instructiunea permite in plus si inserarea de noi instructiuni in program, fara a fi recompilate sau reasamblate. Aceasta se poate face salvand primul octet de instructiune si inlocuindu-l cu instructiunea INT 3. Procedura de tratare a intreruperii de breakpoint va contine noile instructiuni, plus codul pentru refacerea octetului de instructiune salvat (inlocuit anterior de INT 3) si va decrementa adresa de revenire, salvata in stiva (mai exact IP) inainte de revenire, astfel ca instructiunea inlocuita sa fie executata dupa instructiunile inserate.

Metoda aceasta de depanare a unui program este mai complicata decat utilizarea registrelor de depanare, deoarece necesita crearea unui alias pentru segmentul de cod, salvarea octetului instructiunii originale, inlocuirea lui cu INT 3 si refacerea octetului la terminarea intreruperii.

28. Tabela vectorilor de intrerupere.

Aceasta tabela reprezinta legatura dintre codul intreruperii si procedura definita pentru a servi intreruperea asociata cu acel cod. Cativa dintre vectorii cei mai prioritari sunt rezervati de INTEL pentru functii dedicate. Utilizatorul nu poate folosi nici unul dintre primii 32 de vectori, in modul real, aceasta tabela ocupa 1 Koctet de memorie (pentru fiecare tip de intrerupere dintre cele 256 posibile este rezervat un pointer, adica un dublu cuvant) care contine adresa procedurilor de tratare a intreruperilor. Adresa este memorata astfel: cuvantul cel mai semnificativ contine adresa de baza a segmentului, iar cuvantul mai putin semnificativ contine deplasamentul; ele sunt memorate la adrese succesive in ordinea: cuvantul mai putin semnificativ (deplasamentul) si apoi cuvantul mai semnificativ (selectorul de segment).

|

Functia |

Numar intrerupere |

Instructiuni legate de intr. |

Returneaza adr. instr. exceptie |

|

exceptie eroare impartire |

DIV, IDIV | ||

|

intrerupere Single Step |

toate |

da |

|

|

intrerupere NMl |

toate | ||

|

intrerupere de breakpoint |

INT 3 | ||

|

exceptie depasire detectata de INTO |

INTO | ||

|

exceptie depasire domeniu instr. BOUND |

BOUND |

nu |

|

|

exceptie cod instr. invalid |

orice cod nedefinit |

da |

|

|

exceptie extensia procesor nu este |

ESC sau WAIT |

da |

|

|

disponibila |

LIDT |

da |

|

|

limita tabela intr. prea mica |

ESC |

da |

|

|

intr. depasire seg. extensie procesor |

toate instr. cu |

da |

|

|

exceptie depasire segment |

referire la mem |

da |

|

|

intr. eroare extensie procesor |

ESC sau WAIT | ||

|

intreruperi rezervate | |||

|

intreruperi def. de utilizator |

29. Structura procedurilor de tratare a intreruperilor.

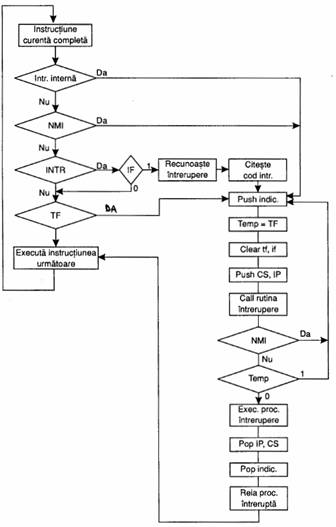

Procesorul serveste intreruperile numai intre sfarsitul unei instructiuni si inceputul urmatoarei. Daca se utilizeaza un prefix de repetare a unei instructiuni pe siruri, intreruperile si exceptiile pot aparea intre repetari. Cand o procedura de tratare a intreruperii este executata, indicatorii si registrele CS si IP sunt pusi in stiva, iar TF si IF sunt stersi.

Procedura poate reactiva semnalele de intrerupere externe cu instructiunea STI, permitand astfel sa fie intrerupta de o cerere, pe linia INTR, mai prioritara decat cea curent servita. Procedura de intrerupere poate fi totusi intrerupta de o cerere NMI, chiar daca sistemul de intreruperi nu este activat.

Ca orice procedura, procedurile de tratare a intreruperilor trebuie sa salveze registrele inainte de a le actualiza si sa le refaca inainte de terminare. De obicei, pe durata sectiunilor critice, adica cea de salvare si refacere a starii programului intrerupt, intreruperile sunt dezactivate urmand a fi reactivate dupa aceste sectiuni. Daca intreruperile sunt dezactivate un timp prea indelungat, intr-o procedura, cererile de intrerupere pe linia INTR pot fi pierdute.

Procedura de tratare a intreruperii se termina cu instructiunea l RET (Interrupt RETurn); se presupune ca stiva este adusa in aceleasi conditii ca la apelul procedurii. Procedurile de intrerupere software pot fi avantajoase in sisteme care realoca dinamic programe in timpul executiei. De exemplu, in figura se arata cum sunt prelucrate intreruperile simultane (eroare la impartire, intreruperea single step este activa si apare pe durata executiei instructiunii de impartire, cerere de intrerupere pe linia INTR).

30. Operatiile realizate de procesor la aparitia

unei intreruperi.

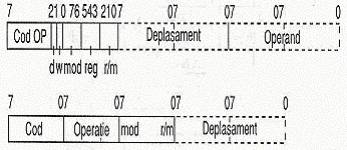

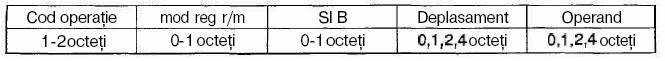

31. Formatul si dimensiunea instructiunilor.

31. Formatul si dimensiunea instructiunilor.

Instructiunile procesorului 80286 au o lungime variabila si pot avea de la 1 pana la 6 octeti.

Primul format - codul operatiei este reprezentat pe 1 octet

Al doilea format - codul operatiei este reprezentat pe 2 octeti

Semnificatia bitilor:

d - direction - specifica directia rezultatului operatiei

d = 0 r/m_r/m [Op] reg (registru)

1 reg_reg [Op] r/m (registru sau memorie)

w - word bit - indica tipul operanzilor:

w = 0, operand de tip octet;

w = 1, operand de tip cuvant (2 octeti)

mod - modul de lucru

= 11 - r/m se refera la un registru

= 00 - campul de

= 01 - deplasament de tip octet

= 10 - deplasamentul are 16 biti

32. Sursele (segment si offset) pe baza carora se calculeaza adresa fizica, in functie de modul de adresare (de tipul referintei).

Adresa fizica determinata de AU din adresa logica se calculeaza din surse diferite in functie de tipul referintei:

|

Tip referinta la memorie |

Segment de baza |

Offset |

|

|

Implicit |

Alternant |

||

|

Fetch instruct. |

CS |

IP |

|

|

Operatii stiva |

SS |

SP |

|

|

Variabile mem. |

DS |

CS, ES, DS |

Adr. Efect. |

|

Operatii siruri - sir sursa - sir destinatie |

DS ES |

CS, ES, SS |

SI DI |

|

BP utilizat ca registru baza |

SS |

CS, ES, SS |

Adr. Efect. |

Moduri de adresare (enumerare, exemple de instructiuni).

Exista in principal sase moduri de adresare:

- directa, adresa efectiva (AE) a operandului este reprezentata de deplasamentul continut in instructiune;

- indirecta, AE este intr-unul dintre registrele de baza sau index;

- bazata, AE este suma dintre deplasament si continutul unui registru de baza (BX sau BP);

- indexata, AE este suma dintre deplasament si continutul unui registru index (SI sau DI);

- bazata si indexata, AE este suma dintre continutul a doua registre: unul de baza si unul index;

- bazata si indexata cu deplasament, AE se obtine ca suma intre un registru de baza, un registru index si un deplasament;

Mai pot fi puse in evidenta si modurile de adresare:

- imediata, operandul este continut in instructiune;

- la registre, operandul se afla intr-un registru;

- adresarea sirurilor;

- adresarea porturilor de I/O.

Tipuri de prefixe.

Pentru adresarea intr-un alt segment decat cel implicit, se va preceda instructiunea respectiva cu un prefix de segment (override) care va specifica, in mod explicit, registrul segment utilizat. in ceea ce priveste formatul instructiunilor, la procesoarele 386/486 el este asemanator:

In plus fata de formatul anterior, poate fi prezent in instructiune octetul SIB (Scale * Index + Base), care specifica registrul index utilizat (acesta poate fi oricare dintre registrele EAX, 120 Programare in limbaj de asamblare EBX, ECX, EDX, EBP, ESI sau EDI, deci nu poate fi utilizat ca registru index ESP), factorul de scalare cu care se inmulteste registrul index (acesta poate avea una dintre valorile 1,2, 4, 8) si registrul de baza (oricare dintre registrele EAX EDI) utilizat pentru calculul adresei efective. Daca in cazul procesorului 286 o instructiune nu poate fi precedata decat de prefixe de segment (care specifica registrul de segment utilizat pentru determinarea adresei fizice) sau prefixe de instructiune (de repetare sau de blocare a accesului altui procesor la magistrala sa), instructiunile procesorului 386/486 pot fi precedate de urmatoarele prefixe (de cate un octet fiecare): [prefix instructiune [ prefix dimensiune adresa [ prefix dimensiune operand | prefix segment]

35. Identificatori in limbajul de asamblare (standard si definiti de utilizator).

Identificatorii sunt secvente de lungime 1-^31 caractere alfanumerice si speciale _ @ $. intr-un identificator nu este permis spatiul liber. Un identificator trebuie sa inceapa cu o litera sau cu unul dintre caracterele speciale. Daca identificatorul incepe cu punct (.), atunci el are semnificatia de comanda adresata asamblorului. Asamblorul nu deosebeste literele mari de cele mici. Identificatorii sunt si ei de doua tipuri: standard (sau predefiniti) si definiti de utilizator. Identificatorii standard, denumiti si cuvinte cheie, sunt folositi pentru denumirea unor functii si argumente stabilite la definirea limbajului si fac parte din vocabularul limbajului. Astfel de identificatori sunt:

- nume de instructiuni: MOV, ADD, SUB, INT etc.;

- nume de resurse: AX, BX,.., CS, DS,.., AH, AL etc.;

- nume de operatori: MOD, OFFSET, SEG, PTR, TYPE etc.;

- pseudoinstructiuni pentru asamblor: ASSUME, MODEL etc.

Identificatorii definiti de utilizator vor fi folositi pentru:

- nume de variabile, adrese de instructiuni, operanzi;

- nume de proceduri, segmente, macroinstructiuni.

36. Tipuri de constante si reprezentarea lor.

Constantele pot fi numerice sau siruri de caractere, formate pe baza anumitor reguli si carora li se asociaza o valoare. Constantele numerice pot fi: intregi, reale sau zecimale (codificate binar). Constantele intregi reprezinta numere intregi; ele pot fi utilizate, in functie de context, pentru: date, adrese sau operanzi imediati. Constantele pot fi reprezentate in binar, octal, zecimal sau hexazecimal; reprezentarea in una dintre aceste baze se specifica printr-una din literele B, Q, D sau H, care urmeaza constanta: -binar: 0110101OB; -octal: 152Q; -zecimal: 106D sau 106; - hexazecimal: 6aH; Pentru a evita confuzia intre constantele hexazecimale si identificatori, o constanta hexazecimala trebuie sa inceapa intotdeauna cu o cifra (de exemplu: OabcdH, pentru a nu fi confundata cu identificatorul abcdH). Constantele zecimale pot fi urmate sau nu de litera D, deoarece se considera implicit baza 10. Exista o directiva de asamblare care permite stabilirea reprezentarii intr-o baza implicita a constantelor: .RADIX < expresie > unde < expresie > trebuie sa aiba o valoare intreaga (2, 8,10 sau 16) si este evaluata in zecimal, lata de exemplu ce valori se incarca in registrul AX dupa utilizarea acestei directive (am folosit constante pentru expresia bazei): .RADIX 2

(AX) = 0004H mov AX,100;

.RADIX 8

mov AX,100;

.RADIX 10

mov AX,100;

.RADIX 16

mov AX,100; (AX) = 0100H

(AX) = 0040H

(AX) = 0064H

Constantele intregi pot fi reprezentate in memorie pe 8,16, 32 sau 64 de biti. Constantele reale sunt reprezentate in virgula mobila, prin mantisa si exponent, in general sub forma: [±] intreg, fractie [ E ± exponent ]

Asamblorul codifica aceste constante reale in reprezentarea cu virgula mobila pe 32, 64 sau 80 de biti, dupa tipul constantei:

dd (define double word), pe 32 de biti, real simpla precizie;

dq (define quadruple word), 64 de biti, real dubla precizie;

dt (define ten bytes), 80 de biti, real temporar;

Codificarea in virgula mobila difera de la un asamblor la altul, de la un compilator la altul, dar formatul cel mai raspandit este cel IEEE:

exponent mantisa

. Sm- semnul mantisei (1 bit);

. exponent- este exponentul numarului deplasat cu o anumita valoare, in functie de tipul reprezentarii:

7fH, pentru formatul pe 32 biti;

3ffH, pentru formatul pe 64 biti;

3fffH, pentru formatul pe 80 biti;

Exponentul pentru cele trei formate se reprezinta pe 8,11 si respectiv 15 biti;

. mantisa este normalizata, adica:

1.00O <= mantisa <=1.111

si se reprezinta, pentru cele trei formate,

pe 23, 52 si respectiv 64 de biti; de remarcat ca pentru primele doua formate

nu se reprezinta prima cifra, deci prima unitate din fata virgulei, care este presupusa

implicit, cu ajustarea corespunzatoare a exponentului. Pentru

cel de-al treilea format se reprezinta si prima unitate, cea din fata virgulei

(punctului zecimal). Exponentul din reprezentarea interna este deplasat (biased), pentru a simplifica operatiile de

comparare cu numere reale; in acest mod, procesorul lucreaza numai cu valori

pozitive pentru exponent. De exemplu, pentru valori reale in simpla precizie

(32 de biti), exponentul este in intervalul [1,254],

in loc de [-127, +126] cat arfi fost domeniul exponentului pentru o

reprezentare cu semn. Exponentul minim (0) este

utilizat doar pentru reprezentarea valorii 0.0 si pentru valori nenormalizate,

iar cel maxim (255) este utilizat pentru a reprezenta o conditie de eroare (

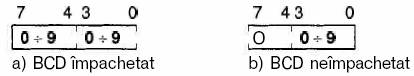

Valorile sunt memorate in ordinea inversa scrierii lor, adica la adresa cea mai mica, octetul cel mai putin semnificativ, iar la adresa cea mai mare (ultima), octetul cel mai semnificativ. Un alt tip de constante il reprezinta constantele zecimale codificate binar (BCD); ele pot fi de doua tipuri, si anume: - zecimal impachetat; - zecimal neimpachetat (denumit si format ASCII). Primul format se caracterizeaza prin faptul ca fiecare dintre cele doua tetrade ale unui octet contine o cifra zecimala, deci valoarea unui astfel de octet este cuprinsa in intervalul 0-99; cel de-al doilea format contine numai o singura cifra, pe tetrada mai putin semnificativa, cealalta fiind O, ca in reprezentarea urmatoare:

Aceste constante pot fi reprezentate si pe 80 de biti utilizand o declaratie de tipul:

dt

pentru care se pot introduce maxim 18 cifre, deoarece octetul cel mai semnificativ contine pe primul bit semnul numarului, restul acestui octet (7 biti) fiind nefolosit. Memorarea se face dupa aceeasi regula, adica incepand cu octetul cel mai putin semnificativ si terminand cu octetul cel mai semnificativ. Formatul zecimal neimpachetat mai este denumit si format ASCII, deoarece exista o corespondenta directa intre formatul BCD neimpachetat si cel ASCII (singura diferenta la acest format fata de cel BCD este ca prima tetrada contine valoarea 3, bineinteles, pentru cifre). Memorarea acestui numar se face, conform regulii cunoscute, incepand cu octetul cel mai putin semnificativ, la adresa adr si terminand cu octetul cel mai semnificativ, la adresa adr + 9.

De exemplu, pentru o declaratie de forma:

dt

reprezentarea interna va fi:

Constantele exprimate prin siruri de caractere constau dintr-o succesiune de caractere incluse intre apostrofuri ('Exemplu') sau intre ghilimele ('sir caractere'). Daca in interiorul unui sir de caractere, un subsir trebuie sa apara intre apostrofuri sau ghilimele, atunci aceste caractere se dubleaza: '1 Dec'1918'sau'1 Dec''1918'.

37. Tipuri de propozitii in limbaj de asamblare; sintaxa unei instructiuni.

O propozitie este o succesiune de cuvinte si caractere din alfabetul limbajului de asamblare, construita dupa anumite reguli sintactice, avand lungimea maxima de 128 de caractere si care poate fi:

- instructiune;

- pseudoinstructiune.

O instructiune reprezinta o propozitie care este tradusa in cod masina. O pseudoinstructiune este o propozitie care nu se traduce in cod masina, ea reprezentand o directiva pentru asamblor, pentru coordonarea modului de lucru al asamblorului:

- definiri de constante;

- rezervari de zone de memorie;

- controlul procesului de asamblare;

Instructiuni in limbaj de asamblare

Sintaxa generala a unei instructiuni este:

[ eticheta: ] [ mnemonica [ operanzi ] ] < comentarii > ]

unde eticheta - este un camp care contine un nume simbolic format din maximum 31 de caractere alfanumerice si caracterele speciale _, ?, @, $. Primul caracter este o litera sau un caracter special. Fiecare eticheta are asociata o valoare numerica ce reprezinta adresa relativa in cadrul segmentului (sau grupului de segmente) din care face parte; mnemonica- reprezinta numele instructiunii sau al pseudoinstructiunii; operanzi - este un camp a carui existenta si format depinde de tipul instructiunii. Daca instructiunea are doi operanzi, cei doi sunt denumiti destinatie si sursa; ei apar in instructiune in aceasta ordine. Operanzii pot fi si expresii care contin registre, constante, identificatori si operatori (aritmetici, de indexare, logici, de deplasare, relationali, de tip sau de conversie).

38. Declararea datelor in limbaj de asamblare, exemple.

Declararea datelor se realizeaza cu ajutorul unor pseudoinstructiuni care asigura: alocarea de memorie pentru date, specificarea tipului datelor si initializarea datelor. Datele pot fi specificate prin nume, expresii sau siruri de caractere, care se evalueaza in procesul de asamblare la constante. Operatia de alocare si initializare a datelor are loc in procesul de asamblare; datele sunt inscrise in fisierul obiect, de unde vor fi preluate la executie.

Sintaxa este urmatoarea:

[ nume_variabila ]tip[ lista_expresii ] [;comentarii]

sau

[ nume_variabila ]tip[numar] DUP ([ lista_expresii ])

unde

- nume_varibila este un identificator, construit dupa regulile specificate anterior;

- tip este mnemonica pseudoinstructiunii, care implicit specifica tipul datelor:

db - define byte; defineste date de tip octet intregi, cu sau fara semn;

dw - define word; cuvant de 16 biti ce defineste date intregi, cu sau fara semn;

dd - define double; dublu cuvant, de 32 de biti ce poate defini un pointer sau o valoare

intreaga sau reala, cu sau fara semn;

dq - define quadruple; cuvant de 64 biti ce poate defini o valoare reala sau intreaga;

df - define float; real pe 6 octeti;

dp - define pointer; referinta specifica pentru 386, reprezentata pe 6 octeti (segmentul

pe 2 octeti, iar deplasamentul pe 4 octeti);

dt - define ten bytes; data de 10 octeti de tip rea! sau zecimal impachetat;

nume_structura - numele unei structuri utilizate pentru definirea unor date cu aceasta

structura

. lista_expresii sunt expresii separate prin virgule, evaluate la constante, reprezentand

valorile cu care vor fi initializate datele definite.

Daca apare simbolul ?, inseamna ca datele respective nu se initializeaza. Constructia este

recursiva. Evaluarea expresiilor se face la asamblare.

. numar reprezinta o expresie ce reprezinta factorul de multiplicare al listei de expresii

care urmeaza dupa operatorul DUP.

Exemple:

adb -100 ; se pot defini valori in intervalul [-128, +127]

; sau [O, 255]

lit db 'abcde' ; se vor memora codurile ASCII ale caracterelor din

; lista: 61 h, 62h, 63h, 64h, 65h

aw dw -1000 ; domeniul de valori: [-32768, 32767] sau [O, 65535]

AB dw 'AB' ; va depune la adresa AB: 42h, 41 h

adrAB dw AB ; se va depune deplasamentul etichetei AB,

; stabilit la asamblare

off_AB dw offset AB ; deplasamentul etichetei AB, stabilit la localizare

seg_AB dw seg AB ; adresa segment de la localizare

rez dw ? ; continut nedefinit

v1 dd 1.0 ; valoare reala definita pe 32 biti

v2 dd 1A2B3C4Dh ; valoare intreaga pe 32 biti

adr_v1 dd v1 ; pointer pentru referirea lui v1

Pentru a multiplica definirea unor date se utilizeaza operatorul DUP, alaturi de db, dw etc.

Sintaxa este urmatoarea:

< numar > DUP (expresie pt. valoarea initiala)

in acest fel se defineste o structura formata dintr-un <numar> de elemente, iar un element

poate fi: expresie numerica, semnul ? daca nu se specifica valoarea initiala, o lista de

elemente sau alti operatori DUP.

Exemple:

db 100 dup (0) ; multiplicarea valorilor initiale

db2 dup (O, 3 dup (1)), 10, 25, 100)

dw 100 dup (5 dup (4), 7)

db 10 dup ('mesaj ', Odh, Oah)

39. Operatorii SEG, OFFSET, TYPE.

SEG < expresie >. Acest operator furnizeaza adresa de segment a unei adrese exprimata printr-o expresie, care poate fi: variabila, operand memorie, eticheta, numele unui segment sau numele unui grup de segmente.

Exemplu:

beta dw

mov bx, seg beta

mov ds,bx

OFFSET < expresie >. Operatorul furnizeaza deplasamentul in cadrul segmentului pentru o expresie de tip: variabila (simpla sau structurata), operand memorie, eticheta. Aplicat unei variabile sau etichete, operatorul furnizeaza deplasamentul variabilei sau etichetei. Valoarea este cunoscuta in momentul editarii legaturilor, cand se face alinierea finala a segmentului, deoarece deplasamentele de la asamblare se pot modifica la localizare, daca segmentul este combinat cu parti ale aceluiasi segment, definite in alte module sau daca nu este aliniat la un paragraf. Exemplu: el poate fi utilizat in adresarea indirecta a variabilelor

sir dw

mov bx, offset sir ; adresa de inceput a sirului

mov si, O ; se initializeaza indexul primului

; element din sir

add ax, [bx] [si] ; se insumeaza elementele

Daca se utilizeaza directiva group, operatorul OFFSET nu va returna deplasamentul unei variabile din grup, ci va returna deplasamentul variabilei din segmentul sau. Pentru a returna deplasamentul variabilei din grupul respectiv, trebuie utilizat prefixul grupului respectiv. Exemplu:

dgrup group datai, data2

datai segment

datai ends

data2 segment

val db

dw val; deplasamentul in cadrul segmentului ; furnizat de asamblor

dw dgrup:val ; deplasamentului in grup

Limbajul de asamblare

dd val; deplasamentul in segment + adresa, segment

dddr gup:val; deplasamentul grup + adresa segment

dataSends

mov bx, offset val; deplasamentul in segment

mov bx, offset grup:val; deplasamentul in grup

Observatie:

- offset [bx] este echivalent cu [bx]

- offset depl[bx] este echivalent cu [depl+bx]

TYPE < expresie >. Furnizeaza un numar intreg ce reprezinta tipul expresiei asupra careia se aplica; are un singur argument, care poate fi o variabila sau eticheta. Daca expresia este o variabila (simpla sau structurata) operatorul returneaza numarul de octeti pe care se reprezinta componentele variabilei simple sau numarul de octeti ai variabilei structurate. Valorile returnate de operator, in functie de tipul variabilei sunt: byte- 1;

word-

dword-

qword-

pword-

fword-

tbyte-

structura - numarul de octeti ai structurii;

Se utilizeaza, de obicei, in calcule asupra vectorilor sau structurilor, pentru a determina adresa urmatorului element. Daca argumentul este de tip eticheta, operatorul, in functie de tipul etichetei, returneaza valorile: near- ffffH;

far- fffeH;

Exemple:

var dw

mov bx, type var ; (BX) = 2

vectorddIO dup (?)

mov si, type vector ; (SI) = 4

num_BCD dt 13245768,

mov bx.type num_BCD; (BX) = 10

40. Operatorii LENGTH, SIZE si PTR.

LENGTH < expresie >. Acest operator furnizeaza o valoare intreaga ce reprezinta numarul de elemente ale unei variabile (declarata utilizand operatorul DUP). Daca variabila a fost declarata prin utilizarea operatorului DUP imbricat (unul inclus intr-altul), atunci operatorul LENGTH va returna o valoare asociata operatorului exterior. Daca variabila nu a fost declarata utilizand operatorul DUP, atunci operatorul LENGTH va returna valoarea 1. Exemple:

n1 db 50 dup (?);

n2 dw 150 dup (O, 1, ?);

n3 dd 200 dup (10, 20, 15 dup (?));

mes db1Exemplu de mesaj:';

length n1 = 50;

length n2 = 150;

length n3 = 200;

length raes = 1;

SIZE < expresie >. Furnizeaza o valoare ce reprezinta numarul de octeti ocupati de o

variabila si este in relatie cu LENGTH si TYPE prin identitatea:

SIZE = LENGTH * TYPE

Daca o variabila a fost declarata utilizand operatorul DUP imbricat, SIZE furnizeaza,

conform relatiei anterioare, numai valoarea operatorului DUP exterior. Pentru declaratiile

anterioare, acest operator va furniza urmatoarele valori:

size n1 = 50;

size n2 = 300;

size n3 = 800;

size mes = 1;

PTR < expresie >. Acest operator realizeaza conversia de tip pentru o variabila, operand din memorie sau eticheta, fie pentru a specifica tipul adresarii, fie pentru a permite adresarea unor date cu un alt tip decat cel cu care au fost declarate. Sintaxa acestui operator este: tip PTR < expresie > unde tip poate fi: BYTE, WORD, DWORD, QWORD, PWORD, FWORD, TBYTE sau nume de structura pentru operanzi din memorie si variabile, sau NEAR, FAR, PROC, unknown (lasa la latitudinea asamblorului determinarea tipului FAR sau NEAR utilizat) pentru etichete de instructiuni, nume de proceduri. De fapt, acest operator asociaza urmatoarele atribute expresiei: tip expresie

variabila sau eticheta

expresie numerica

atribute asociate

segment

SEG <expr>

nedefinit

offset

OFFSET <EXPR>

<expresie>

type

tip

tip

Exemple:

a) Explicitarea tipului referintei la memorie, pentru referinte anonime:

inc byte ptr [bx]

inc word ptr [si]

mov byte ptr [bx],99

mov word ptr [di],100

and word ptr [bp],100h

b) Specificarea tipului de salt (intersegment sau intrasegment):

jmp dword ptr [bx]

}mp near ptr etich ; pentru etich declarata in alt modul,

; daca aceasta eticheta este in acelasi segment sau grup

; de segmente cu instructiunea de salt

c) Referirea unor variabile cu un alt tip decat cel cu care au fost declarate:

aw dw OabcH, 12abH

ab db OaH, 12H

mov al, byte ptr aw

mov ax, word ptr ab

Limbajul de asamblare

d) Crearea unei variabile anonime la un offset dat dintr-un segment:

mov al,ds: byte ptr 5 ; refera octetul de la ds:5

mov bx,datai: word ptr 3000H ; refera cuvantul de la deplasamentul 3000H din

; segmentul datai

Aceste doua declaratii sunt echivalente cu urmatoarele doua:

mov al,ds:[5]

mov bx,datai:[3000]

41.Operatorii SHORT, WIDTH, MASK.

SHORT. Acest operator accepta un argument de tip eticheta (un offset adresabil prin registrul segment CS).Se utilizeaza in instructiuni de salt conditionat, neconditionat si in instructiuni de apel de procedura, cand codul tinta are un deplasament autorelativ de un octet cu semn (adica tinta saltului este in intervalul -128 ->127 fata de instructiunea de salt). In mod normal, instructiunea de salt va codifica deplasamentul la instructiunea tinta ca un numar intreg pe 16 biti. Utilizand acest operator, cu conditia ca tinta sa fie in intervalul [-128 127], asamblorul va codifica deplasamentul tintei pe un singur octet, reducand codul generat cu un octet:

jmp SHORT etich

De fapt asamblorul genereaza in mod automat un deplasament pe 8 biti, daca deplasamentul auto relativ al tintei este in intervalul [-128,+127], dar pt referinte externe va genera un deplasament pe 16 biti. Daca referinta este in intervalul mentionat, utilizand operatorul Short se va genera un deplasament de un octet, scurtand codul generat pt instructiunea de salt cu un octet.

WIDTH si MASK. Acesti operatori unt folositi pt a returna numarul de biti sau o masca de biti pt inregistrare, care reprezinta un tip de date structurat. Operatorul WIDTH returneaza numatul de biti ai unei inregistrari sau al unui camp al unei inregistrari, dupa cum argumentul sau este numele inregistrarii sau numele unui camp al inregistrarii. Operatorul MASK are ca argument numele unui camp al unei inregistrari si returneaza o masca de biti, definiti ca fiind 1 pt pozitiile campului respectiv si 0 pt celelalte pozitii. Exemplu:

model record A:3,B:1,C:4,D:5,E:3 ;reprezinta numerele asociate campurilor respective, impreuna cu numarul

; de biti pt fiecare camp

mov cx, mask C ; (CX)=000 0 1111 00000 000=0f00H

mov cl, width D ; (CL)=5, dimensiunea campului D

mov cl, C ;(CX)=8, pozitia campului C

42. Directivele ORG, EQU si simbolul contor program $.

Directiva EQU. Aceasta directiva permite asignarea unei valori la un simbol, in momentul asamblarii.

Sintaxa este:

<nume> EQU <expresie>

unde expresia poate fi:

Directiva ORG. Contorul de locatii poate fi initializat prin aceasta directiva cu o anumita valoare pozitiva astfel:

ORG <expresie>

unde expresia este evaluata modulo(64K) si nu poate contine referinte ulterioare. Nu poate fi asignata la o eticheta, adica o declaratie de forma: start: ORG 100 H, sua pentru date.

Simbolul contor program $ (contor locatie). Reprezinta adresa curenta a contorului de program, adica adresa relativa in cadrul segmentului curent al instructiunii sau a datelor de asamblat. La inceputul fiecarui segment, contorul de locatii este initializat la 0 si e actualizat de asamblor pe masura asamblarii programului. Exemple:

lista dw 11, 22, 33, 0aah

lung_lista equ ($ linie-lista)/2

mesaj db ' mesaj $ '

lung_mesaj equ $ - mesaj

43. Definirea completa a segmentelor.

Se utilizeaza o declaratie de forma:

nume_seg SEGMENT [tip_aliniere][tip_combinare][tip_utilizare][clasa_seg]

..<corpul segmentului> ;instructiuni sau date

nume_seg ENDS

unde nume_seg este numele asociat segmentului, care trebuie sa fie unic si caruia i se asociaza o adresa de segment (de 16 biti), corespunzatoare pozitiei in memoria segmentului, in faza de executie a programului.

Initializarea unui registru segment( DS,ES,SS) cu un segment declarat revine utilizatorului, care o va face in mod explicit in cadrul programului, utilizand pt aceasta numele segmentului respectiv:

mov ax,<nume_segment>

mov ds, ax ; in mod asemanator pt ES sau SS

44.Definirea simplificata a segmentelor.

.MODEL tip_model

Prin aceasta directiva se specifica dimensiunea si modul de dispunere a segmentelor in memoria RAM. Modelele de implementare, tip_model, sunt urmatoarele:

tiny - pt care LP + LD + LS < un segment (64K)

small - pt LP < un segment (64K), LD + LS < un segment

medium - pt LP > un segment (64K), LD + LS < un segment

compact - pt LP < un segment (64K), LD + LS > un segment

large - pt LP > un segment (64K), LD + LS >un segment

huge - la fel cu modelul anterior, cu diferenta ca referintele sunt normalizate.

Abrevierile utilizate sunt: LP, LD si LS; ele reprezinta lungimea programului (codului), dimensiunea memoriei pt date si respectiv pt stiva.

45.Simboluri predefinite utilizate in definirea simplificata a segmentelor.

Simboluri predefinite:

@CODE - numele segmentului de cod;

@DATA?, @DATA - numele segmentului de date (ne)initializate;

@FARDATA - numele segmentului de date initializate, de tip FAR;

@FARDATA?- numele segmentului de date neinitializate, FAR;

@CURSEG - numele segmentului curent executat; forma:

@curseg ends

conduce la inchiderea segmentului curent;

Aceste simboluri pot fi utilizate in directivele ASSUME, si la initializarea registrelor segment:

assume cs:@code, ds:@data

mov ax, @data

mov ds, ax

Alte simboluri predefinite:

@FILENAME; @CODESIZE; @DATASIZE

46.Asocierea segm cu registrele segm. Pseudoinstr. ASSUME.

Deoarece intr-un program pot exista mai multe segmente de diferite tipuri, asamblorul trebuie informat in leg cu cele 4 segm logice curente, lucru realizat cu pseudoinstr ASSUME:

ASSUME<reg_segment>:<segment>

<reg_segment> - unul din registrii CS,DS,ES sau SS; <segment> - numele unui segm/grup de segm ce va fi adresat de registrul segm respectiv sau de operatorul SEG si numele unei variabile/etichete din segm respectiv:

assume cs: code, ds: dgrup, es: SEG var_a, ss: SEG varf_stiva

Pt anularea asocierii: - una din formulele:

assume <reg_seg>: NOTHING ; anuleaza

; asocierea reg_seg la orice segm

assume NOTHING ; anuleaza asocierile facute,

; pt toate registrele

47.Initializarea registrelor segment.

Registrele CS:IP - initializate pt executie de sist de operare la incarcarea programului executabil in memorie a i ele sa contina adresa primei instr ce trebuie executata din program:

END [adresa_de _start]

<adresa_de_start> - expresie ce specifica prima instr executabila si care va initializa continutul registrului IP. Adresa de start este optionala (poate lipsi pt unele module de program ce cont date sau proceduri).

CS - initializat de SO, cu prima adresa de segment disponibila; IP - initializat cu deplasamentul primei instr executabile in cadrul segm. Pt SS:SP - initializare facuta de: - utilizator, dc se folosesc direcive complete de segmentare si nu se specifica tipul si clasa segm de stiva; - automat (SP - initializat cu dimens segm de stiva declarata in directiva .stack sau rezervata in declararea completa a segm de stiva). DS, ES etc - initializate explicit si intotdeauna de programator.

48. Prefix segment.Referinte anonime.

Dc o referinta la o variabila nu este acoperita de o directiva ASSUME, asamblorul poate fi informat explicit asupra registrului segment al variabilei prin codificarea unui prefix de segment de forma: reg_seg: instructiune (referinta) in fata variabilei respective. Initializarea e facuta de utilizator.

Dezavantaje: - e valabila doar pt o instructiune (prefixul de segment trebuie precizat pt fiecare referinta la o variabila)

- e foarte usor sa se greseasca pt ca se refera la un registru de segment si nu la un nume de segment.

Variabilele referite astfel: [bx], [bp], word ptr [si], byte ptr [di], [bx].camp, sunt denumite referinte anonime, pt ca nu este precizat numele variabilei din care sa se poata det segmentul caruia ii apartin. In astfel de situatii registrele de segment utilizate pt adresare sunt det in mod implicit pe baza unor reguli.

49.Reguli pt det registrului segment implicit.

Se refera la cazurile in care in instr. nu apar referiri explicite la registrele de segm sau nu apar nume de variabile din care sa reiasa registrul de segm care trebuie utilizat. Registrele de segm utilizate implicit sunt:

-pt registrele de baza: SS pt BP, DS pt. BX;

-pt.registrele index: DS pt ambele registre index (DI, SI). Dc instr. foloseste si un registru de baza si unul index, atunci se foloseste regula coresp. registrului de baza. Instr. care lucreaza cu stiva (push,pop,call,ret,int,iret) utilizeaza SS:SP si nu pot fi prefixate. Instr. pe siruri utilizeaza pt sirul destinatie registrul segm ES. Referintele anonime ce nu fol. registrul segm DS pt sirul sursa necesita specificarea explicita a reg. de segm utilizat si tipul operanzilor:

movs es:byte ptr [di],ss:[si]

movs word ptr es:[di],ss:[si]

50.Definirea si utilizarea grupurilor de segmente.

<nume_grup> GROUP <lista_nume_segmente>

<nume_grup> - numele grupului de segm pt det adresei de sgm utilizata pt referirea in cadrul grupului de sgm. Utilizat pt.: a initializa un registru de segment, intr-o pseudoinstr. ASSUME:

assume ds:dgrup

mov ax,dgrup

mov ds,ax

ca prefix de operand, pt a specifica utilizarea valorii de baza a grupului sau deplasamentul in cadrul acestuia:

mov ax,offset dgrup:var1 ; deplasamentul in grup

dd dgrup:var2 ; adresa in cadrul grupului

<lista_nume_segmente> - nume de segmente sau expresii de forma: SEG nume_variabila, SEG nume_eticheta

51. Setul de instructiuni; setul de instructiuni de baza.

Setul de instructiuni e impartit in 3 subseturi distincte: setul instructiunilor de baza, setul extins de instructiuni (instr pt I/O din proceduri, BOUND, I/O pe bloc), setul de instructiuni pentru controlul de sistem (controlul mecanismelor de administrare, protectia memoriei virtuale).

8086(88) instruct. de baza

80186 set extins de instruct.

80286 instruct. control sistem

80386 instruct. pe 32 biti

80486 instruct. in virgula mobila

PENTIUM instruct. MMX (date/64 biti)

Setul de instr.de baza: instr. de transfer de date, aritmetice, operare pe bit (logice,deplasare, rotire), operare pe siruri, transfer al controlului de program, pt controlul de procesor.

Instructiuni de conversie (extensie de semn).

Instructiuni de conversie (extensie de semn)

realizeaza extensia de semn a acumulatorului (AL, AX, EAX) in extensia sa (AH, DX sau EAX, EDX). Nu se modifica nici un indicator.

CBW (Convert Byte to Word)

CWDE (Convert Word to Double word Extended)

CWD (Convert Word to Double word)

CDQ (Convert Double word to Quad word)

La 386/486 transfer cu extensia bitului de semn sau de zerouri:

MOVSX <dest>,<sursa> (MOVe with Sign eXtension)

Destinatia poate fi un reg 16/32 biti, iar sursa reg/mem 8/16 biti.

MOVSX reg_16,reg/mem_8

MOVSX reg_32,reg/mem_8

MOVSX reg_32,reg/mem_16

Nu este afectat nici un indicator.

MOVZX <dest>,<sursa> (MOVe with Zero eXtension)

Instructiuni de transfer cu stiva. Accesul la datele (parametrii) din stiva, cu descarcarea sau fara descarcarea stivei.

Instructiuni de transfer cu stiva

- salvarea / refacerea adresei de revenire pentru apel/intreruperi; administrarea stivei pentru astfel de operatii este facuta, in mod automat, de catre procesor;

- salvarea / refacerea continutului unor resurse (registre, memorie etc.) la intrarea intr-o procedura, respectiv la iesirea din aceasta;

- pentru transferul parametrilor de intrare / iesire intre o procedura si programul apelant, precum si pentru alocarea dinamica de memorie.

PUSH <sursa> - depune in varful stivei <sursa>.

(SP) (SP) - 2

((SP)+1:(SP)) (sursa)